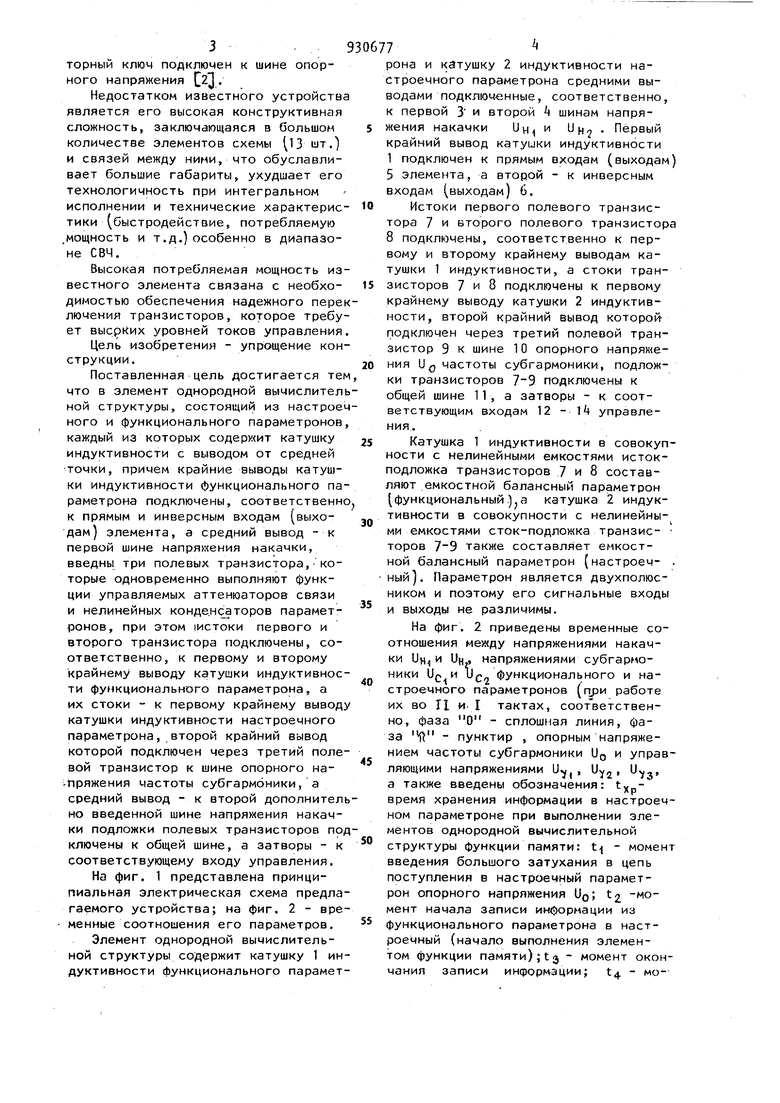

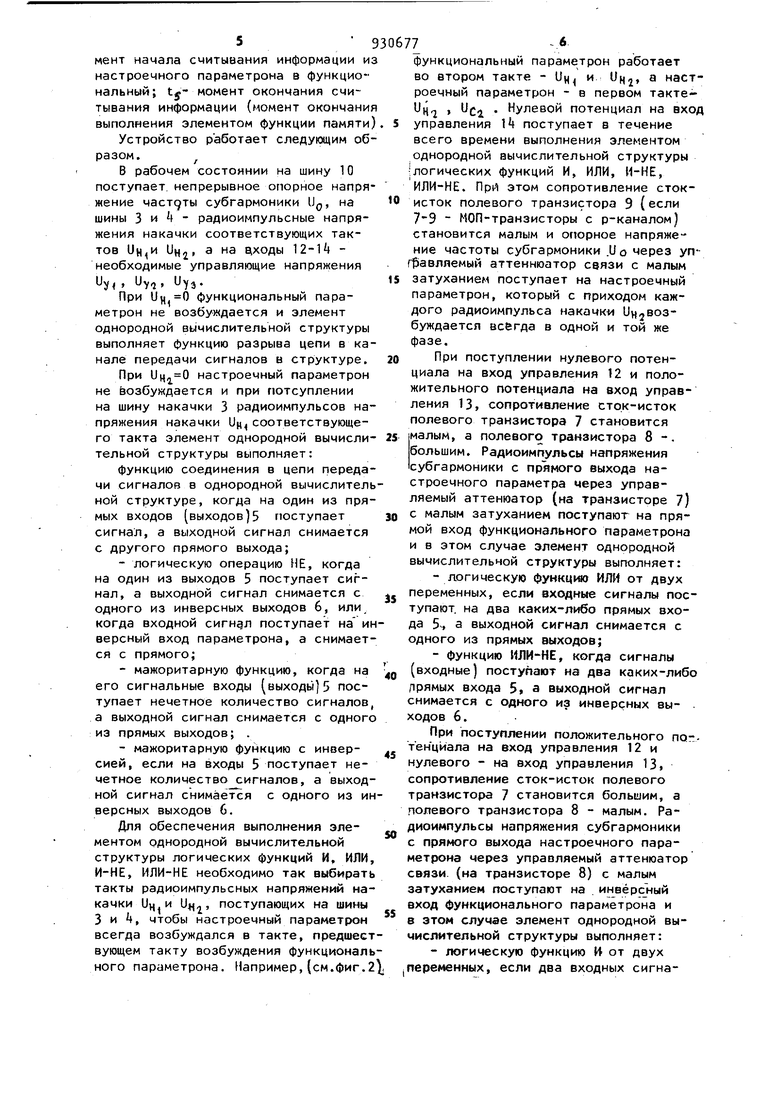

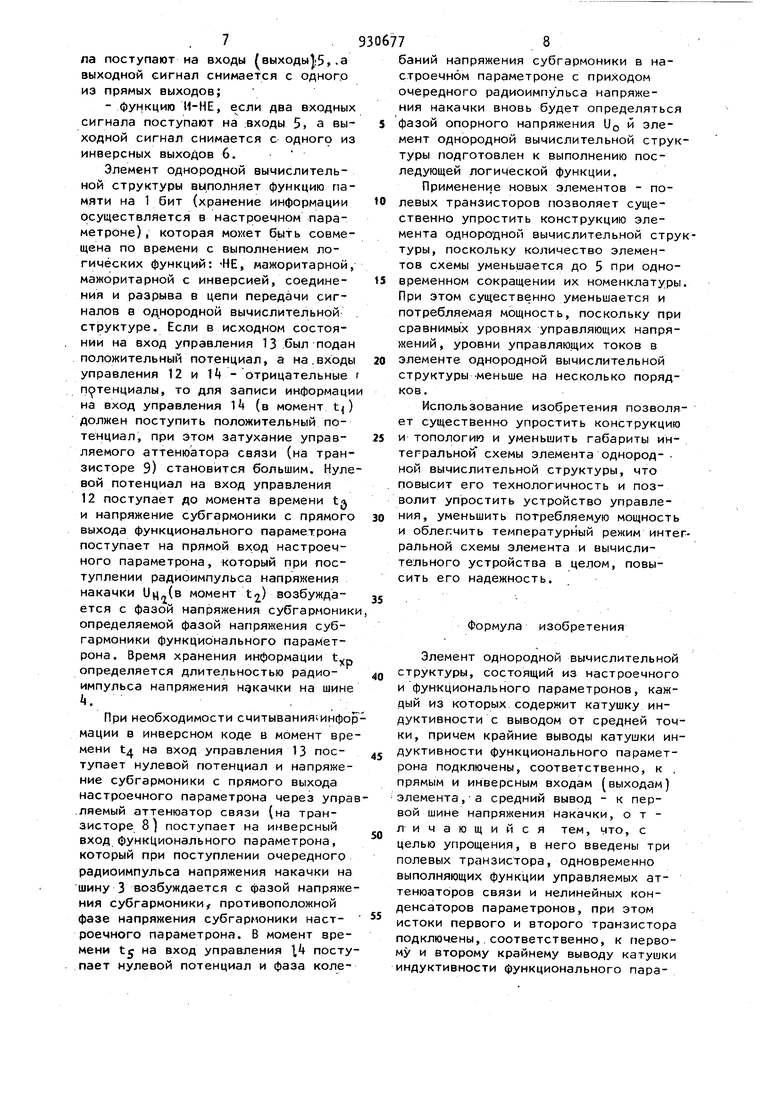

J Изобретение относится к областй вычислительной техники и высокочастотной автоматики и может быть испол зовано преимущественно при построении радиоимпульсных однородных вычислительных структур, предназначенных для обработки радиосигналов, носителем информации в которых является фаза высокочастотных колебаний. Известен элемент однородной вычис лительной структуры, предназначенный для обработки высокочастотных сигналов, состоящий из настроечной и функ циональной части, каждая из которых содержит катушки индуктивности и нелинейные конденсаторы f 1. Недостатком известного устройства является его высокая сложность. Известен элемент однородной вычислительной структуры, состоящий из настроечного и функционального параметронов, каждый из которых содержит катушку индуктивности, у которой вывод от средней точки подключен к шине напряжения накачки, а каждый крайний вывод подключен к коллектору транзистора, выполняюидего функции нел линейного конденсатора, при этом зы всех транзисторов подключены к общей, шине, эмиттеры транзисторов настроечного параметрона подключены к одной шине тактовых импульсов, а эмиттеры транзисторов функционального параметрона - к другой шине тактовых импульсов, кроме того, крайние выводы .катушки индуктивности функционального параметрона подключены соответственно, к прямым и инверсным входам (выходам) элемента, а крайние выводы катушки индуктивности настроечного параметрона через управляемые тpaнзиcтopнo-peзиcтoJ)ныe аттенюаторы связи подключены к одному из крайних выводов катушки индуктивности функционального параиетрона, один из крайних выводов катушки индуктивности настроем ного параметрона через управляемый транзисторный ключ подключен к шине опорного напряжения 2. Недостатком известного устройства является его высокая конструктивная сложность, заключающаяся в большом количестве элементов схемы (13 шт.) и связей между ними, что обуславливает большие габариты, ухудшает его технологичность при интегральном исполнении и технические характеристики (быстродействие, потребляемую .мощность и т.д.) особенно в диапазоне СВЧ. Высокая потребляемая мощность известного элемента связана с необходимостью обеспечения надежного перек лючения транзисторов, которое требует высоких уровней токов управления Цель изобретения - упрощение конструкции. Поставленная цель достигается тем что в элемент однородной вычислител ной структуры, состоящий из настроеч ного и функционального параметронов каждый из которых содерх(ит катушку индуктивности с выводом от средней точки, причем крайние выводы катушки индуктивности функционального параметрона подключены, соответственно к прямым и инверсным входам (выходам) элемента, а средний вывод - к первой шине напряжения накачки, введнь три полевых транзистора, которые одновременно выполняют функции управляемых аттенюаторов связи и нелинейных конденсаторов параметронов, при этом 1ИСТОКИ первого и второго транзистора подключены, соответственно, к первому и второму крайнему выводу катушки индуктивнос ти функционального параметрона, а их стоки - к первому крайнему вывод катушки индуктивности настроечного параметрона, второй крайний вывод которой подключен через третий поле вой транзистор к шине опорного на-пряжения частоты субгармоники, а средний вывод - к второй дополнител но введенной шине, напряжения накачки подложки полевых транзисторов по ключены к общей шине, а затворы - к соответствующему входу управления. На фиг. 1 представлена принципиальная электрическая схема предла гаемого устройства; на фиг. 2 - вре менные соотношения его параметров. Элемент однородной вычислительной структуры содержит катушку 1 ин дуктивности функционального парамет 7 рона и катушку 2 индуктивности настроечного параметрона средними выводами подключенные, соответственно, к первой 3 и второй 4 шинам напряжения накачки UH и U . Первый крайний вывод катушки индуктивности 1 подключен к прямым входам (выходам) 5 элемента, а второй - к инверсным входам (выходам) 6. Истоки первого полевого транзистора 7 и второго полевого транзистора 8 подключены, соответственно к первому и второму крайнему выводам катушки 1 индуктивности, а стоки транзисторов 7 и 8 подключены к первому крайнему выводу катушки 2 индуктивности, второй крайний вывод которой подключен через третий полевой транзистор 9 к шине 10 опорного напряк ения и частоты субгармоники, подложки транзисторов подключены к общей шине 11, а затворы - к соответствующим входам 12 - 14 управления. Катушка 1 индуктивности в совокупности с нелинейными емкостями истокподложка транзисторов 7 и 8 составляют .емкостной балансный параметром (функциональный .)jа катушка 2 индуктивности в совокупности с нелинейными емкостями сток-подложка транзис- торов также составляет емкостной балансный параметром (настроеч- . ный). Параметрон является двухполюсником и поэтому его сигнальные входы и выходы не различимы. На фиг. 2 приведены временные соотношения между напряжениями накачки UH, напряжениями субгармоНИКИ U{4 и 1)(л функционального и настроечного параметроноа (при работе их во Г1 и. I тактах, соответственно, фаза О - сплошная линия, фаза - пунктир , опорным напряжением частоты субгармоники UQ и управляющими напряжениями U , Uyj, Uy,, а также введены обозначения: t время хранения информации в настроечном параметроне при выполнении элементов однородной вычислительной структуры функции памяти: t - момент введения большого затухания в цепь поступления в настроечный параметром опорного напряжения UQ; 2 мо мент начала записи инс-юрмации из функционального параметрона в настроечный (начало выполнения элементом функции памяти)jtj - момент окончания записи информации; t - момент начала считывания информации из настроечного параметрона в функцио нальный; момент окончания считывания информации (момент окончания выполнения элементом функции памяти) Устройство работает следующим образом. В рабочем состоянии на шину 10 поступает, непрерывное опорное напряжение частдты субгармоники UQ, на шины 3 и if - радиоимпульсные напряжения накачки соответствующих тактов UHJ, а на щходы 12-U необходимые управляющие напряжения Uy,, UY,, Uyj. При UH,O функциональный параметрон не возбуждается и элемент однородной вычислительной структуры выполняет функцию разрыва цепи в канале передачи сигналов в структуре. При настроечный параметрон не возбуждается и при потсуплении на шину накачки 3 радиоимпульсов напряжения накачки J соответствующего такта элемент однородной вычислительной структуры выполняет: функцию соединения в цепи передачи сигналов в однородной вычислитель ной структуре, когда на один из прямых входов (выходов 5 поступает сигнал, а выходной сигнал снимается с другого прямого выхода; -логическую операцию НЕ, когда на один из выходов 5 поступает сигнал, а выходной сигнал снимается с одного из инверсных выходов 6, или когда входной сигнал поступает на ин версный вход параметрона, а снимается с прямого; -мажоритарную функцию, когда на его сигнальные входы (выходь| 5 поступает нечетное количество сигналов, а выходной сигнал снимается с одного из прямых выходов; . -мажоритарную функцию с инверсией, если на входы 5 поступает нечетное количество сигналов, а выходной сигнал снимается с одного из ин версных выходов 6. Для обеспечения выполнения элементом однородной вычислительной структуры логических функций И, ИЛИ, И-НЕ, ИЛИ-НЕ необходимо так выбирать такты радиоимпульсных напряжений накачки и U,, поступающих на шины 3 и 4, чтобы настроечный параметрон всегда возбуждался в такте, предшест вующем такту возбуждения функциональ ного параметрона. 11апример, (см.фиг.2 функциональный параметрон работает во втором такте - UH и , а настроечный параметрон - в первом такте HI Ci Нулевой потенциал на вход управления 1 поступает в течение всего времени выполнения элементом однородной вычислительной структуры Алогических функций И, ИЛИ, И-НЕ, ИЛИ-НЕ. При этом сопротивление стокисток полевого транзистора 9 (если - МОП-транзисторы с р-каналом) становится малым и опорное напряжение частоты субгармоники .Uo через упфавляемый аттеннюатор связи с малым затуханием поступает на настроечный параметрон, который с приходом каждого радиоимпульса накачк 1 UHJвозбуждается всегда в одной и той же фазе. При поступлении нулевого потенциала на вход управления 12 и положительного потенциала на вход управления 13, сопротивление сток-исток полевого транзистора 7 становится |малым, а полевого транзистора 8 -. большим. Радиоимпульсы напряжения 1субгармоники с прямого выхода настроечного параметра через управляемый аттенюатор (на транзисторе 7) с малым затуханием поступают на прямой вход функционального параметрона и в этом случае элемент однородной вычислительной структуры выполняет: -логическую функцмо ИЛИ от двух переменных, если входные сигналы поступают, на два каких-либо прямых входа 5, а выходной сигнал снимается с одного из прямых выходов; -функцию ИЛИ-НЕ, когда сигналы (входные) поступают на два каких-либо дрямых входа 5, а выходной сигнал снимается с одного из инверсных выходов 6. При поступлении положительного notтенцйала на вход управления 12 и нулевого - на вход управления 13, сопротивление сток-исток полевого транзистора 7 становится большим, а полевого транзистора 8 - малым. Радиоимпульсы напряжения субгармоники с прямого выхода настроечного параметрона через управляемый аттенюатор связи, (на транзисторе 8} с малым затуханием поступают на инвёрепный вход функционального параметрона и в этом случае элемент однородной вычислительной структуры выполняет: -логическую функцию И от двух переменных, если два входных сигнала поступают на входы выходы ;5, .а выходной сигнал снимается с одного из прямых выходов; - функцию И-НЕ, если два входных сигнала поступают на :входы 5, а выходной сигнал снимается с одного из инверсных выходов 6. Элемент однородной вычислительной структуры выполняет функцию памяти на 1 бит (хранение информации осуществляется в настроечном параметроне), которая быть совмещена по времени с выполнением логических функций: -НЕ, мажоритарной, мажоритарной с инверсией, соединения и разрыва в цепи передачи сигналов в однородной вычислительной структуре. Если в исходном состоянии на вход управления 13 был подан положительный потенциал, а на.входы управления 12 и Ш - отрицательные П(ртенциалы, то для записи информаци на вход управления 14 (в момент t) должен поступить положительный потенциал, при этом затухание управляемого аттенюатора связи (на транзисторе 9) становится большим. Нуле вой потенциал на вход управления 12 поступает до момента времени tg и напряжение субгармоники с прямого выхода функционального параметрона поступает на прямой вход настроечного параметрона, который при поступлении радиоимпульса напряжения накачки ицл(в момент 12) возбуждается с фазой напряжения субгармоник определяемой фазой напряжения субгармоники функционального параметрона. Время хранения информации typ определяется длительностью радиоимпульса напряжения ндкачки на шине k. При необходимости считывания инфо мации в инверсном коде в момент вре мени t на вход управления 13 поступает нулевой потенциал и напряжение субгармоники с прямого выхода настроечного параметрона через упра .ляемый аттенюатор связи (на транзисторе 8 поступает на инверсный вход функционального параметрона, который при поступлении очередного радиоимпульса напряжения накачки на шину 3 возбуждается с фазой напряже ния субгармоники противоположной фазе напряжения субгармоники настроечного параметрона. В момент времени t5 на вход управления 1, посту пает нулевой потенциал и фаза колебаний напряжения субгармоники в настроечном параметроне с приходом очередного радиоимпульса напряжения накачки вновь будет определяться фазой опорного напряжения UQ и элемент однородной вычислительной структуры подготовлен к выполнению последующей логической функции. Применение новых элементов - полевых транзисторов позволяет существенно упростить конструкцию элемента однородной вычислительной структуры, поскольку количество элементов схемы уменьшается до 5 при одновременном сокращении их номенклатуры. При этом существенно уменьшается и потребляемая мощность, поскольку при сравнимых уровнях управляющих напряжений , уровни управляющих токов в элементе однородной вычислительной структуры -меньше на несколько порядков. Использование изобретения позволяет сущестйенно упростить конструкцию и топологию и уменьшить габариты интегральной схемы элемента однород- ной вычислительной структуры, что повысит его технологичность и позволит упростить устройство управления, уменьшить потребляемую мощность и облегчить температурный режим интегральной схемы элемента и вычислительного устройства в целом, повысить его надежность. Формула изобретения Элемент однородной вычислительной структуры, состоящий из настроечного и функционального параметронов, каждый из которых содержит катушку индуктивности с выводом от средней точки, причем крайние выводы катушки индуктивности функционального параметрона подключены, соответственно, к , прямым и инверсным входам (выходам) элемента,а средний вывод - к первой шине напряжения накачки, отличающийся тем, что, с целью упрощения, в него введены три полевых транзистора, одновременно выполняющих функции управляемых аттенюаторов связи и нелинейных конденсаторов параметронов, при этом истоки первого и второго транзистора подключены,.соответственно, к первому и второму крайнему выводу катушки индуктивности функционального парапервому крайметрона, а их стоки - к нему выводу катушки индуктивности настроечного параметрона, второй крайний вывод которой подключен через третий полевой транзистор к шине опорного напряжения частоты субгармоники, а средний вывод - к второй дополнительно введенной шине напряжения накачки, подлоиски поле93вых транзисторов подключены к общей шине, а затворы - к соответствующему входу управления. Источники инфбрмации, принятые во внимание при экс 1ертизе t,Авторское: свидетельство СССР Г 32679, кл. Н 03 К 19/00, 1972. 2. Авторское свидетельство СССР по заявке If 2753972, 16,01.79.

| название | год | авторы | номер документа |

|---|---|---|---|

| Элемент однородной вычислительнойСТРуКТуРы | 1979 |

|

SU813786A1 |

| ЭЛЕМЕНТ ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙСТРУКТУРЫ | 1972 |

|

SU432679A1 |

| Элемент однородной вычислительной структуры | 1984 |

|

SU1211890A1 |

| ЭЛЕМЕНТ ОДНОРОДНОЙ ВЫЧИСЛИТЕЛЬНОЙСТРУКТУРЫ | 1972 |

|

SU415808A1 |

| Параметрический генератор | 1987 |

|

SU1518866A1 |

| Устройство для измерения фазы радиосигнала | 1979 |

|

SU976505A1 |

| Делитель частоты | 1987 |

|

SU1580520A1 |

| Элемент однородной вычислительной структуры | 1978 |

|

SU733107A1 |

| Приемник фазоманипулированных сигналов | 1986 |

|

SU1363524A1 |

| Цифровой фазометр | 1982 |

|

SU1061062A1 |

Авторы

Даты

1982-05-23—Публикация

1980-06-16—Подача