(54) УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ-ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ

вторые входы соответственно второго и третьего, четвертого и пятого, шестого и седьмого вычислительных модулей объединены между собой.

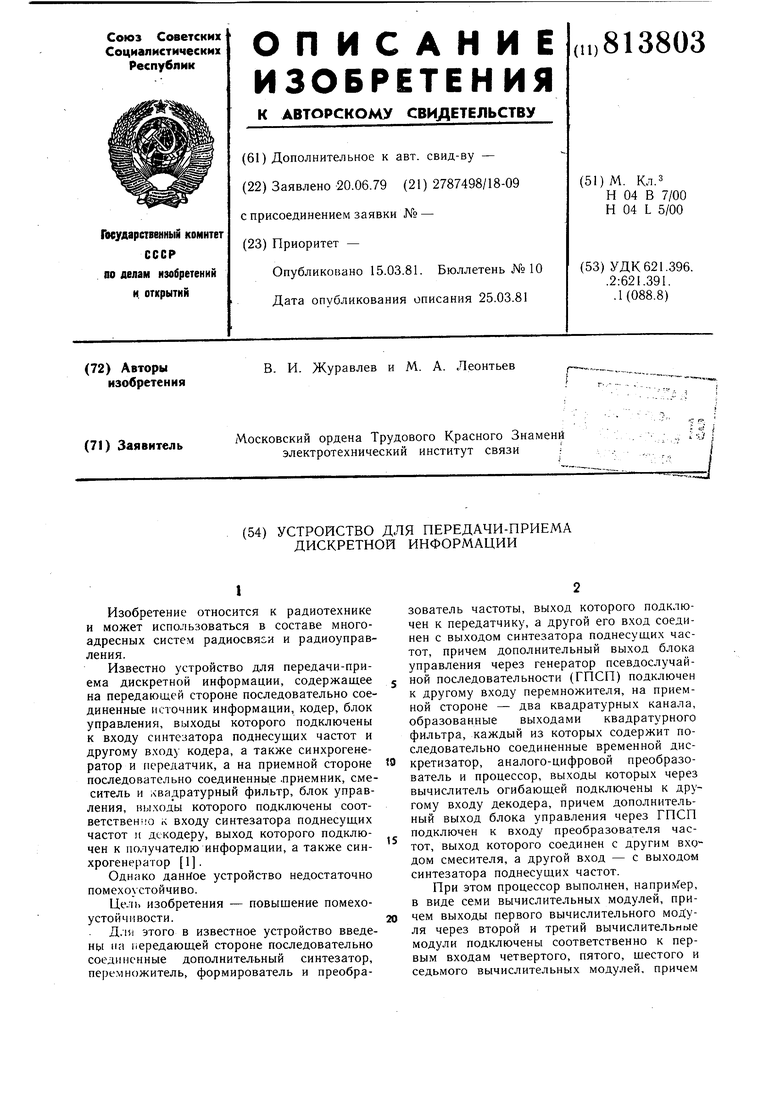

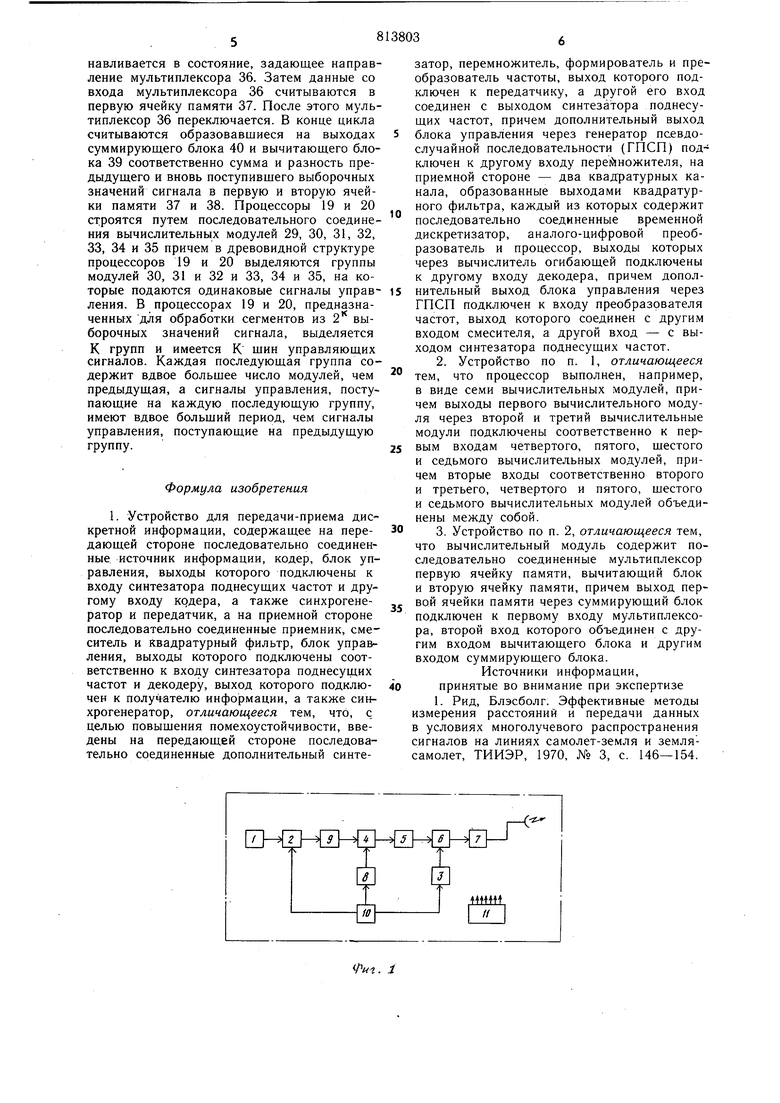

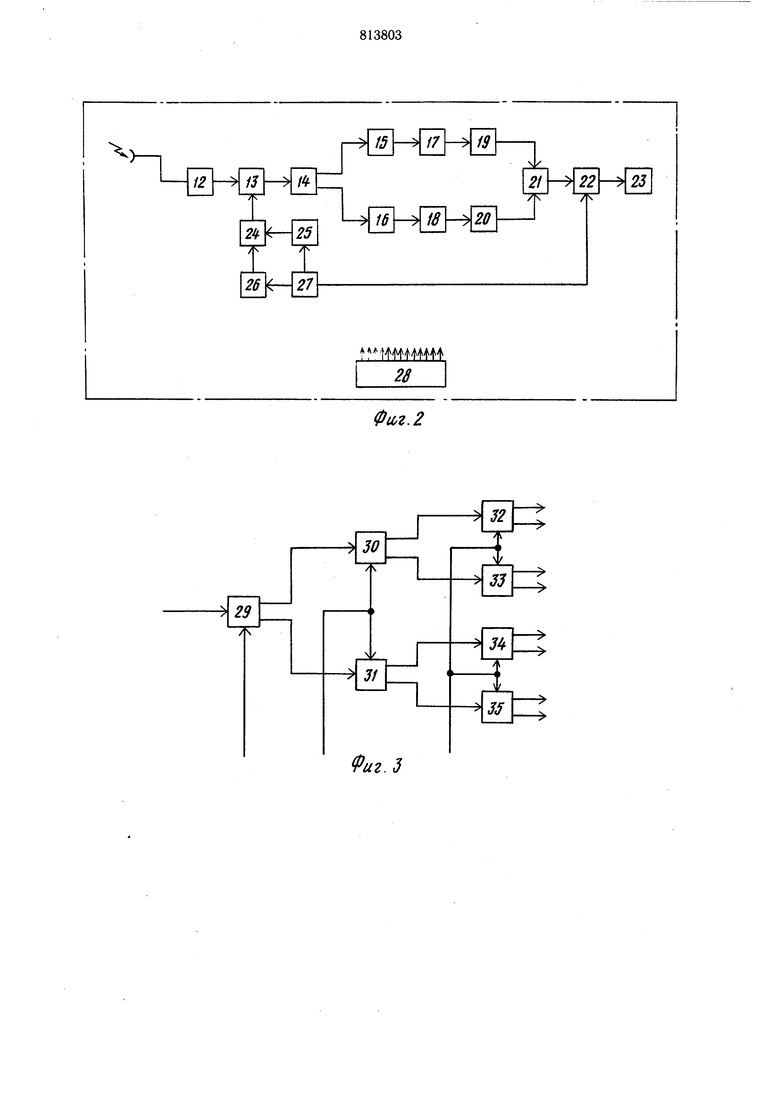

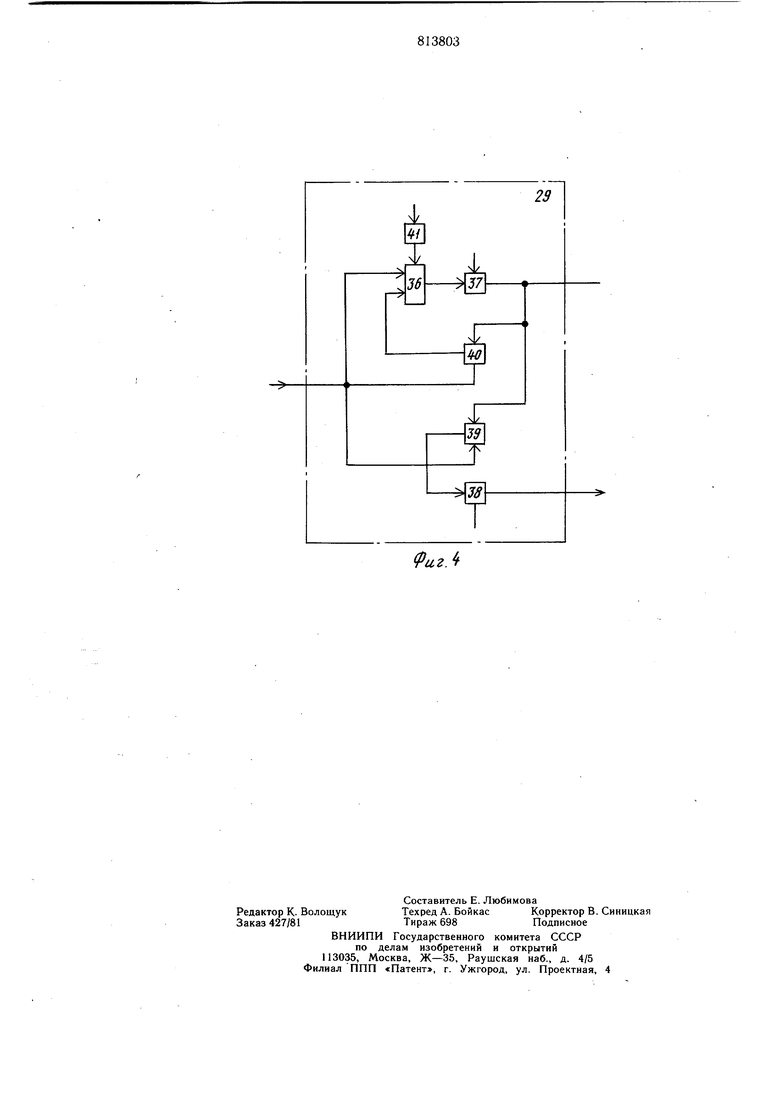

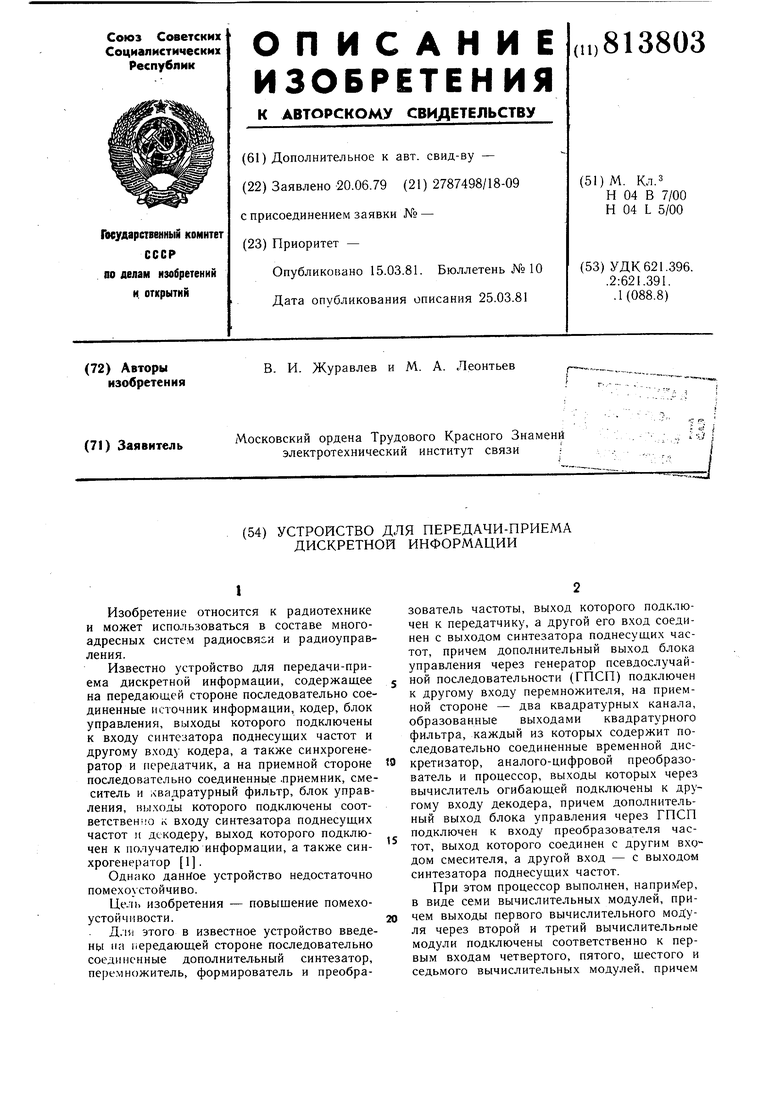

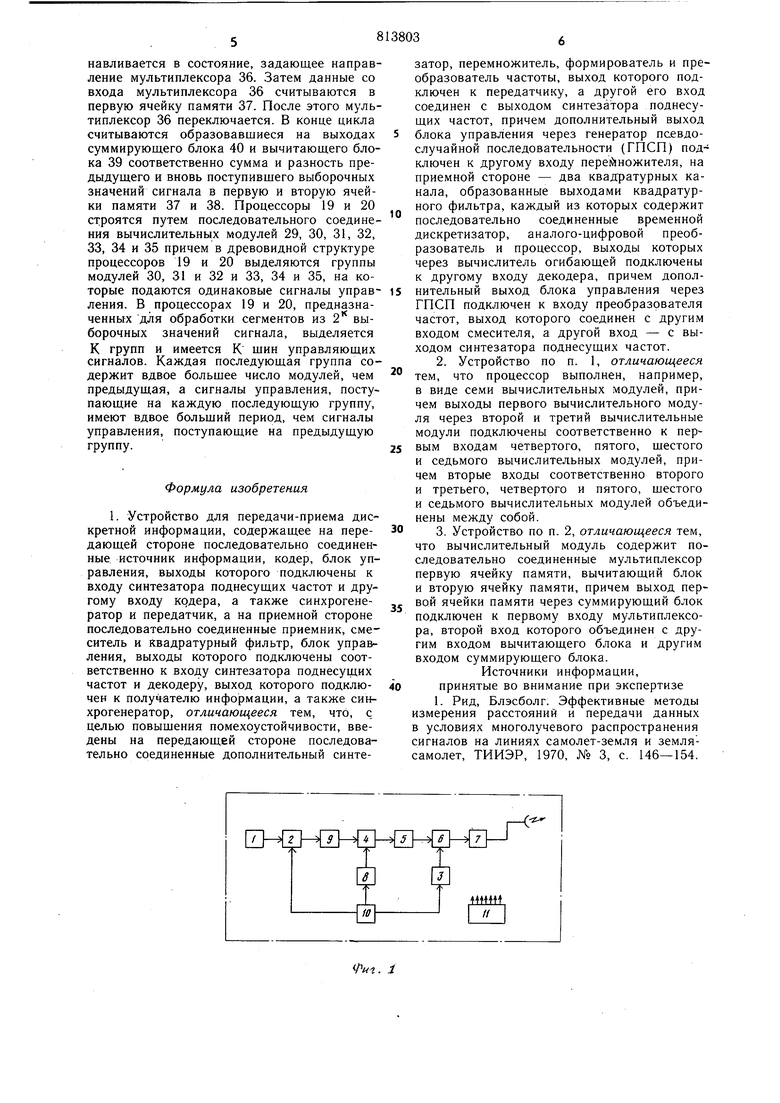

Причем вычислительный модуль содержит последовательно соединенные мультиплексор, первую ячейку памяти, вычитающий блок и вторую ячейку памяти, причем выход первой ячейки памяти через суммирующий блок подключен к первому входу мультиплексора, второй вход которого объединен с другим входом вычитающего блока и другим входом суммирующего блока. На фиг. 1 представлена структурная электрическая схема передающей части предлагаемого устройства; на фиг. 2 - то же, приемной части устройства; на фиг. 3 - то же, процессора; на фиг. 4 - то же, вычислительного модуля.

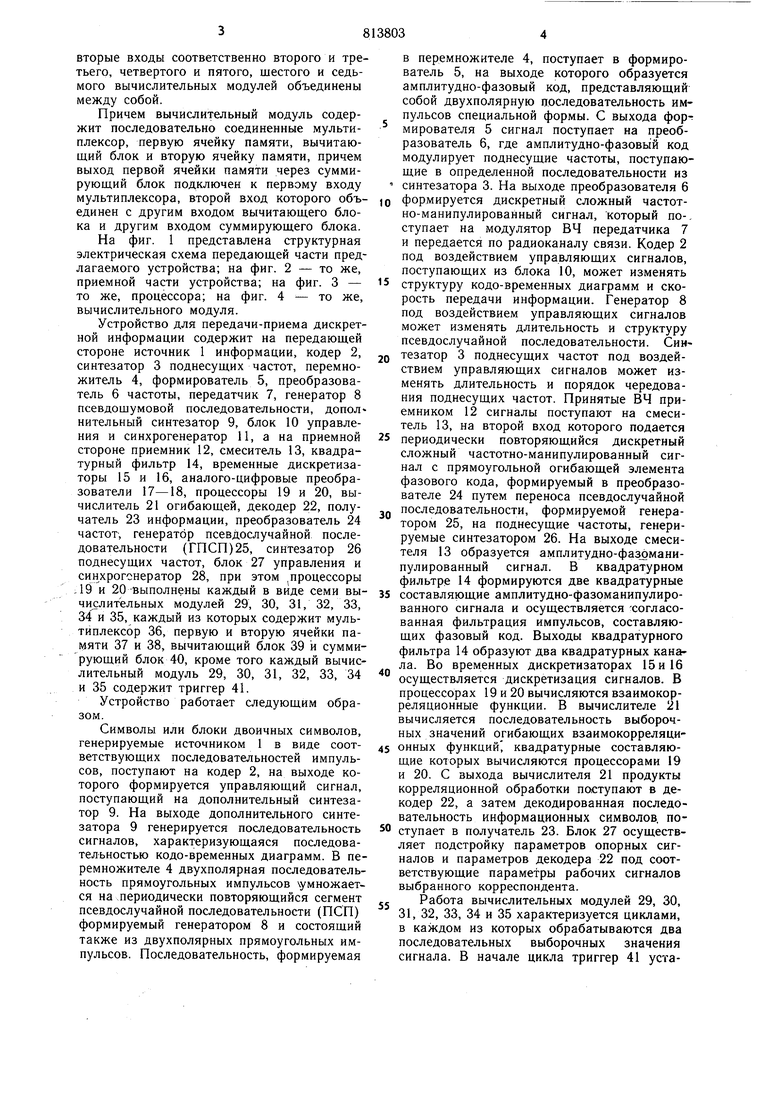

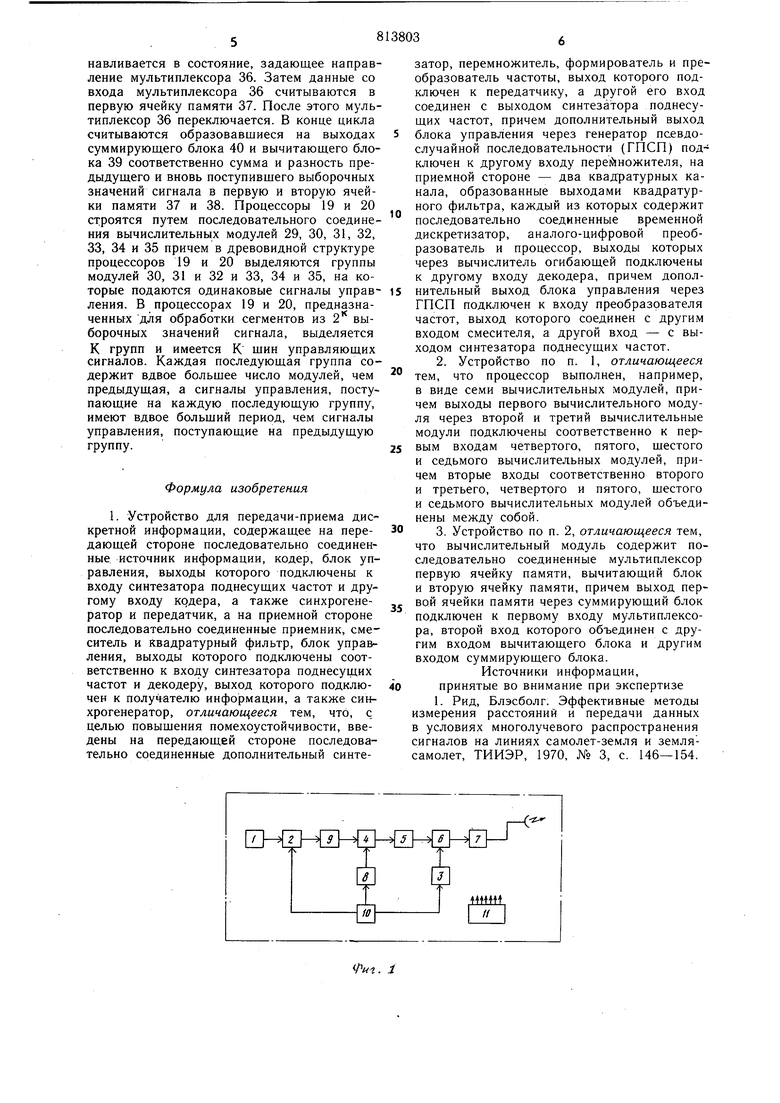

Устройство для передачи-приема дискретной информации содержит на передающей стороне источник 1 информации, кодер 2, синтезатор 3 поднесущих частот, перемножитель 4, формирователь 5, преобразователь 6 частоты, передатчик 7, генератор 8 псевдошумовой последовательности, допол нительный синтезатор 9, блок 10 управления и синхрогенератор 11, а на приемной стороне приемник 12, смеситель 13, квадратурный фильтр 14, временные дискретизаторы 15 и 16, аналого-цифровые преобразователи 17-18, процессоры 19 и 20, вычислитель 21 огибающей, декодер 22, получатель 23 информации, преобразователь 24 частот, генератор псевдослучайной последовательности (ГПСП)25, синтезатор 26 поднесущих частот, блок 27 управления и синхрогенератор 28, при этом процессоры ,19 и 20-выполнены каждый в виде семи вычи лительных модулей 29, 30, 31, 32, 33, 34 и 35, каждый из которых содержит мультиплексор 36, первую и вторую ячейки памяти 37 и 38, вычитающий блок 39 и суммирующий блок 40, кроме того каждый вычислительный модуль 29, 30, 31, 32, 33, 34 и 35 содержит триггер 41.

Устройство работает следующим образом.

Символы или блоки двоичных символов, генерируемые источником 1 в виде соответствующих последовательностей импульсов, поступают на кодер 2, на выходе которого формируется управляющий сигнал, поступающий на дополнительный синтезатор 9. На выходе дополнительного синтезатора 9 генерируется последовательность сигналов, характеризующаяся последовательностью кодо-временных диаграмм. В перемножителе 4 двухполярная последовательность прямоугольных импульсов умножается на чПериодически повторяющийся сегмент псевдослучайной последовательности (ПСП) формируемый генератором 8 и состоящий также из двухполярных прямоугольных импульсов. Последовательность, формируемая

в перемножителе 4, поступает в формирователь 5, на выходе которого образуется амплитудно-фазовый код, представляющий собой двухполярную последовательность импульсов специальной формы. С выхода формирователя 5 сигнал поступает на преобразователь 6, где амплитудно-фазовь1Й код модулирует поднесущие частоты, поступающие в определенной последовательности из синтезатора 3. На выходе преобразователя 6

0 формируется дискретный сложный частотно-манипулированный сигнал, который по-, ступает на модулятор ВЧ передатчика 7 и передается по радиоканалу Связи. Кодер 2 под воздействием управляющих сигналов, поступающих из блока 10, может изменять

структуру кодо-временных диаграмм и скорость передачи информации. Генератор 8 под воздействием управляющих сигналов может изменять длительность и структуру псевдослучайной последовательности. СинQ тезатор 3 поднесущих частот под воздействием управляющих сигналов может изменять длительность и порядок чередования поднесущих частот. Принятые ВЧ приемником 12 сигналы поступают на смеситель 13, на второй вход которого подается

5 периодически повторяющийся дискретный сложный частотно-манипулированный сигнал с прямоугольной огибающей элемента фазового кода, формируемый в преобразователе 24 путем переноса псевдослучайной

JJ последовательности, формируемой генератором 25, на поднесущие частоты, генерируемые синтезатором 26. На выходе смесителя 13 образуется амплитудно-фаз оманипулированный сигнал. В квадратурном фильтре 14 формируются две квадратурные

5 составляющие амплитудно-фазоманипулированного сигнала и осуществляется согласованная фильтрация импульсов, составляющих фазовый код. Выходы квадратурного фильтра 14 образуют два квадратурных канала. Во временных дискретизаторах 15 и 16 осуществляется дискретизация сигналов. В процессорах 19 и 20 вычисляются взаимокорреляционные функции. В вычислителе 21 вычисляется последовательность выборочных значений огибающих взаимокорреляци5 онных функций квадратурные составляющие которых вычисляются процессорами 19 и 20. С выхода вычислителя 21 продукты корреляционной обработки поступают в декодер 22, а затем декодированная последовательность информационных символов, поступает в получатель 23. Блок 27 осуществляет подстройку параметров опорных сигналов и параметров декодера 22 под соответствующие параметры рабочих сигналов выбранного корреспондента.

, Работа вычислительных модулей 29, 30, 31, 32, 33, 34 и 35 характеризуется циклами, в каждом из которых обрабатываются два последовательных выборочных значения сигнала. В начале цикла триггер 41 устанавливается в состояние, задающее направление мультиплексора 36. Затем данные со входа мультиплексора 36 считываются в первую ячейку памяти 37. После этого мультиплексор 36 переключается. В конце цикла считываются образовавшиеся на выходах суммирующего блока 40 и вычитающего блока 39 соответственно сумма и разность предыдущего и вновь поступившего выборочных значений сигнала в первую и вторую ячейки памяти 37 и 38. Процессоры 19 и 20 строятся путем последовательного соединения вычислительных модулей 29, 30, 31, 32, 33, 34 и 35 причем в древовидной структуре процессоров 19 и 20 выделяются группы модулей 30, 31 и 32 и 33, 34 и 35, на которые подаются одинаковые сигналы управления. В процессорах 19 и 20, предназначенных для обработки сегментов из 2 выборочных значений сигнала, выделяется

К групп и имеется К щин управляющих сигналов. Каждая последующая группа содержит вдвое большее число модулей, чем предыдущая, а сигналы управления, поступающие на каждую последующую группу, имеют вдвое больший период, чем сигналы управления, поступающие на предыдущую группу.

Формула изобретения

1. Устройство для передачи-приема дискретной информации, содержащее на передающей стороне последовательно соединенные источник информации, кодер, блок управления, выходы которого подключены к входу синтезатора поднесущих частот и другому входу кодера, а также синхрогенератор и передатчик, а на приемной стороне последовательно соединенные приемник, смеситель и квадратурный фильтр, блок управления, выходы которого подключены соответственно к входу синтезатора поднесущих частот и декодеру, выход которого подключен к получателю информации, а также синхрогенератор, отличающееся тем, что, с целью повышения помехоустойчивости, введены на передающей стороне последовательно соединенные дополнительный синтеГГ1- 7 - Пзатор, перемножитель, формирователь и преобразователь частоты, выход которого подключен к передатчику, а другой его вход соединен с выходом синтезатора поднесущих частот, причем дополнительный выход блока управления через генератор псевдослучайной последовательности (ГПСП) подключен к другому входу перейножителя, на приемной стороне - два квадратурных канала, образованные выходами квадратурного фильтра, каждый из которых содержит последовательно соединенные временной дискретизатор, аналого-цифровой преобразователь и процессор, выходы которых через вычислитель огибающей подключены к другому входу декодера, причем дополнительный выход блока управления через ГПСП подключен к входу преобразователя частот, выход которого соединен с другим входом смесителя, а другой вход - с выходом синтезатора поднесущих частот.

2.Устройство по п. 1, отличающееся тем, что процессор выполнен, например, в виде семи вычислительных модулей, причем выходы первого вычислительного модуля через второй и третий вычислительные модули подключены соответственно к первым входам четвертого, пятого, шестого и седьмого вычислительных модулей, причем вторые входы соответственно второго и третьего, четвертого и пятого, шестого и седьмого вычислительных модулей объединены между собой.

3.Устройство по п. 2, отличающееся тем, что вычислительный модуль содержит последовательно соединенные мультиплексор первую ячейку памяти, вычитающий блок и вторую ячейку памяти, причем выход первой ячейки памяти через суммирующий блок подключен к первому входу мультиплексора, второй вход которого объединен с другим входом вычитающего блока и другим входом суммирующего блока.

Источники информации, принятые во внимание при экспертизе

1. Рид, Блэсболг. Эффективные методы измерения расстояний и передачи данных в условиях многолучевого распространения сигналов на линиях самолет-земля и землясамолет, ТИИЭР, 1970, № 3, с. 146-154.

v.

t tWMHH

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство формирования и обработки широкополосных сигналов | 2018 |

|

RU2691733C1 |

| СИСТЕМА СВЯЗИ НАЗЕМНОГО ПУНКТА УПРАВЛЕНИЯ С БЕСПИЛОТНЫМ ЛЕТАТЕЛЬНЫМ АППАРАТОМ | 2024 |

|

RU2825035C1 |

| ЦИФРОВОЙ МОДЕМ КОМАНДНОЙ РАДИОЛИНИИ ЦМ КРЛ | 2013 |

|

RU2548173C2 |

| МНОГОКАНАЛЬНАЯ ЦИФРОВАЯ СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ | 1990 |

|

RU2013012C1 |

| АДАПТИВНОЕ УСТРОЙСТВО ПЕРЕДАЧИ ДАННЫХ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2008 |

|

RU2356171C1 |

| АБОНЕНТСКИЙ БЛОК ДЛЯ БЕСПРОВОДНОЙ ЦИФРОВОЙ ТЕЛЕФОННОЙ СИСТЕМЫ | 1988 |

|

RU2231222C2 |

| УСТРОЙСТВО ПРИЕМА И ПЕРЕДАЧИ OFDM-СИГНАЛОВ С ПОВЫШЕННОЙ ПОМЕХОУСТОЙЧИВОСТЬЮ | 2010 |

|

RU2423002C1 |

| Широкополосное приемопередающее устройство | 2016 |

|

RU2628328C1 |

| Широкополосное приемопередающее устройство с программной перестройкой рабочей частоты | 2016 |

|

RU2631464C1 |

| ШИРОКОПОЛОСНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО | 2005 |

|

RU2296420C1 |

.г

fe.J

Авторы

Даты

1981-03-15—Публикация

1979-06-20—Подача