(54) КОММУТАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| СЕТЬ ДЛЯ МАРШРУТИЗАЦИИ СООБЩЕНИЙ | 1996 |

|

RU2115162C1 |

| Коммутационное устройство | 1988 |

|

SU1539790A1 |

| Многоканальный матричный коммутатор | 1981 |

|

SU964690A1 |

| Информационно-управляющая система центрального теплового пункта жилых общественных и промышленных зданий | 1987 |

|

SU1511751A1 |

| Устройство межмашинной связи | 1987 |

|

SU1474666A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| СПОСОБ ВЫРАБОТКИ НАВИГАЦИОННО-ПИЛОТАЖНОЙ ИНФОРМАЦИИ ДЛЯ СУДОВ И ОТВЕТЧИК | 1993 |

|

RU2075763C1 |

| СТАНЦИЯ СВЯЗИ С АДАПТИВНОЙ КОММУТАЦИЕЙ КАНАЛОВ | 2015 |

|

RU2594758C1 |

| Устройство для поиска информации в ассоциативной памяти | 1988 |

|

SU1617460A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ ОБСЛУЖИВАНИЯ ЗАПРОСОВ | 2000 |

|

RU2157561C1 |

1

Изобретение относится к коммутационной технике.

Известны, коммутаторы, содержащие передатчики, приемники и матрицу коммутации 1.

Недостатком известного устройства яъляется низкое быстродействие.

Наиболее близким техническим решением к предлагаемому является коммутатор, содержащий М передатчиков и N приемников, а также матрицу из M-N узлов, в каждом из которых расположен элемент И коммутации, при этом первые входы элементов И коммутации каждого столбца матрицы объединены и подключены к информационному выходу соответствующего передатчика, а выходы элементов И коммутации каждой строки матрицы объединены и подключены ко входу соответствующего приемника 2.

Недостатком известного устройства является низкое быстродействие.

Цель изобретения - повышение быстродействия коммутатора.

Указанная цель достигается за счет того, что в коммутаторе, содерж.ащем М передатчиков и N приемников, а также матрицу

ИЗ M-N узлов, в каждом из которых расположен элемент И коммутации, при этом первые входы элементов И коммутации каждого столбца матрицы объединены и подключены к информационному выходу соответствующего передатчика, а выходы элементов И коммутации каждой строки матрицы объединены и подключены ко входу соответствующего приемника, введены входной М-канальный и выходной N-канальный блоки приоритетного обслуживания, шифратор М регистров с разрядностью logiN, М дешифраторов, N канальных элементов ИЛИНЕ, управляющий элемент ИЛИ-НЕ и Nразрядный регистр маски, при этом каждый из входов входного блока приоритетного обслуживания соединен с управляющим выходом соответствующего передатчика, каждый

5 из информационных выходов - со входом считывания соответствующего регистра и управляющим входоад соответствующего дешифратора, первый и второй управляющие выходы подключены соответственно к управляющим входам регистра маски и выходного блока приоритетного обслуживания, информационные входы которого со&динены с выходами регистра маски, а вь1ходы подключены ко входам шифратора, выходы которого соединены с информационными входами регистров, выходы каждого из которых подключены к информационным входам соответствующего дешифратора, каждый из выходов каждого из которых соединен со вторым входом одного из элементов И коммутации соответствующего столбца матрицы и одним из входов соответствующего канального элемента ИЛИ-НЕ, выходы которых подключены к информационным входам регистра маски, а дополнительные входы объединены и подключены к выходу управляющего элемента ИЛИ-НЕ, входы которого соединены с информационными выходами входного блока приоритетного обслуживания.

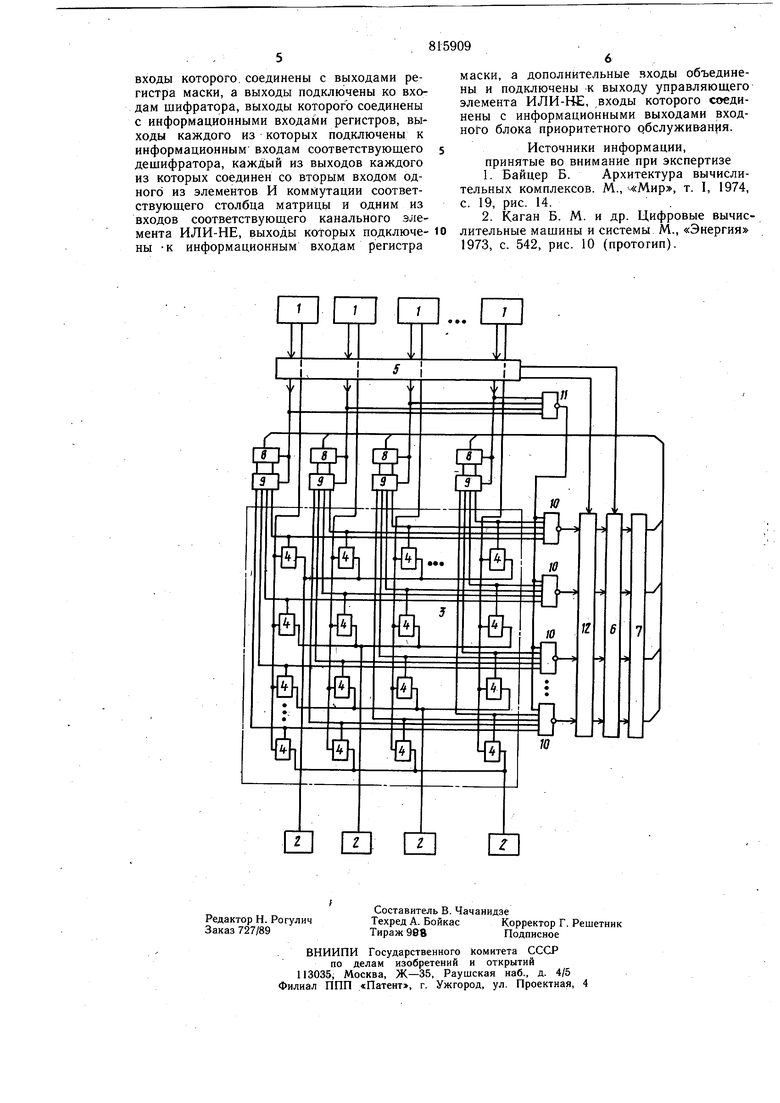

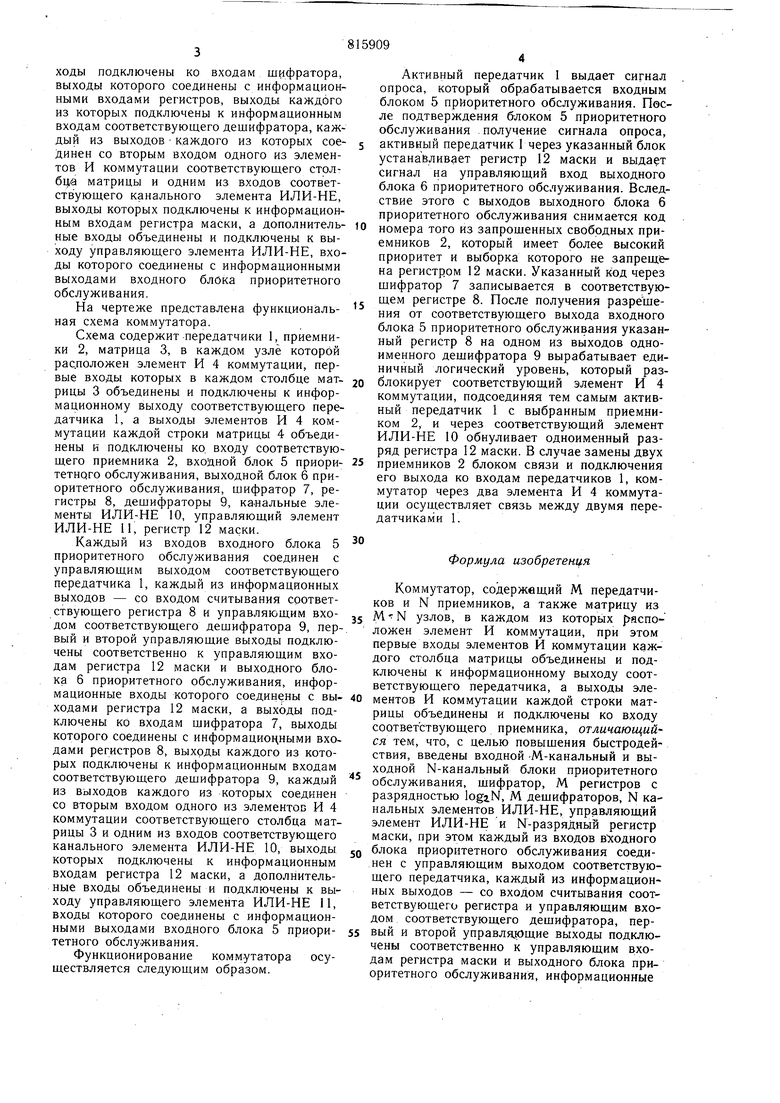

На чертеже представлена функциональная схема коммутатора.

Схема содержит передатчики 1, приемники 2, матрица 3, в каждом узле которой расположен элемент И 4 коммутации, первые входы которых в каждом столбце матрицы 3 объединены и подключены к информационному выходу соответствующего передатчика 1, а выходы элементов И 4 коммутации каждой строки матрицы 4 объединены и подключены ко. входу соответствующего приемника 2, входной блок 5 приоритетнрго обслуживания, выходной блок 6 приоритетного обслуживания, шифратор 7, регистры 8, дешифраторы 9, ка-нальные элементы ИЛИ-НЕ 10, управляющий элемент ИЛИ-НЕ И, регистр 12 маски.

Каждый из входов входного блока 5 приоритетного обслуживания соединен с управляющим выходом соответствующего передатчика 1, каждый из информационных выходов - со входом считывания соответствующего регистра 8 и управляющим входом соответствующего дешифратора 9, первый и второй управляющие выходы подключены соответственно к управляющим входам регистра 12 маски и выходного блока 6 приоритетного обслуживания, информационные входы которого соединены с выходами регистра 12 маски, а выходы подключены ко входам шифратора 7, выходы которого соединены с информационными входами регистров 8, выходы каждого из которых подключены к информационным входам соответствующего дешифратора 9, каждый из выходов каждого из которых соединен со вторым входом одного из элементов И 4 коммутации соответствующего столбца матрицы 3 и одним из входов соответствующего канального элемента ИЛИ-НЕ 10, выходы которых подключены к информационным входам регистра 12 маски, а дополнительные входы объединены и подключены к выходу управляющего элемента ИЛИ-НЕ 11, входы которого соединены с информационными выходами входного блока 5 приоритетного обслуживания.

Функционирование коммутатора осуществляется следующим образом.

Активный передатчик 1 выдает сигнал опроса, который обрабатывается входным блоком 5 приоритетного обслуживания. После подтверждения блоком 5 приоритетного обслуживания получение сигнала опроса, активный передатчик 1 через указанный блок устанавливает регистр 12 маски и выдает сигнал на управляющий вход выходного блока 6 приоритетного обслуживания. Вследствие этого с выходов выходного блока б приоритетного обслуживания снимается код номера того из запрошенных свободных приемников 2, который имеет более высокий приоритет и выборка которого не запрещена регистром 12 маски. Указанный к-од через щифратор 7 записывается в соответствующем регистре 8. После получения разрещения от соответствующего выхода входного блока 5 приоритетного обслуживания указанный регистр 8 на одном из выходов одноименного дещифратора 9 вырабатывает единичный логический уровень, который разблокирует соответствующий элемент И 4 коммутации, подсоединяя тем самым активный передатчик 1 с выбранным приемником 2, и через соответствующий элемент ИЛИНЕ 10 обнуливает одноименный разряд регистра 12 маски. В случае замены двух приемников 2 блоком связи и подключения его выхода ко входам передатчиков 1, коммутатор через два элемента И 4 коммутации осуществляет связь между двумя передатчиками 1.

Формула изобретен14я

Коммутатор, содержащий М передатчиков и N приемников, а также матрицу из М - N узлов, в каждом из которых расположен элемент И коммутации, при этом первые входы элементов И коммутации каждого столбца матрицы объединены и подключены к информационному выходу соответствующего передатчика, а выходы элементов И коммутации каждой строки матрицы объединены и подключены ко входу соответствующего приемника, отличающийся тем, что, с целью повышения быстродействия, введены входной -М-канальный и выходной N-канальный блоки приоритетного обслуживания, щифратор, М регистров с разрядностью logiN, М дешифраторов, N канальных элементов ИЛИ-НЕ, управляющий элемент ИЛИ-НЕ и N-разрядный регистр маски, при этом каждый из входов выходного блока приоритетного обслуживания соединен с управляющим выходом соответствующего передатчика, каждый из информационных выходов - со входом считывания соответствующего регистра и управляющим входом соответствующего дешифратора, первый и второй управляющие выходы подключены соответственно к управляющим входам регистра маски и выходного блока приоритетного обслуживания, информационные

Авторы

Даты

1981-03-23—Публикация

1979-05-18—Подача