(54) УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| Устройство цикловой синхронизации | 1980 |

|

SU924892A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2005 |

|

RU2280956C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2810267C1 |

| Устройство приема двоичной информации в последовательном коде | 1991 |

|

SU1771075A1 |

| Устройство цикловой синхронизации | 1977 |

|

SU628629A1 |

| Устройство синхронизации приёмной и передающей части радиолинии при использовании короткоимпульсных сверхширокополосных сигналов | 2019 |

|

RU2713379C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2007 |

|

RU2348117C1 |

I

Изобретение относится к устройствам обработки информации и может использоваться в системах с импульсно-кодовой модуляцией, в системах передачи дискретных сообщений.

Известно устройство для синхронизации по циклам, содержащее первый и второй регистры сдвига, выходы разрядов которых через дещифратор подключены к первому входу решающего блока, второй вход которого является входом устройства 1.

Однако известное устройство имеет сравнительно низкую помехоустойчивость синхро низации при передаче информации по каналам связи с помехами, обусловленную невыделением синхросигналов при искажении принятых синхроимпульсов. Действительно, в режиме поиска синхронизма детерминированные синхроимпульсы, принятые с ошиб кой, ложно преобразуются в комбинации, соответствующие информационным позициям- цикла, что препятствует правильному накоплению синхросигналов в регистрах сдвига и, следовательно, выделению цикловой фазы дещифратором синхросигнала.

Цель изобретения - повыщение помехоустойчивости синхронизации.

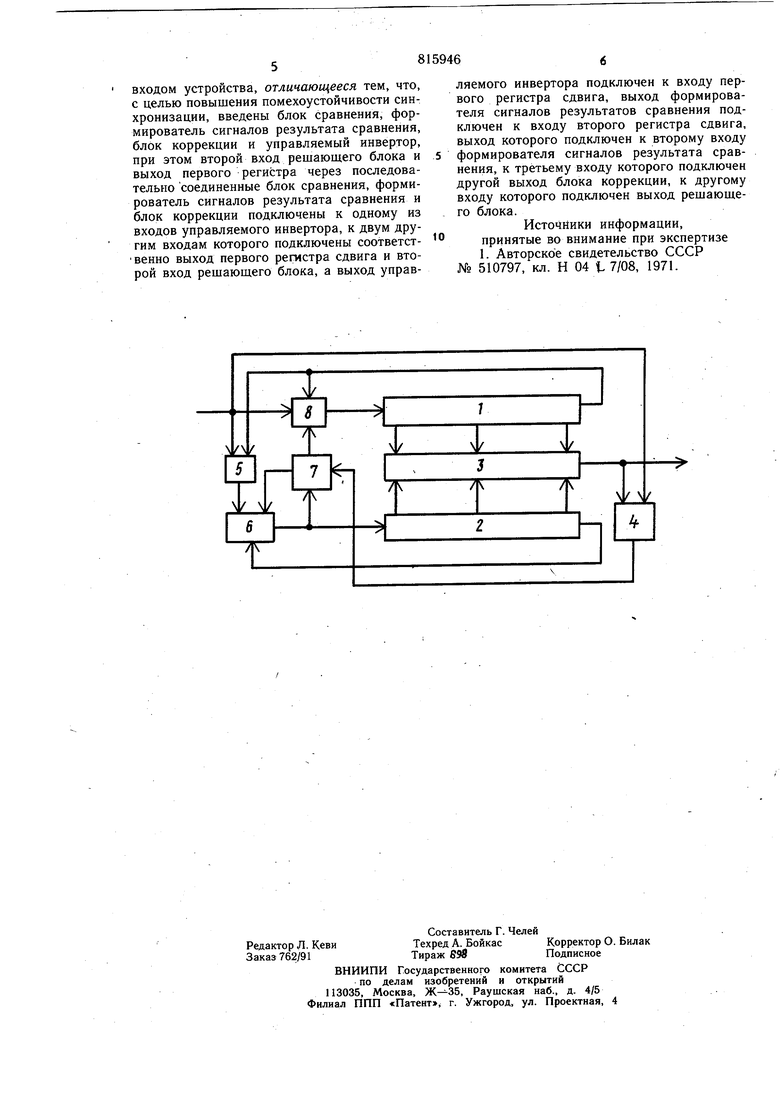

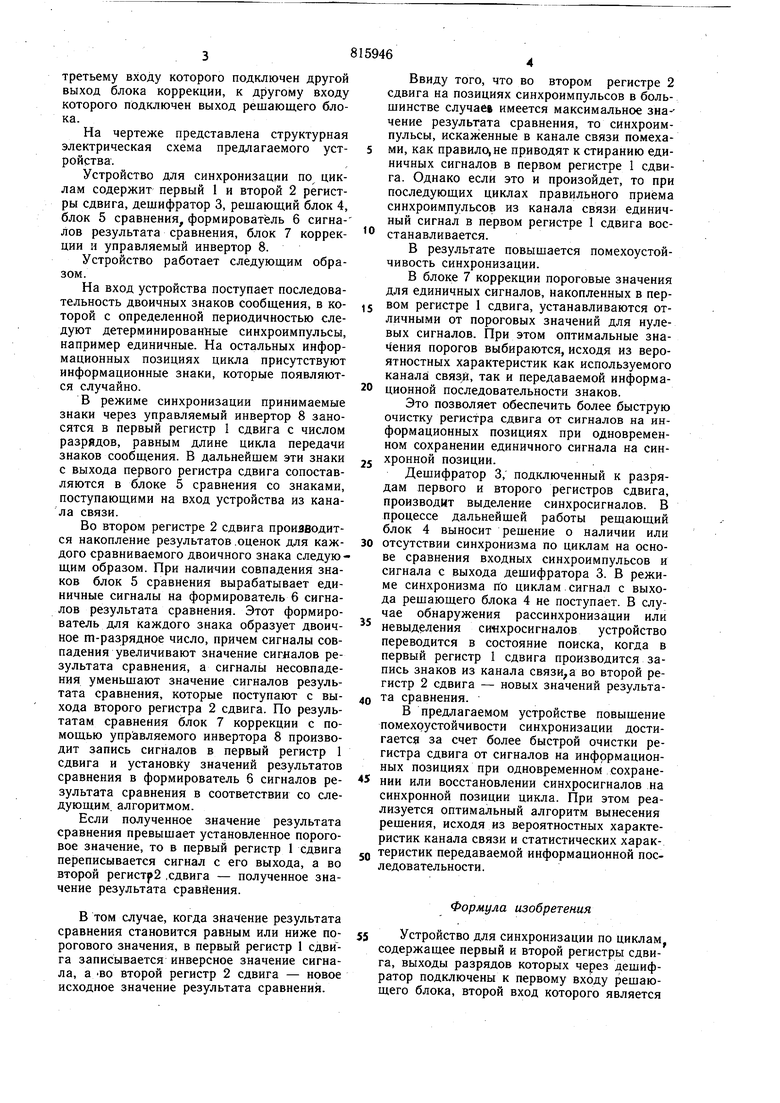

Цель достигается тем, что в устройство для синхронизации по циклам, содержащее первый и второй регистры сдвига, выходы разрядов которых через дешифратор подключены к первому входу решающего блока, второй вход которого является входом устройства, введены блок сравнения, формирователь сигналов результата сравнения, блок коррекции и управляемый инвертор, при этом второй вход рещающего блока и выход первого регистра через последовательносоединенные блок сравнения, формирователь сигналов результата сравнения и блок коррекции подключены к одному из входов управляемого инвертора, к двум другим входам которого подключены соответственно выход первого регистра сдвига и второй вход решающего блока, а выход управляемого инвертора подключён к входу первого регистра сдвига, выход формирователя сигналов результатов сравнения подключен к входу второго регистра сдвига, выход которого подключен к второму входу формирователя сигналов результата сравнения, к третьему входу которого подключен другой выход блока коррекции, к другому входу которого подключен выход решающего блока. На чертеже представлена структурная электрическая схема предлагаемого устройства. Устройство для синхронизации по циклам содержит первый 1 и второй 2 регистры сдвига, дешифратор 3, решающий блок 4, блок 5 сравнения, формирователь 6 сигналов результата сравнения, блок 7 коррекции и управляемый инвертор 8. Устройство работает следующим образом. На вход устройства поступает последовательность двоичных знаков сообщения, в которой с определенной периодичностью следуют детерминированные синхроимпульсы, например единичные. На остальных информационных позициях цикла присутствуют информационные знаки, которые появляются случайно. В режиме синхронизации принимаемые знаки через управляемый инвертор 8 заносятся в первый регистр 1 сдвига с числом разрядов, равным длине цикла передачи знаков сообщения. В дальнейшем эти знаки с выхода первого регистра сдвига сопоставляются в блоке 5 сравнения со знаками, поступающими на вход устройства из канала связи. Во втором регистре 2 сдвига производится накопление результатов.оценок для каждого сравниваемого двоичного знака следующим образом. При наличии совпадения знаков блок 5 сравнения вырабатывает единичные сигналы на формирователь 6 сигналов результата сравнения. Этот формирователь для каждого знака образует двоичное т-разрядное число, причем сигналы совпадения увеличивают значение сигналов результата сравнения, а сигналы несовпадения уменьшают значение сигналов результата сравнения, которые поступают с выхода второго регистра 2 сдвига. По результатам сравнения блок 7 коррекции с помощью управляемого инвертора 8 производит запись сигналов в первый регистр 1 сдвига и установку значений результатов сравнения в формирователь б сигналов результата сравнения в соответствии со следующим, алгоритмом. Если полученное значение результата сравнения превышает установленное пороговое значение, то в первый регистр 1 сдвига переписывается сигнал с его выхода, а во второй регистр2 .сдвига - полученное значение результата сравнения. В том случае, когда значение результата сравнения становится равным или ниже порогового значения, в первый регистр 1 записывается инверсное значение сигнала, а ВО второй регистр 2 сдвига - новое исходное значение результата сравнения. Ввиду того, что во втором регистре 2 сдвига на позициях синхроимпульсов в большинстве случае имеется максимальное зна-чение результата сравнения, то синхроимпульсы, искаженные в канале связи помехами, как правило, не приводят к стиранию единичных сигналов в первом регистре 1 сдвига. Однако если это и произойдет, то при последующих циклах правильного приёма синхроимпульсов из канала связи единичный сигнал в первом регистре 1 сдвига восстанавливается. В результате повыщается помехоустойчивость синхронизации. В блоке 7 коррекции пороговые значения для единичных сигналов, накопленных в первом регистре I сдвига, устанавливаются отличными от пороговых значений для нулевых сигналов. При этом оптимальные значения порогов выбираются, исходя из вероятностных характеристик как используемого канала связи, так и передаваемой информационной последовательности знаков. Это позволяет обеспечить более быструю очистку регистра сдвига от сигналов на информационных позициях при одновременном сохранении единичного сигнала на синхронной позиции. Дещифратор 3, подключенный к разрядам первого и второго регистров сдвига, производит выделение синхросигналов. В процессе дальнейшей работы решающий блок 4 выносит решение о наличии или отсутствии синхронизма по циклам на основе сравнения входных синхроимпульсов и сигнала с выхода дещифратора 3. В режиме синхронизма по циклам сигнал с выхода решающего блока 4 не поступает. В случае обнаружения рассинхронизации или невыделения си«хросигналов устройство переводится в состояние поиска, когда в первый регистр I сдвига производится запись знаков из канала связи,а во второй регистр 2 сдвига - новых значений результата сравнения. В предлагаемом устройстве повышение помехоустойчивости синхронизации достигается за счет более быстрой очистки регистра сдвига от сигналов на информационных позициях при одновременном сохранении или восстановлении синхросигналов на синхронной позиции цикла. При этом реализуется оптимальный алгоритм вынесения решения, исходя из вероятностных характеристик канала связи и статистических характеристик передаваемой информационной последовательности. Формула изобретения Устройство для синхронизации по циклам содержащее первый и второй регистры сдвига, выходы разрядов которых через дешифратор подключены к первому входу решающего блока, второй вход которого является

входом устройства, отличающееся тем, что, с целью повышения помехоустойчивости синхроиизации, введены блок сравнения, формирователь сигналов результата сравнения, блок коррекции и управляемый инвертор, при этом второй вход решающего блока и выход первого регистра через последовательно соединенные блок сравнения, формирователь сигналов результата сравнения и блок коррекции подключены к одному из входов управляемого инвертора, к двум другим входам которого подключены соответственно выход первого регистра сдвига и второй вход решающего блока, а выход управляемого инвертора подключен к входу первого регистра сдвига, выход формирователя сигналов результатов сравнения подключен к входу второго регистра сдвига, выход которого подключен к второму входу формирователя сигналов результата сравнения, к третьему входу которого подключен другой выход блока коррекции, к другому входу которого подключен выход решающего блока.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 510797, кл. Н 04 t 7/08, 1971.

Авторы

Даты

1981-03-23—Публикация

1979-05-14—Подача