(54) УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

| Устройство цикловой синхронизации | 1981 |

|

SU949832A1 |

| Устройство цикловой синхронизации | 1981 |

|

SU987836A1 |

| Приемник синхросигнала | 1981 |

|

SU1092745A1 |

| Устройство цикловой синхронизации | 1979 |

|

SU1259504A1 |

| Устройство цикловой синхронизации (его варианты) | 1979 |

|

SU864586A1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

| Устройство цикловой синхронизации (его варианты) | 1980 |

|

SU951738A2 |

| Устройство цикловой синхронизации | 1980 |

|

SU1341727A2 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 1999 |

|

RU2173027C2 |

1

Изобретение относится к электросвязи и может быть использовано для циклового фазирования систем передачи дискретных сигналов.

Известно устройство шпсловой синхронизации, содержащее регистр сдв1тга, выходы которого через дешифратор подключены к информационным входам первого и второго анализаторов, к тактовому входу первого анализатора подключен соот ветствующий выход распределителя импульсов, выходы первого анализатора подключе п 1 соответственно к тактовым входам первого и второго н&копителай, выход второго анализатора соединен через блок управления со сбросовым входом делителя частоты, выход которого соединен с тактовым входом второго анализатора, третьего накопителя и с первым входом блока совпадения, к второму входу которого подключен выход ipe- тьего накопителя, а выход блока совпадения подключен к установочному входу распределителя импульсов, тактовый вход

которого объединен с тактовыми входами регистра сдвиг а и делителя частоты, вход регистра сдвш-а 1шляется информационным входом устройства tl}Недостатком устройства $шляется малое быстродействие и низкая помехоустойчивость. .. ,

Цель изобретения - повышение быст родействия и помехоустойчивости.

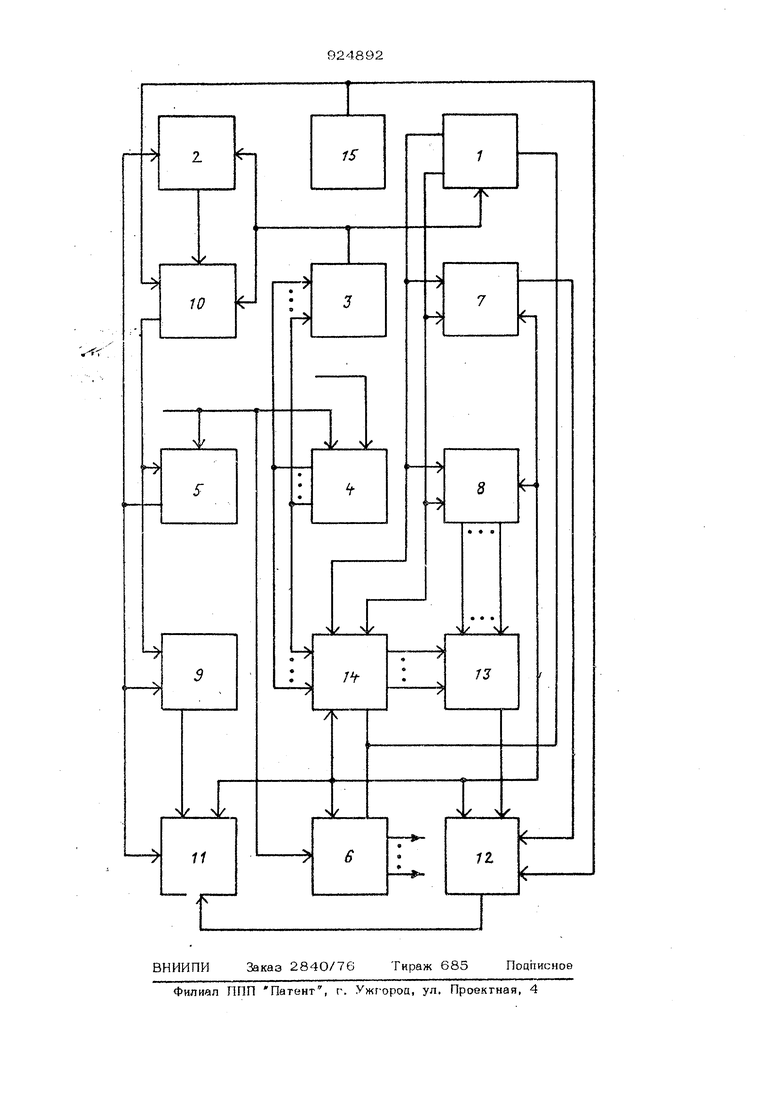

Для достижения указанной цели в устройство шссловой синхронизации, содержащее регистр , выходы которого через дешифратор подключены к информационным входам первого и второго анализаторов, к тактовому входу первого анализатора подключен соответствующий выход распределителя импульсов, выходы первого анализатора подключены соответственно к тактовым вхо- .дам первого и второго накопителей, выход второго анатшзатора соединен через блок управления со сбросовым входом делителя частоты, выход которого соединен с тактовым входом второго анализатора, третьего накопителя и с первым входом облока совпадения, к второму входу кото рого подключен выход третьего накопите ш, а выход блока совпадения подключен к установочному бходу распредели теля импульсов, тактовый вход которого ооъединен с тактовыми входами регистр одвига и делителя частоты, а вход ретгистра сдвига является входом устройетва, введены последовательно соединен |1ые решающий блок, коммутатор и триг гер, а также формирователь сигнала Сброс, при этом выходы регистра сды-гга подключены к входам решающего блока, к другой группе входов коммута тора подключены выходы второго накопителя, первый вход сброса которого объединен с соответствующими входами первого накопителя, триггера и решающего блока и, соединен с выходом блока совпадения, к третьему входу которого подключен выход триггера, к другому входу сброса которого подключен выход первого накопителя, к входу сброса которого подключен второй выход первого анализатора и управляющий вход решающего блока, другой вход сбр са которого объединен с соответствующим входом второго накопителя и с пер вым выходом первого анализатора, инфо машюнный вход которого объединен с жхформационным входом блока управлени выход которого соединен с входом сбро третьего накопителя, причем выход фор Mj-фователя сигнала Сброс соединен с установочным входом блока управления и с другим установоч1Ш1м входом тр1пт ра. На чертеже изображена структурная электр1тческая схема устройства цикловой синхронизации. Устройство цикловойсинхронизации, содержит анализаторы 1 и 2, дешифратор 3, регистр 4 сдвига, делитель 5 частоты, распределитель 6 импульсов, накопители 7, 8 и 9, блок 10 управления, блок 11 совпадения, триггер 12, коммутатор 13, решающий блок 14 и формирователь 15 сигнала Сброс. Устройство работает следующим образом. В момент включения устройства сигнал с выхода формирователя 15 устанавливает триггер 12 в единичное состояние и подготавливает блок управления 10 к работе. На вход регистра 4 поступает последовательность прзшимаемых элементов сообщения, а на тактовый вход устройства - последовательность тактовых импульсов, следующих с частотой поступления принимаемых элементов. Если момент включения устройства совпал во времени с поступлением на вход регистра 4 сдвига фазирующей комбинации, то сигналы на выходах последнего такта распределителя и rayльcoв 6 и делителя 5 совпадают во времени с сигналом на выходе дешифратора 3, вследствие чего на выходе анализатора 2 выходной сигнал не формируется, а на первом выходе анализатора 1 в каждом цшсле приема фазирующей комбинации i формируются сигналы, заряжающие накопитель 7. При поступлении на его вход Ксигнала накопитель зарялсается и сигнал, с его выхода сбрасьшает триггер 12 в нулевое состояние, вследствие чего блой совпадения 11 оказывается закрытым по третьему входу для прохожцения сигналов на установку распределителя импульсов 6 для работы на новой временной позиции, т. е. устройство находится в состоянии синхронизации. Если момент включения устройства не совпал с моментом приема из канала связи фазирующей комбинации, то первый же сигнал на выходе дешифратора 3 проходит на блок 10 управления, возвращая его в исходное состояние. Сигнал с выхода блока управления 1О переводит делитель 5 в нулевое состояние, вследствие чего анализатор 2 проверяет поступление сигнала с выхода дешифратора 3 на новой временной позиции. В случае, если сигнал, прошедший на ЗЫХ.ОД блока 10 управления, является синхросигналом, то он формируется на выходе дешифратора 3 на одной и той же временной позиции в каждом цикле.принимаемого сигнала и совпадает во времени с .сигналом на выходе делителя 5. В этом случае сигналы на выходе анализаторЕ отсутствуют, а сигналы с выхода делителя 5 заряжают накопитель 9. При поступлении на вход накопителя 9 Ко, импулг сов на его выходе формируется уровень напряжения, открьшающий блок совпадения 11 по второму входу, вследсгаие чего сигнал с выхода делителя 5 проходит на выход блока 11 совпадения, устанавливая распределитель 6 импульсов в новое исходное состояние и сбрасьшая триггер 12 Б нулевое состояние. Начиная с этого момента времени, устройство приняло решение о вхождении в синхронизм, при этом сигналы с выхода послед него такта распределителя 6 совпадают во времени с сигналами на выходах деишфратора 3 и делителя 5. В случае, если сигнал, прошедший на выход блока 10 управления, не даляется синхросигналом, то в одном из следующ циклов передачи он не совпадает во вре мени с сигналом на выходе делителя 5, вследствие чего на выходе анализатора формируется сигнал, устанавливающий блок 10 управления в состояние готовности к работе, которое сохраняется до момента вьщеления дещифратором 3 сиг нала об обнаружении комбинации, аналогичной фазирующей. Сигнал с выхода дещифратора 3 проходит через блок 10 управления возвращая его в исходное ;остояние, и сбрасывает делигеяь 5 и шкопитель 9 в исходное состояние. Всле ;твие этого анализатор 2 начинает контроль импульсов на новой временной пози дии цикла. Далее процесс работы анало гичен вьплеописанному. В состоянии синхронизма сигнал на выходе дешифратора 3 в каждом цикле принимаемых сообщений совпадает во времени с сигналами на выходе делителя 5 и выходе последнего такта распределителя 6. В случае нарушения синхронизма при сбое в работе передающие части системы передачи и приемной части аппаратуры в момент поступления сигнала .ода последнего такта распределителя 6 в регистре сдвига 4 оказывается записанной комбинация, значительно отличак щаяся от фазирующей, а на втором выходе анализатора 1 формируется сигнал несовпадения. Вследствие этого решающий блок. 14 определяет насколько принятый сигнал отличается от фазирующей комбинации, осуществляет усреднение это величины за несколько циклов приема и в соответствии с полученной величиной фо мируют сигнал на определенной выходной шине. В зависимости от того, на какой вз ходных шин решающего блока 14 формируется выходной сигнал, коммутатор 13 осуществляет соединение своей выходной шины с соответствующим выходом накопителя 8. Одновременно с этим сигналы со второго выхода анализатора 1 осуществляют последовательный заряд накопителя 8. Таким образом, сигналы с выхода решающего блока 14 автоматически устанавливают в зависимости от степени несовпадения структуры фаз1фую1цей комбинашш со структурой проверяемой кр 1бинацш1 в регистре сдвига требуемый коэффиЩ1ент накопления накопителя 8, т. е. определяют число циклов проверки отсутствия фазирующей комбинашш на прежней временной позиции, у стройство принимает решение о потере синхронизма и готово к запуску распределителя 6 на новой временной позиции. Параллельно с этим процессом происходит поиск синхронизирующей комбинации цепью, состо5пдей из анализатора 2, блока 10 управления, делителя 5 и накопителя 9. При заряде накопителя 9 блок 11 совпадения открьтается по второму входу, вследствие чего сигнал с выхода делителя 5 через блок 11 совйадени$1 устанавливает распределитель 6 в новое исходное положение, а также переводит а нулевое состояние накопители 7 и 8, триггер 12 и решающий блок 14. Если аовое исходное состояние распределителя 6 не является синхронным с циклом пр1шкмаемых элементов сообщения, то процесс установления синхронизма повторяется. В случае, если нарушение синхронноскнфаз ного поступления фазирующей комбинации произошло из-за воздействия помех в канале связи, устройство рабо тает, следующим образом. В момент поступления сигнала с вы1сЬаа последнего тактараспределителя 6 в ре- грстре 4 сдвига оказывается комбинация, незначительно отличающаяся от фаз1фук щей, а на втором выходе анализатора 1 формируется сигнал несовпадения, который записывает единицу в ншсопитель 8. Вследствие этого решающий блок 14 формирует выходной сигнал на определенной шине, а коммутатор 13 осуществляет коммутацию своей выходной шиной с одним из последующих выходов накопителя 8. Поэтому еще до момейта формирования сигнала на выходной шине коммутатора 13 анализатор 1 обнаруживает фазирующую комбинацию на прежней временной позишш, а на его первом выходе формируется сигнал, сбрасывающий накопитель 8 и решающий блок 14 в нулевое состояние и записывающий единицу в накопитель 7. Таким образом, ошибочная установка рвспределнтеля 6 в новое исходное cocTo.snme не произошла и устройство сохраняет синхронно-синфазную работу с принимаемыми шсклами информации, Накопитель 7 выполняет фу1шшп1 допопиите;гоной зашиты устройства от ошибочной установки распределителя 6 в новое исходное состояние. Так, в , если триггер 12 установлен в единичное состояние сш-иалом с выхода формирователя 15 или с выхода коммутатора 13, т. е. принято решение о потере синхронизма, а параллельной депью контроля синхросщ-нала {анали затор 2, управления 10, делитель 5 и наконитель 9) все еще не обнаруже устойчзюо повторяющаяся в кадодом шасл на одних и тех же новых позиш$ях ком6ifflaijHH, аналогичная фазирующей, то обнаружение подобной комбинашп на прежнш: временных позициях, осузцествленное анализатором 1 в течение К гетша подряд, приведет к заряцу накопителя 7, сигнал с выхода которого сбросит триггер 12 в ноль. Вследствие чего сохранится синхронно-синфазная работа устройства на прежних временных ПОЗИЩ1ЯХ, Введение формирователя сброса поэволяет при первоначальном включению устройства или в случае сбоев в подаче Ш1тающ1к напряженн.йоткрыть блок 11 совпадения для установки распределителя в исходное синфазное состояние без предварительного заряда накопителя 8, что уменьшает время несинфазной работы устройства и ведет к повышению быстродействия и помехоустойчивости фазирован1м, Нал1-гчие решающего блока 14, комму татора 13 и триггера 12 в предлагаемом устройстве позволяет повысить быс родействие и помехоустойчивость восста новления синхронизма путем введения зависимости числа циклов проверки поступления фаз1фующей комбннашп (времени поддержания синхронизма на преж- них временных позициях ,щпсла) от сте- пени несоответствия контролируемой ком бинагши принимаемых элементов сообщени фазирующей комбинации, т. е. введения усредненного за несколько циклов по степени несоответствия критерия различения искаженной фазирующей комбинаци от временного сбоя в работе нередающей части системы передачи. В случае значительных отличий контролируемой комбинации от фазирующей в течение нескольких шжлов проверки (что необходимо уменьшения вероятности ошибки от воздействия групповых помех, так назьшаемых пакетов ошибок) установ ка 1.2 в ед1шичнос состояние (т. е. подготовка блока 11 совпадения для установки распределители 6 в исходное состояние) производится через меньшее число проверок несовпадения циклов работы распределителя, так как в этом случае вьпие вероятность того, что про- изощел временной сбой устройства, чем в случае малых отличий контролируемой комбинации от фазирующей, когда вьпие вероятность того, что сбоя в работе устройства не произощло, а отсутствие фазирующей комбинации вызвано помехами в канале связи. Отсюда следует, что предлагаемое устройство обеспечивает в сравнении с известными устройствами повьпиение помехоустойчивости и быстродействия фазирования. Формула изобре1ения Устройство цикловой синхронизации, содержащее регистр сдвига, выходы которого через дешифратор подключены к 1-гаформадионкым входам первого и второго анахшзаторов, к тактовому входу первого анализаторе подключен соответст- вующ.чй выход распределителя импульсов, выходы первого анализатора подключены соответственно к тактовым входам первого и второго накопителей, выход второго анализатора соединен через блок управления со сбросовым входом делителя частоты, выход которого соединен с тактовым входом второго анализатора, третьего накопителя и с первым входом блока совпадения, к второму входу которого подключен выход третьего накопителя, а выход совпадения подгслючен к установочному входу распределителя импульсов, тактовый вход которого объединен с тактовыми входами регистра сдви- .га и делителя частоты, а вход регистра сдвига является информациошатм входом устройства, отличающееся тем, что, с целью повышения быстродейстия и помехоустойчивости, в него введены последовательно соединенные региающий блок, коммутатор и триггер, а также формирователь сигнала Сброс, при этом йыходы регистра сдвьта подключет1ы к входам решающего блока, к другой группе входов коммутатора подключены выходы второго накопителя, первый вход сброса которого объединен с соответствующими входами первого накопителя, триггера и решающего блока и соединен с выходом блока совпадения, к третьему входу которого подключен выход триггера, к другому входу сброса которого подключен выход пердаого на- копителя, к другому входу сброса которого подключен второй выход первого анализатора и управляющий вход решак щего блока дургой вход сброса которого объединен с соответствуюпгам входом

второго накопители и с первым выходом первого анализатора, информационный

вход которого объединен с информационным входом блока управления, выход ко торого соединен с входом сброса третьего накопителя, причем выход формироватеда сигнала Сброс соединен с установочным входом блока управления и с другим установочным входом триггера.

Источники янформашт, принятые во внимание при экспертизе

Авторы

Даты

1982-04-30—Публикация

1980-09-02—Подача