(54) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ИСПРАВЛЯЮЩЕЙ СПОСОБНОСТИ ПРИЕМНИКА ДВОИЧНБ1Х СИГНАЛОВ

ВХОДОМ элемента памяти и с первыми входами третьего и четвертого элементов И, выходы которых соединены соответственно с первым и вторым входами первого элемента ИЛИ, выход блока задержки фронта импульса соединен с вторым входом триггера, первый выход элемента памяти соединен с вторым входом ключа, третий вход которого объединен с первым входом делителя частоты, второй вход которого соединен с первым входом второго элемента ИЛИ и с выходом первого элемента И, второй вход которого соединен с выходом дополнительного триггера и с вторым входом второго элемента И, выход которого соединен с третьим входом делителя частоты и с вторым входом второго элемента ИЛИ, выход которого соединен с третьим входом элемента памяти, второй выход которого соединен с вторым в){одом третьего элемента И, и с входом инвертора, выход которого соединен с вторым входом четвертого элемента И, третий вход которого соединен с вторым выходом блока опорных частот, третий вход третьего элемента И соединен с выходом формирователя импульсов, а на первый и второй входы дополнительного триггера, на третьи входы первого и второго элементов И и второго элемента ИЛИ и на четвертый вход делителя частоты поданы соответственно сигналы пуска, ошибки, опережения, отставания, постоянных искажений и сброса.

Формирователь зоны искажений содержит второй дополнительный триггер, пятый и шестой элементы И, первый и второй дополнительные инверторы, и третий элемент ИЛИ, при этом первый и второй выходы второго дополнительного триггера соединены с первыми входами соответственно пятого и шестого элементов И, вторые входы которых соединены соответственно с выходами первого и второго дополнительных инверторов, причем вход второго дополнительного инвертора, который объединен с третьим входом пятого элемента И и с первым входом второго дополнительного триггера, является первым входом формирователя зоны искажений, вторым входом которого является третий вход шестого элемента И, который объединен с входом первого дополнительного триггера, выход которого соединен с вторым входом второго дополнительного триггера, а вых ОА формирователя зоны искажений является выход третьего элемента ИЛИ, первый и второй входы которого соединены соответственно с выходами пятого и шестого элементов И.

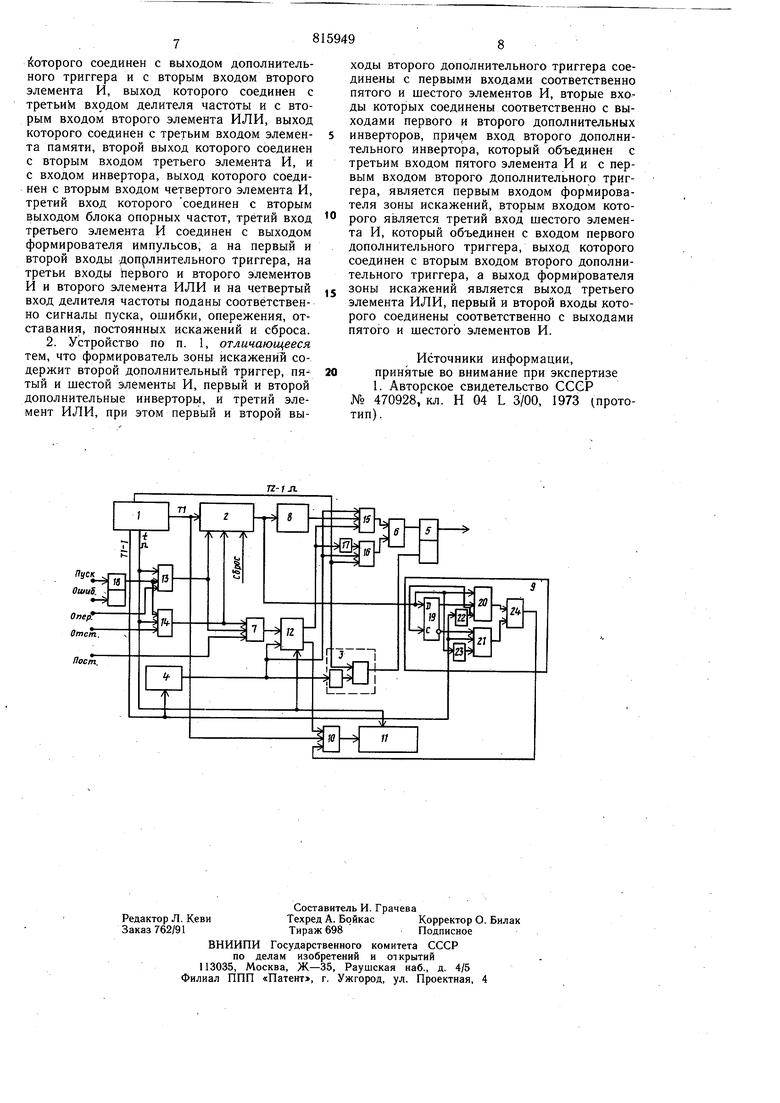

На чертеже изображена структурная электрическая схема предлагаемого устройства для измерения исправляюшей способности приемника двоичных сигналов.

Предлагаемое устройство содержит блок 1 опорных частот, делитель 2 частоты, блок 3 задержки фронта импульса, датчик 4 кода, триггер 5, первый элемент ИЛИ 6, второй элемент ИЛИ 7, формирователь 8 импульсов, формирователь 9 зоны искажений, ключ 10, блок 11 счета и индикации, элемент 12 памяти, первый 13, второй 14, третий 15, четвертый 16 элементы И, инвертор 17, дополнительный триггер 18, второй дополнительный триггер. 19, пятый 20 и шестой 21 элементы И, первый 22 и второй 23 дополнительные инверторы, третий элемент ИЛИ 24.

Устройство для измерения исправляюш,ей способности приемника двоичных сигналов работает следуюш,им образом.

При включении блок 1 опорных частот формирует тактовые последовательности импульсов и импульсы частотой в п раз превышаюшей скорость первой тактовой последовательности (при минимальной величине искажений 1%, п 100). Дополнительный триггер 18 находится в состоянии «О, поэтому первый 13 и второй 14 элементы И закрыты и не формируют сигналы «добавления и «вычитания, на делитель 2 поступает только импульсная последовательность. При поступлении на вход делителя 2 сигнала «сброс, всегда совпадающего по фазе с отрицательным перепадом первой тактовой последовательности, делитель 2 формирует импульсную последовательность с частотой первой тактовой последовательности, совпадающую по фазе с импульсной последовательностью, формируемой блоком 1 опорных частот. При этом на выходе формирователя 8 появляются импульсы, совпадающие по фазе с импульсами второй тактовой последовательности, формируемые блоком 1 опорных частот. При отсутствии сигналов на выходе первого 13 и второго

14элементов И, на первом выходе элемента 12 памяти имеется постоянный низкий уровень, закрывающий третий элемент И

15и открывающий четвертый элемент И 16 через инвертор 17. В этом случае, если на вход четвертого элемента И 16 поступают от датчика 4 кода положительные посылки, то на выходе четвертого элемента И 16 появляются импульсы, совпадающие по фазе с импульсами второй тактовой последовательности. Если на выходе датчика 4 кода формируются отрицательные посылки, то на выходе блока 3 появляются импульсы, совпадающие по фазе с импульсами второй тактовой последовательности. Дополнительный триггер 18 формирует последовательность импульсов, сдвинутую на половину такта относительно исходной последовательности, формируемой датчиком 4 кода. Таким образом, блок 3 задержки фронта обеспечивает постоянную задержку фронта на половину такта.

Если на вход первого элемента И 13 поступает сигнал «опережение, а на вход дополнительного триггера 18 сигнал «пуск, то он переводится в состояние «1, и открывается первый элемент И 13. В моменты

поступления на вход первого элемента И 13 импульсов, следующих через интервалы времени, на выходе его формируется сигнал «добавление. При этом фаза импульсов на выходе делителя 2 смещается в сторону «опережения. Одновременно импульсы с выхода первого элемента И 13 через второй элемент ИЛИ 7 поступают в элемент 12 памяти, который формирует импульс длительностью в один тактовый интервал. Этот импульс совпадает с передним фронтом положительной посылки, формируемой датчиком 4 кода. С выхода элемента 12 памяти импульс поступает на третий элемент И 15 и открывает его. При этом импульс, сформированный формирователем 8 импульсов проходит через третий элемент И 15 и первый элемент ИЛИ 6, переводя триггер 5 в состояние «1. Одновременно импульс с выхода элемента 12 памяти проходит через инвертор 17 на вход второго элемента И 14 и закрывает его. Задний фронт информации формируется первым импульсом второй тактовой последовательности после появления на выходе датчика 4 кода отрицательной посылки. При превыщении величин,1 краевых искажений исправляющей способности проверяемой аппаратуры в этой аппаратуре формируется сигнал «ошибка, который переводит дополнительный триггер 19 пуска в состояние «О. При этом закрываются первый 13 и второй 14 элементы И, которые перестают формировать сигналы «добавление («вычитание). Измерение величины краевых искажений осуществляется блоком 11. Второй дополнительный триггер 19 определяет сдвиг фазы между первой тактовой последовательностью, формируемой блоком 1 опорных частот и делителем 2. Если фаза тактовой частоты управлемого делителя 2 опережает фазу первой тактовой последовательности блока 1 опорных частот, то импульсы, поступающие через первый дополнительный инвертор 22 на С-вход второго дополнительного триггера 19, переводят его в состояние «О, при этом открывается щестой элемент И 21 и на вход ключа 10 поступают положительные импульсы. Если фаза тактовой частоты делителя 2 отстает от фазы первой тактовой последовательности блока 1 опорных частот, то второй дополнительный триггер 19 переводится в состояние «Ь, при этом открывается шестой элемент И 21 .и на вход ключа 10 поступают положительные импульсы. Импульсы интервала t, поступающие в элемент 12 памяти, запоминаются в нем и затем, при поступлении очередного переднего фронта положительной посылки, формируют импульс длительностью в один тактовый интервал. Этот импульс поступает на ключ 10 и открывает его. Поэтому очередной импульс, сформированный в формирователе 9 зоны искажений открывает по второму входу ключ 10 и в блок 11, предварительно сброшенный передним фронтом импульса периода t, сформированного блоком 1 опорных

частот, записывается пакет импульсов частоты Tj. Так как длительность импульсов, поступающих на второй вход ключа 10, пропорциональна фазе расстройки частот первой последовательности, то число импульсов 5 пакета, записанного в блок 11, равно величине краевых искажений. В случае, если на вход второго элемента ИЛИ 7 поступает сигнал постоянных искажений, эле.мент 12 памяти постоянно формирует импульсы, совпадающие с передним фронтом посылки.

° При этом все импульсы от блока 3 проходят через третий элемент И 15 и вся импульсная последовательность, сформированная триггером 5, передается искаженной. Величина искажения определяется ранее

15 установленным фазовым сдвигом между тактами первой тактовой последовательности делителя 2.

Использование предлагаемого устройства для измерения исп равляющей способности приемника двоичных сигналов позволяет

20 сократить время измерения и автоматизировать процесс измерений.

Формула изобретения

: Устройство ДЛЯ измерения исправляющей способности приемника двоичных сигналов, содержащее блок опорных частот, первый и второй выходы которого соединены соответственно с первым входом делителя частоты и с первым входом блока задержки фронта импульса, второй вход которого соединен с выходом датчика кода, триггер, первый вход которого соединен с выходом первого элемента ИЛИ, и второй элемент ИЛИ, отличающееся тем, что с целью сокращения времени измерения, введены формирователь импульсов, формирователь зоны искажений, ключ, блок счета и индикации, элемент памяти, четыре элемента И, инвертор и дополнительный триггер, при этом выход делителя частоты соединен . с входом формирователя импульсов и с первым входом формирователя зоны искажений, выход которого через ключ соединен с первым входом блока счета и индикации, второй вход которого соединен с первыми входами элемента памяти и первого и второго элементов И и с третьим выходом блока опорных частот, четвертый выход которого соединен с вторым входом формирователя зоны искажений и с входом датчика кода, выход которого соединен с вторым входом элемента памяти и с первыми в.ходами третьего и четвертого элементов И. выходы которых соединены соответственно с первым и вторым входами первого элемента ИЛИ, выход блока задержки фронта импульса соединен с вторым входом триггера, первый выход элемента памяти соеди-нен с вторым входом ключа, третий вход которого объединен с входом делителя частоты, второй вход которого соединен с первым входом второго элемента ИЛИ и с выходом первого элемента И, второй вход йоторого соединен с выходом дополнительного триггера и с вторым входом второго элемента И, выход которого соединен с третьи1и входом делителя частоты и с вторым входом второго элемента ИЛИ, выход которого соединен с третьим входом элемента памяти, второй выход которого соединен с вторым входом третьего элемента И, и с входом инвертора, выход которого соединен с вторым входом четвертого элемента И, третий вход которого соединен с вторым выходом блока опорных частот, третий вход третьего элемента И соединен с выходом формирователя импульсов, а на первый и второй входы дополнительного tpHrrepa, на третьи входы Ьервого и второго элементов И и второго элемента ИЛИ и на четвертый вход делителя частоты поданы соответственно сигналы пуска, ошибки, опережения, отставания, постоянных искажений и сброса. 2. Устройство по п. 1, отличающееся тем, что формирователь зоны искажении содержит второй дополнительный триггер, пятый и шестой элементы И, первый и второй дополнительные инверторь;, и третий элемент ИЛИ, при этом первый и второй выХОДЫ второго дополнительного триггера соединены с первыми входами соответственно пятого и шестого элементов И, вторые входы которых соединены соответственно с выходами первого и второго дополнительных инверторов, причем вход второго дополнительного инвертора, который объединен с третьим входом пятого элемента И и с первым входом второго дополнительного триггера, является первым входом формирователя зоны искажений, вторым входом которого является третий вход шестого элемента И, который объединен с входом первого дополнительного триггера, выход которого соединен с вторым входом второго дополнительного триггера, а выход формирователя зоны искажений является выход третьего элемента ИЛИ, первый и второй входы которого соединены соответственно с выходами пятого и шестого элементов И. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 470928, кл. Н 04 L 3/00, 1973 прото

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения среднеквадратичного отклонения краевых искажений импульсов | 1979 |

|

SU860337A1 |

| Фазокорректирующее устройство с подстройкой частоты | 1980 |

|

SU882010A1 |

| Устройство для формированияиСпыТАТЕльНОгО TEKCTA | 1979 |

|

SU803118A1 |

| ДИСКРЕТНЫЙ ФАЗОРАЗНОСТНЫЙ МАНИПУЛЯТОР | 2017 |

|

RU2666228C1 |

| Датчик испытательных текстов | 1988 |

|

SU1571786A1 |

| Устройство для приема и передачииНфОРМАции | 1979 |

|

SU809294A1 |

| Устройство для определения средне-КВАдРАТичЕСКОгО ОТКлОНЕНия Слу-чАйНОй ВЕличиНы | 1979 |

|

SU849230A1 |

| ТРЕХЧАСТОТНЫЙ МОДУЛЯТОР | 2003 |

|

RU2239939C1 |

| Устройство для индикации | 1990 |

|

SU1795513A1 |

| Устройство поэлементной синхронизации | 1985 |

|

SU1319301A1 |

Авторы

Даты

1981-03-23—Публикация

1979-05-16—Подача