54) ДЕЛИТЕЛЬ ЧАСТОТЫ ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь числоимпульсного кода в код семисегментного индикатора | 1983 |

|

SU1105885A1 |

| Измеритель временных интервалов | 1982 |

|

SU1034012A1 |

| Система динамической синхронизации и корректировки рангов объектов в АСУ | 1985 |

|

SU1305630A1 |

| Пересчетная декада | 1983 |

|

SU1112574A1 |

| Устройство для определения направления и угла поворота вращающегося объекта | 1991 |

|

SU1786441A1 |

| Устройство генерации импульсов управления шаговым двигателем с электронной коррекцией | 1991 |

|

SU1829022A1 |

| Реверсивный счетчик импульсов | 1982 |

|

SU1042185A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2009 |

|

RU2417537C1 |

| Двухканальный программируемый генератор импульсов | 1991 |

|

SU1800594A1 |

| Преобразователь синусно-косинусных сигналов в последовательность импульсов | 1985 |

|

SU1309310A1 |

1

Изобретение относится к автоматике и может использоваться при постро ении цифровых синтезаторов частоты, а также -в формирователях временных интервалов.

Известен делитель частоты импульсов, содержащий счетчик, выходы которого соединены с дешифратором, выход Которого соединен с первыми входами первого и второго элементов И, вторые входы которых соединены со входом делителя частоты импульсов, выход которого соединен с выходом первого элемента И и цепью сброса счетчика, счетный вход которого соединен с выходом второго элемента И LlJ.

Недостатки этого делителя частоты импульсов - относительно низкая надежность и сложность изменения коэффициента пересчета.

Известен также делитель частоты импульсов, содержащий счетчики с дешифрацией состояния и элемент И, входы которого соединены с выходами дешифрации состояния десятичных счетчиков с дешифрацией состояния, а выход элемента И соединен с входами сброса десятичных счетчиков с дешифрацией состояния, выход переноса каждого десятичного счетчика с дешифрацией состояния соединен со счетным входом следующего десятичного счетчика с дешифрацией состояния 2.

Недостатком этого делителя частоты импульсов является относительно низкая достоверность функционирования .

Целью изобретения является повышение достоверности функционирования.

to

Поставленная цель достигается тем, что в делитель частоты импульсов, содержащий десятичные счетчики с дешифрацией состояния и элемент И, входы которого соединены с выходами ,

15 дешифрации состояния десятичных Счетчиков с дешифрацией состояния, а выход элемента И соединен со входами сброса десятичных счетчиков с дешифрацией состояния, выход переноса каж20дого десятичного счетчика с дешифрацией состояния соединен со счетным входом следутэщего десятичного счетчика с дешифрацией состояния введены вспомогательный элемент Н и инвертор,

25 выход которого соединен с дополнительны; входом элемента И и счетн м входом первого десятичного счетчика с деилифрациеп состояния, а вход инвертора соединен со входом делителя

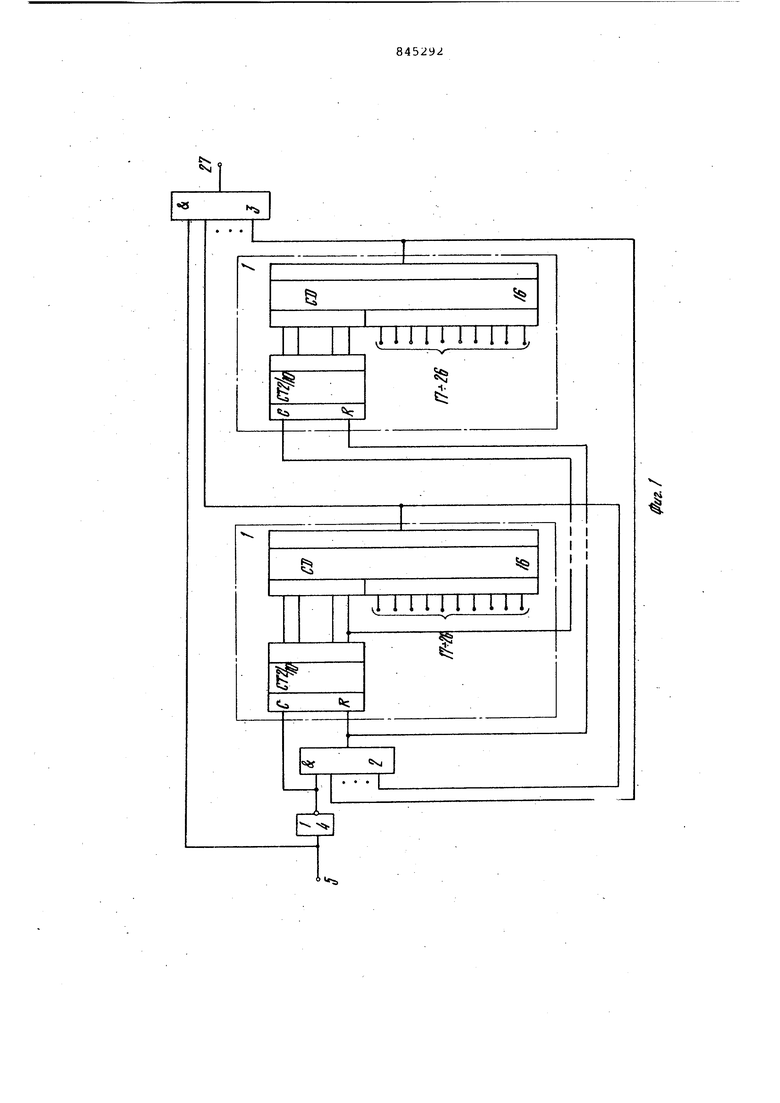

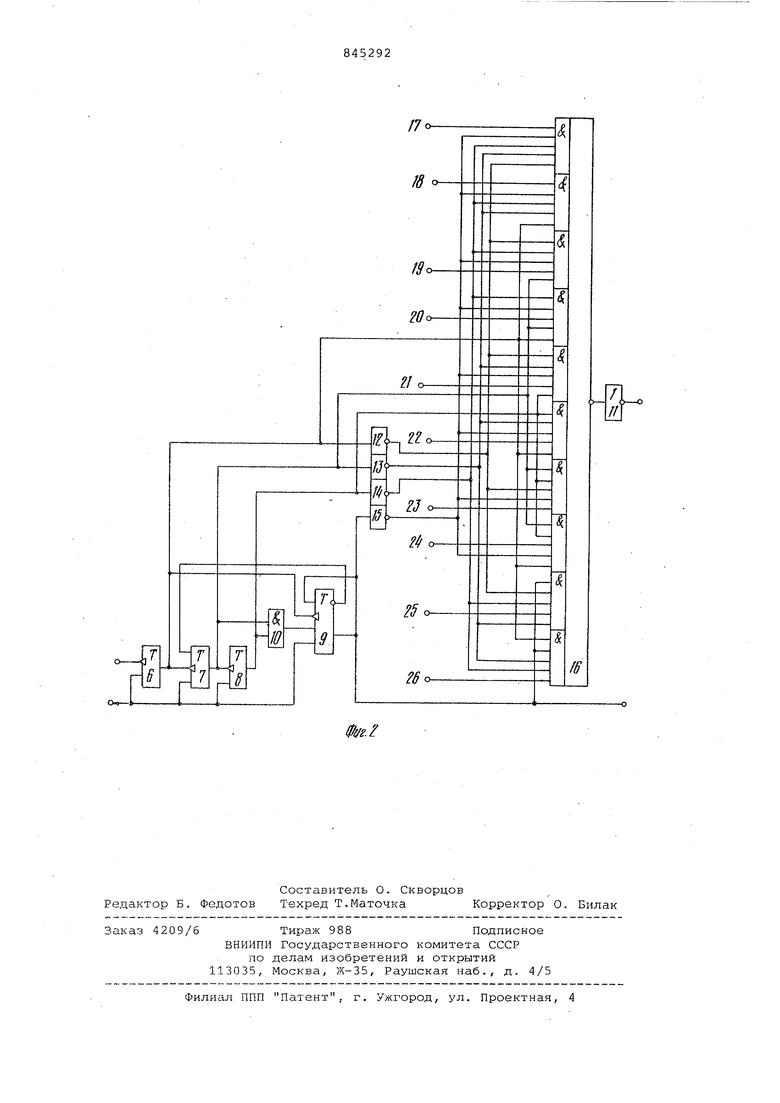

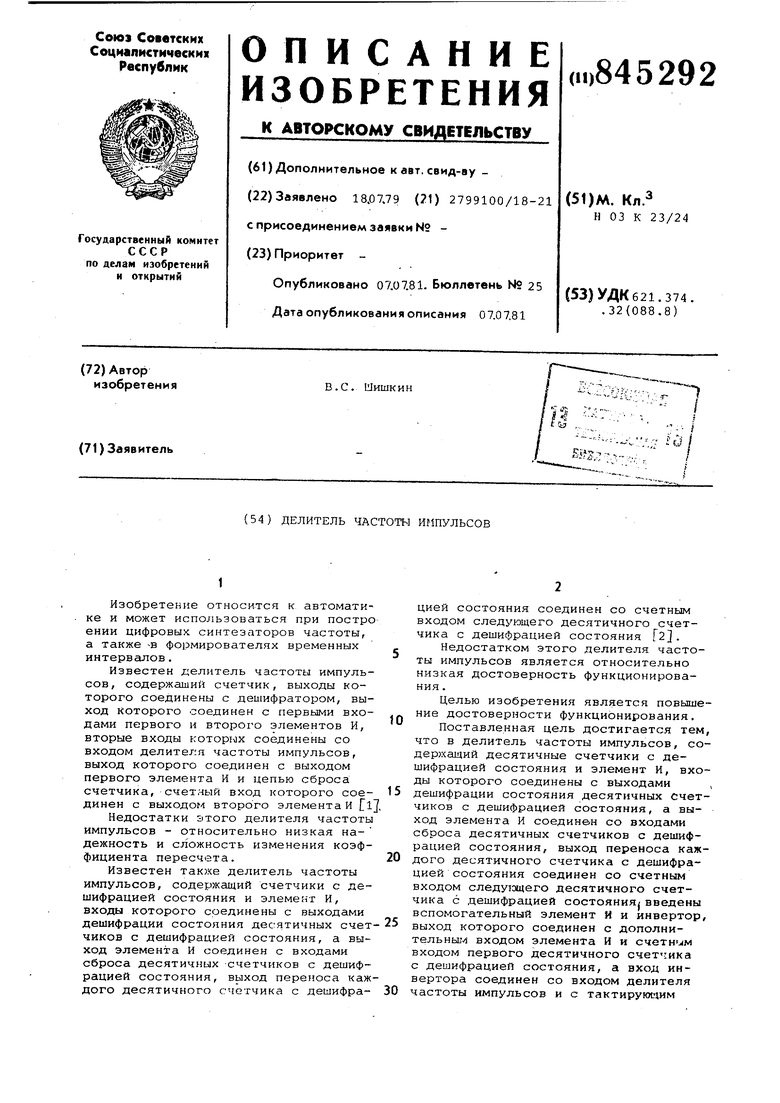

30 частоты импульсов и с тактируюиим входом вспомогательного элемента И, остальные входы которого соединены с выходами дешифрации состояния деся тичных счетчиков с дешифрацией состо ния. Каждый десятичный счетчик с дешифрацией состояния содержит, пер,вый, второй, третий и четвертый триггеры, двухвходовой элемент И, пять инверторов и элемент И-ИЛИ-Н выход которого соединен со входом первого инвертора, выход которого соединен с выходом дешифрации состояния этого десятичного счетчика с дешифрацией состояния, вход сброса которого соединен со вхо дом сброса триггеров; счетные входы второго и третьего и первый управляющий вход четвертого триггеров соединены соответственно с прямыми выхо дами первого, второго триггеров и выходом двухвходо вого элемента И, вх ды которого соединены с прямыми выходами второго и третьего триггеров. счетный и второй управляющий входы четвертого триггера соединены соответственно с прямым выходом первого триггера и прямым выходом четвертого триггера, инверсный выход которого соединен с управляющим входом второго триггера; прямые выходы первого, второго, третьего и четвертого триггеров соединены с входами соответственно второго, третьего, четвертог пятого инверторов; прямой выход чет вертого триггера соединен с первыми входами первой и второй групп входов по И элемента И-ИЛИ-НЕ и выхддом переноса десятичного счетчика с дешифрацией состояния, счетный вход кото рого соединен с счетным входом перво го триггера ) прямой выход первого три гера соединен с первыми входами тре ей, пятой, седьмой и девятой групп входов по И элемента И-ИЛИ-НЕ и вто рым входом первой группы входов по И элемента И-ИЛИ-НЕ) прямой выход вто рого триггера соединен с первыми вх дами четвертой и восьмой и вторыми входами третьей и седьмой групп вхо дов по И элемента И-ИЛИ-НЕ; прямой выход третьего триггера соединен с первым входом входом шестой, вторым входами четвертой и пятой и третьим входрм третьей групп входов по И эл мента И-ИЛИ-НЕ) выход второго инвер тора соединен с входами вос мой я десятой, вторыми входами второй и шестой и третьим входом четве той групп входов по И элемента И-ИЛИ-НЕ; выход третьего инвертора соединен с третьими входами первой, второй, пятой и шестой и вторыми входами девятой и десятой групп вхо дов по И элемента И-ИЛИ-НЕ) выход четвертого инвертора соединен с чет вертыми входами первой и второй и третьими входами седьмой, восьмой, девятой и десятой групп входов по и элемента И-ИЛИ-НЕ; выход пятого инвертора соединен с четвертыми входами третьей, четвертой, пятой, шестой седьмой, восьмой, девятой и десятой групп входов по И элемента И-ИЛИ-НЕ; пятые входы всех групп входов по И элемента И-ИЛИ-НЕ соединены с соответствующими шинами. Структурная схема делителя частоты импульсов показана на фиг. 1. На фиг. 2 показана структурная схема десятичного счетчика с дешифрацией состояний . Делитель частоты импульсов содержит десятичные счетчики 1 с дешифрацией состояния, элемент И 2, вспомогательный элемент И 3 и инвертор 4. Входы элемента И 2 соединены с выходами деформации состояния счетчиков 1, а выход элемента И 2 соединен с входами сброса счетчиков. Выход переноса каждого счетчика соединен со / счетным входом следующего, выход инвертора 4 соединен с дополнительньлм входом элемента И 2 и со счетным входом первого счетчика, а вход инвертора 4 - с входом 5 делителя частоты импульсов и с тактирующим входом вспомогательного элемента И 3, остальные входы которого соединены с выходами дешифрации состояния счетчиков. Каждый десятичный счетчик 1 содержит триггеры 6-9, двухвходовый счетчик И 10, пять инверторов 11-15 и элемент И-ИЛИ-НЕ 16, выход которого соединен с входом инвертора 11. Его выход соединен с выходом дешифрации состояния этого счетчика, вход сброса которого соединен со входами сброса триггеров 6-9, счетные входы триггеров 7 и 8 и первый управляющий вход триггера 9 соединены соответственно с прямыми выходами триггеров 6 и 7 и выходом двухвходового элемента И 10, входы которого соеди- . нены с прямыми выходами триггеров 7 и.8, счетный и второй управляющий входы четвертого триггера 9 соединены соответственно с прямым выходом триггера 6 и прямым выходом триггера 9, инверсный выход которого соединен с управляющим входом триггера 7. Прямые выходы триггеров 6-9 соединены с входами соответственно инверторов 12-15. Прямой выход триггера 9 соединен с первыми входами первой и второй групп входов по И элемента И-ИЛИ-НЕ 16 И выходом переноса счетчика, счетный вход которого соединен со счетным входом триггера 6. Прямой выход триггера 6 соединен с первыми входами третьей, пятой, седьмой и девятой групп входов по И элемента И-ИЛИ-НЕ 16 и вторым входом первой группы входов по И элемента И-ИЛИ-НЕ 16. Прямой выход триггера 7 соединен с первыми входамичетвертой и восьмой и вторыми входами третьей и седьмой групп входов и по И элемента И-ИЛИ-НЕ 16. Прямой выход триг гера 8 соединен с первым входом шестой, вторыми входами четвертой и пятой и третьим входом третьей групп входо по И элемента И-ИЛИ-НЕ 16. Выход второго инвертора 12 соединен с первыми входами десятой, вторыми вхо дами второй и шестой и восьмой и третьим входом четвертой групп входов по И элемента Н-ИЛИ-НЕ 16, выход инвертора 13 - с третьими входами ,лервой, второй, пятой и шестой и вто рыми входами девятой и десятой групп входов по И элемента И-ИЛИ-НЕ 16. Вы ход четвертого инвертора 14 связан с четвертыми входами первой и второй и третьими входами седьмой, восьмой, девятой и десятой групп входов по И элементаИ-ИЛИ-НЕ 16. Выход инвертора 15 соединен с четвертыми входами третьей, четвертой, пятой, шестой, седьмой, восьмой, девятой и десятой групп входов.по И элемента И-ИЛИ-НЕ 16, пятые входы всех групп входов по И элемента И-ИЛИ-НЕ 16 соединены с соответствующими управляющими шинами 17-26. Элемент И-ИЛИ-НЕ 16 выполняет функции мультиплексора. Работает делитель частоты импульсов следующим образом Импульсная последовательность FO (высокий уровень входного импульса) с периодом следования Тд и длительностью импульса высокого уровня tр непрерывно поступает на вход элемент -И 3 и через инвертор 4 - на счетный вход счетчика 1 и на вход элемента И 2. Двоично-десятичный счетчик работа ет в коде 8-4-2-1. Выходы триггеров 6-9 соединены с кодирующими входами мультиплексора 16 данного счетчика с соответствующими двоичными весами. Сигнал А на выходе появляется вы соким уровнем в моменты времени, определяемые логическим уравнением °-.Игде - символ, обозначакадий логи ческое произведение выходны сигналов мультиплексоров каскадов деления; выходной сигнал мультиплексора. Выходной сигнал п-ного мультиплек сора определяется логическим уравнениемУ 5 п-х;„ С1, С2, С4, С8, n- n-i где Р„. импульсный сигнал, поступающий на вход п-ного сче чика. Период следования сигнала св зан с периодом следования входной им пульсной последовательности соотношениемСимвол обозначает логическое жение десяти конституент едиы. Символ S обозначает конкретный ормационный вход мультиплексора, i 0,1,...,9. Символ fCl, С2, С4, С8 обозает двоичный вектор на кодируювходах n-HDro мультиплексора, чем код двоичногр вектора соответует информационному входу i п-ного ьтиплексора. Импульс обнуления выого уровня формируется на выходе мента И 2 и определяется логичесуравнениемУЧ - символ, обозначающий логи - ческое произведение двоичных аргументов А,.. Число, выражакнцее любой целочисленкоэффициент деления, представляя в десятичной системе счисления аскрытой форме в виде К.Кед,..-,о4..., Kg., Кд ... - коэффициенты от О до 9, стоящие соответственно в раз делах единиц, десятков и т.д. десятичного числа, выражающего коэффициент деления. Структура построения и коэффициент ения ДПКД связаны соотношением ..o-.s..,oV....s.. . Требуемый коэффициент деления ДПКД 1,...,CD ) устанавливается подачей окого уровня на одну из шин мульлексора каждого каскада давления. Время задержки выходного импульса окого уровня А делителя относиьно входного импульса высокого вня FO определяется по формуле з.. . эи -время задержки выходного импульса высокого уровня; -время задержки инвертора 4 -время задержки одного счетчика; -номер каскада деления, коэффициент которого ,э О начиная с первого касксща; -время задержки одного мультиплексора; -время задерж1 и элемента И 3. Предельная частота использования делителя определяется выражением ,, 1 .,.„ивЛп-Ьз..гл,.«3 где п - число Каскадов деления. Предложенное устройство позволит на своем выходе 27 получить импульсы синхронные по времени и равные по длительности входным импульсам, что обеспечивает надежность функционирования. .Формула изобретения 1. Делитель частоты импульсов, со держащий десятичные счетчики, с дешиф рацией состояния и элемент И, входы которого соединены с выходами дешифрации состояния десятичных счетчиков с дешифрацией состояния, а вы ход элемента И соединен с входами сброса десятичных счетчиков с дешифрацией состояния, выход переноса каждого десятичного счетчика с дешифрацией состояния соединен со сче ным входом следующего десятичного счетчика с дешифрацией состояния, отличающи йся тем, что, с целью повышения достоверности фун цион1 рования, в .него введены вспомо гательный элемент И и инвертор, вых которого соединен с дополнительным входом элемента И и счетным входом первого десятичного счетчика с деши рацией состояния, а вход инвертора соединен с входом делителя частоты импульсов и тактирующим входом вспо могательного элемента И, остальные входы которого соединены с выходами дешифрации состояния десятичных сче чиков с дешифрацией состояния. 2. Делитель по п. 1, отличающийся тем, что каждый де сятичный счетчик с дешифрацией сост ния содержит первый, второй, третий и четвертый триггеры, двухвходовый элемент И, пять инверторов и элемен И-ИЛИ-НЕ, выход которогосоединен с входом первого инвертора, выход которого соединен с выходом дешифрации состояния этого десятичного сче чика с дешифрацией состояния, вход сброса которого соединен с входами сброса триггеров, с -1етные входы вто го Ц третьего и первый управляющий вход четвертого триггеров соединены соответственно с прямыми выходами п вого, второго .триггеров и выходом двух входового элемента И, входы которог соединены с прямыми выходами второго и третьего триггеров, счетный и второй управляющий входы четвертого триггера соединены соответственно с прямым выходом первого триггера и прямым выходом четвертого триггера, инверсный выход которого соединен с управляющим входом второго триггера, прямые выходы первого, второго, третьего и четвертого триггеров соединены с входами соответственно второго, третьего, четвертого, пятого инверторов , прямой выход четвертого триггера соединен с первыми входами первой и второй групп входов по И элемента И-ИЛИ-НЕ и выходом переноса десятичного счетчика с дешифрацией состояния, счетный вход которого соединен с счетным входом первого триггера,прямой выход первого триггера соединен с первыми входами третьей, пятой, седьмой и девятой групп входов по И элемента И-ИЛИ-НЕ и вторым входом первой группы входов по И элемента И-ИЛИ-НЕ, прямой выход второго триггера соединен с первыми входами четвертой и восьмой и вторыми входами третьей и седьмой групп входов по И элемента И-ИЛИ-НЕ, прямой выход треть его триггера соединен с первым входом шестой, вторыми входами четвертой и пятой и третьим входом третьей групп входов по И элемента И-ИЛИ-НЕ, выход второго инвертора соединен с первыми входами восьмой и десятой, вторь1ми входами второй и шестой и Третьим входом четвертой групп входов по И элемента И-ИЛИ-НЕ, выход третьего инвертора соединен с третьиими входами, первой, второй, пятой, шестой и вторыми входами девятой и десятой групп входов по И элемента И-ИЛИ-НЕ, выход четвертого инвертора соединен с четвертыми входами первой и второй и третьими входами седьмой, восьмой, девятой и десятой групп входов по И элемента И-ИЛИ-НЕ выход пятого инвертора соединен с четвертыми входами третьей, четвертой, пятой, шестой, седьмой, восьмой, девятой и десятой групп входов по И элемента И-ИЛИ-НЕ, пятые входы всех групп входов по И элемента И-ИЛИ-НЕ соединены с соответствующими управляющими шинами. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство ССОР № 513507, кл. Н 03 К 23/00, 1974. 2.Friedrich Arnolds. Electroniche Medtechnik, Berlin, Union, c. 277, рис. 18.1. 1976 (прототип).

а

J1111 11 1 IT

s

j 11 ill 1 m;

V I

Авторы

Даты

1981-07-07—Публикация

1979-07-18—Подача