(54) СИНТЕЗАТОР ЧАСТОТ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой синтезатор частоты с частотной модуляцией | 1989 |

|

SU1771068A1 |

| Частотный компаратор | 1981 |

|

SU1023630A1 |

| Устройство для автоматического переключения однофазных нагрузок в низковольтных распределительных сетях | 1981 |

|

SU1026234A1 |

| Устройство для измерения частоты частотно-модулированного телевизионного сигнала | 1983 |

|

SU1223157A1 |

| Устройство для коррекции нелинейности | 1982 |

|

SU1056228A1 |

| Устройство автоматической подстройки линейного закона частотной модуляции | 1984 |

|

SU1218463A1 |

| Синтезатор частот | 1974 |

|

SU486450A1 |

| Манипулятор частоты без разрыва фазы | 1987 |

|

SU1515384A1 |

| Устройство для регулирования скорости электродвигателя | 1984 |

|

SU1267375A1 |

| Устройство автоматической подстройки частоты | 1987 |

|

SU1539999A2 |

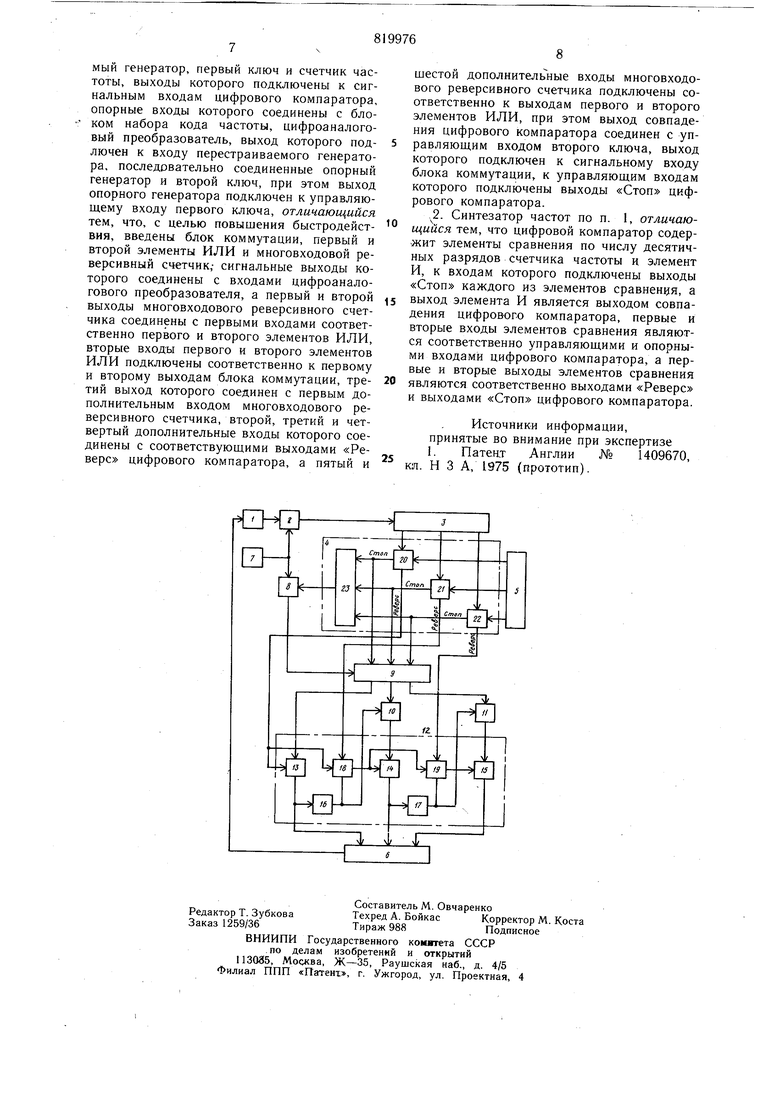

Изобретение относится к радиотехнике и может быть использовано, например, в технике связи в качестве гетеродина приемника или возбудителя передатчика. Известен синтезатор частот, содержащий последовательно соединенные перестраиваемый генератор, первый ключ и счетчик частоты, выходы которого подключень{ к сигнальным входам цифрового компаратора, опорные входы которого соединены с блоком набора кода частоты, цифроаналоговый преобразователь, выход которого подключен к входу перестраиваемого генератора, последовательно соединенные опорный генератор и второй ключ, при этом выход опорного генератора подключен к управляющему входу первого ключа 1. Однако такой синтезатор частот облагает высоким быстродействием в случае необходимости повышения точности настройки при малом шаге перестройки. Целью изобретения является повышение быстродействия. Для этого в синтезатор частот, содержащий последовательно соединенные перестраиваемый генератор, первый ключ и счетчик частоты, выходы которого подключены К сигнальным входам цифрового компаратора, опорные входы которого соединены с блоком набора кода частоты цифроаналоговый преобразователь, выход которого подключен к входу перестраиваемого генератора, последовательно соединенные опорный генератор и второй ключ, при этом выход опорного генератора подключен к управляющему входу первого ключа, введены блок коммутации, первый и второй элементы ИЛИ и многовходовой реверсивный счетчик, сигнальные выходы которого соединены с входами цифроаналогового преобразователя, а первый и второй выходы многовходового реверсивного счетчика соединены с первыми входами соответственно первого и второго элементов ИЛИ, вторые входы первого и второго элементов ИЛИ подключены соответственно к первому и второму выходам блока коммутации, третий выход которого соединен с первым дополнительным входом многовходового реверсивного счетчика, второй, третий и четвертый дополнительные входы которого соединены с соответствующими выходами «Реверс цифрового компаратора, а пятый и щестой дополнительные входы многовходового реверсивного счетчика подключены соответственно к выходам первого и второго элементов ИЛИ, при этом выход совпадения цифрового компаратора соединен с управляющим .входом второго ключа, выход которого подключен к сигнальному входу блока коммутации, к управляющим входам которого подключены выходы «Стоп цифрового компаратора. Кроме того, цифровой компаратор содержит элементы ср нения по числу десятичных разрядов счетчика частоты и элемент И, к входам которого подключены выходы «Стоп каждого из элементов сравнения, а выход элемента И является выходом совпадения цифрового компаратора, первые и вторые входы элементов сравнения являются соответственно управляющими и опорными входами цифрового -компаратора, а первые и вторые выходы элементов сравнения являются соответственно выходами «Реверс и выходами «Стоп цифрового компаратора. На чертеже приведена функциональная схема предлагаемого устройства. Синтезатор частот содержит перестраиваемый генератор 1, первый ключ 2, счетчик частоты 3, цифровой компаратор 4, блок 5 набора кода частоты, цифроаналоговый преобразователь (ЦАП) 6, опорный генератор 7, второй ключ 8, блок 9 коммутации, первый и второй элементы ИЛИ 10, 11, многовходовый реверсивный счетчик 12, соетоящий из реверсивных счетчиков 13, 14, 15, схем 16, 17 переноса- и схем 18, 19 коммутации реверса, а также элементы сравнения 20, 21, 22, элемент И 23, входящих в состав цифрового компаратора 4. Синтезатор частот работает следующим образом. Колебания перестраиваемого генератора 1 подаются на сигнальный вход ключа 2. С опорного генератора 7 на управляющий вход ключа 2 поступают импульсы, открывающие ключ 2 на время мерного интервала (эталонное время). В результате на вход счетчика частоты 3 поступает пачка импульсов, число импульсов в которой пропорционально частоте перестраиваемого генератора 1, а после каждого цикла счета на выходах счетчика частоты 3 записывается код, отображающий среднее значениее частоты генератора 1 за эталонное время счета. Затем с помощью элементов сравнения 20, 21, 22 производится поразрядное сравнение кода частоты перестраиваемого генератора 1 с кодом частоты, значение которой установлено на блоке 5 набора кода частоты. Для этой цели с соответству1ощего выхода счетчика частоты 3 на первый вход каждого элемента сравнения 20, 21, 22 подается код соответствующего разряда частоты перестраиваемого генератора 1, а на второй вход - аналогичный код с выхода блока 5 набора частоты. В результате на выходах элементов 20, 21, 22 появляется информация о рассогласовании в каждом разряде (если таковое имеется) и о знаке этого рассогласования. Допустим, что рассогласование имеет, место во всех разрядах. Тогда с выхода «Стоп элемента сравнения 22 старщего разряда логический «О через элемент И 23 поступит на управляющий вход второго ключа 8 и откроет его. Это приводит к подаче эталонного импульса на сигнальный вход блока 9 коммутации. Блок 9 коммутации работает таким образом, что пропускает импульс, приходящий с ключа 8 на какой-то один из своих выходов в зависимости от кода на выходах «Стоп элемента сравнения. При рассогласовании в старшем разряде импульс с выхода второго ключа 8 проходит на соответствующий старшему разряду выход блока 9 коммутации и через элемент ИЛИ 11 на счетный вход реверсивного счетчика 15. В то же время выход «Реверс элемента сравнения 22 старщего разряда через схему коммутации 19 реверса подключен к знаковому входу реверсивного счетчика 15. Таким образом, в зависимости от соотношения кода частоты перестраиваемого генератора 1 и кода блока 5 набора частоты в данный момент времени г1од действием эталонного импульса, пришедшего с блока 9 коммутации и информации, поступающей с выхода «Реверс элемента сравнения 22, реверсивный счетчик 15 перейдет либо в состояние /С+1, либо в состояние /С-1 (К - состояние счетчика 15 до пocfyплeния имлульса на счетный вход), что приведет к изменению кода старших разрядов ЦАП 6, изменению выходного напряжения преобразователя и в конечном счете к изменению частоты генератора 1. Процесс будет протекать до тех пор, пока не исчезнет сигнал рассогласования в старшем разряде. Когда это произойдет, путем перестройки генератора 1 на выходе «Стоп элемента сравнения 22 появится логическая «1. Такое изменение кода на управляющих входах блока 9 коммутации приводит к тому, что импульсы с выхода второго ключа 8 (ключ этот, как следует из схемы, остается открытым, пока существует сигнал рассогласования в любом из разрядов) начинает поступать на другой выход блока 9 коммутации, а именно на выход, подключенный через первый элемент ИЛИ 10 к счетному входу реверсивного счетчика. 1.4. Знаковый вход последнего в этот момент времени через схему коммутации реверса 18 соединен с выходом «Реверс элемента сравнения 21. Таким образом, пока на выходе «Стоп элемента сравнения 21 будет существовать сигнал рассогласования, будет происходить изменение кода соответствующих счетчиков 14, а следовательно, на управляющий вход перестраиваемого генератора 1 будет действовать изменяющееся ступенчатое напряжение. Величина отдельной ступеньки этого напряжения будет значительно меньще аналогичной ступени при обработке рассогласования в старшем разряде, так как в последнем случае имеет место изменение кода более младших разрядов ЦАП. При приближении к точке настройки в синтезаторе происходит автоматическое уменьшение скорости перестройки частоть1, что позволяет повысить точность настройки перестраиваемого генератора Ц Когда рассогласование и в этом разряде будет скомпенсировано, на выходе «Стоп элемента сравнения 21 появится логическая «1. После этого импульсы с входа блока 9 коммутации будут, поступать на выход, соответствующий самому младшему разряду, а с него непосредственно на счетный вход реверсивного счетчика 13. Знаковый вход этого счетчика также непосредственно подключен к выходу «Реверс элемента сравнения 20. Выход реверсивного счетчика 13 подсоединен к младшим разрядам ЦАП 6 и поэтому каждый импульс, приходящий на счетный вход счетчика 13, вызывает такой скачок напряжения на управляющем входе генератора 1, который приводит к перестройке частоты генератора на величину, не превыщающую цены деления счетчика частоты 3. Когда сигнал рассогласования исчезает, в младшем разряде на все входы элемента И 23 поступают логические «1. Вследствие этого логическая «1, подаваемая с выхода элемента И 23, закрывает второй ключ 8, прекращая подачу эталонных импульсов на вход блока 9 коммутации и фиксируя тем самым состояние реверсивных счетчиков 13, 14, 15. В результате этого код на входе ЦАП 6, а следовательно, и управляющее напряжение генератора 1 становятся такими, что выполняется равенство кодов частот перестраиваемого генератора 1 и блока 5 набора кода частоты с точностью, определяемой точностью счетчика частоты 3, Далее синтезатор из режима настройки на частоту, заданную блоком 5 набора кода частоты, переходит в режим стабилизации этой частоты, которьш протекает следующим образом. Если спустя некоторое время частота перестраиваемого генератора 1 увеличилась на величину Л {, большую, чем цена деления младшего разряда счетчика частоты 3, то на, выходах элементов сравнения 20, 21, 22 появится информация о рассогласовании в младшем разряде. В этом случае, как было изложено, второй ключ 8 откроется и импульсы с опорного генератора 7 через блок 9 коммутации начнут поступать на реверсивный счетчик 13. При этим на знаковый вход счетчика 13 с выхода «Реверс элемента сравнения 20 будет подана команда перейти в режим вычитания. Изменение кода приведет к тому, что управляющее напряжение перестраиваемого генератора 1, а следовательно, и его частота будет уменьшаться до тех пор, пока не восстановится нарушенное соответствие, т.е. пока частота генератора 1 опять не станет равной частоте, значение кода которой набрано на блоке 5 набора кода частоты. Если же частота генератора 1 под влиянием дестабилизирующих факторов уменьщается, то процесс подстройки генератора протекает аналогично, но в этом случае команда с выхода «Реверс элементов сравнения 20 переводит реверсивный счетчик 13 в режим сложения, и управляющее напряжение генератора 1 вместе с частотой ступенчато нарастает. Чтобы полосу удержания такой системы автоподстройки сделать достаточно большой (а она определяется объемом реверсивного счетчика 13), выходной код реверсивного счетчика 13 помимо ЦАП 6 подается на вход схемы переноса 16. Когда реверсивный счетчик переходит сразу же из состояния полного заполнения в нулевое или наоборот, на выходе схемы переноса 16 вырабатывается импульс переноса, который, поступив на управляюший вход схемы 18 коммутации реверса, подключает на время своего действия выход «Реверс1 элемента сравнения 20 к знаковому входу реверсивного счетчика 14, а также через элемент ИЛИ 10 поступает на счетный вход реверсивного счетчика 14. Итогом всех этих процессов является одновременно (т.е. во время срабатывания триггеров реверсивного счетчика 13 от фронта эталонного импульса, приходящего с блока 9 коммутации) изменение состояния сразу двух реверсивных счетчиков 13 и 14, в результате чего код на входах ЦАП меняется так, что на его выходе напряжение получает приращение, равное по .величине приращению, получаемому при изменении состояния реверсивного счетчика 13 на единицу. При этом важно то, что реверсивный счетчик 13 после этого оказывается свободным для заполнения (или полным для считывания) импульсами, поступающими на его счетный вход. Схема переноса 17 и схема 19 коммутации реверса работают соверщенно аналогично схемам 16 и 18 в случае полного (или нулевого) заполнения реверсивного счетчика 14. Предлагаемый синтезатор частот гТозьоляет получить 1000 фиксированных рабочих частот с щагом перестройки, равным- цене деления младшего разряда счетчика частоты, и существенный выигрыш в быстродействии по сравнению с прототипом. Формула изобретения 1. Синтезатор частот, содержащий последовательно соединенные перестраиваемыи генератор, первый ключ и счетчик частоты, выходы которого подключены к сигнальным входам цифрового компаратора, опорные входы которого соединены с блоком набора кода частоты, цифроаналоговый преобразователь, выход которого подлючен к входу перестраиваемого генератора, последовательно соединенные опорный генератор и второй ключ, при этом выход опорного генератора подключен к управляющему входу первого ключа, отличающийся тем, что, с целью повышения быстродейстВИЯ, введены блок коммутации, первый и второй элементы ИЛИ и многовходовой реверсивный счетчик,- сигнальные выходы которого соединены с входами цифроаналогового преобразователя, а первый и второй выходы многовходового реверсивного счетчика соединены с первыми входами соответственно первого и второго элементов ИЛИ, вторые входы первого и второго элементов ИЛИ подключены соответственно к первому и второму выходам блока коммутации, третий выход которого соединен с первым дополнительным входом многовходового реверсивного счетчика, второй, третий и четвертый дополнительные входы которого соединены с соответствующими выходами «Реверс цифрового компаратора, а пятый и щестой дополнительные входы многовходового реверсивного счетчика подключены соответственно к выходам первого и второго элементов ИЛИ, при этом выход совпадения цифрового компаратора соединен с управляющим входом второго ключа, выход которого подключен к сигнальному входу блока коммутации, к управляющим входам которого подключены выходы «Стоп цифрового компаратора. 2. Синтезатор частот по п. 1, отличающийся тем, что цифровой компаратор содержит элементы сравнения по числу десятичных разрядов счетчика частоты и элемент И, к входам которого подключены выходы «Стоп каждого из элементов сравнения, а выход элемента И является выходом совпадения цифрового компаратора, первые и вторые входы элементов сравнения являются соответственно управляющими и опорными входами цифрового компаратора, а первые и вторые выходы элементов сравнения являются соответственно выходами «Реверс и выходами «Стоп цифрового компаратора. Источники информации, принятые во внимание при экспертизе 1. Патент Англии № 1409670, кл. Н 3 А, 1975 (прототип).

Авторы

Даты

1981-04-07—Публикация

1977-04-06—Подача