(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЭЛЕМЕНТОВ ЗАПОМИНАЮЩЕЙ МАТРИЩ

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ИЗМЕРИТЕЛЬ СЕРИИ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 1968 |

|

SU208038A1 |

| Электронные часы с фиксацией и документированием времени | 1988 |

|

SU1552147A1 |

| Голографическое постоянное запоминающее устройство | 1990 |

|

SU1725258A1 |

| Счетное устройство, сохраняющее информацию при отключении питания | 1987 |

|

SU1492476A1 |

| Репрограммируемое постоянное запоминающее устройство | 1989 |

|

SU1695384A1 |

| УСТРОЙСТВО ДЛЯ НАКОПЛЕНИЯ И ОБРАБОТКИ ИНФОРМАЦИИ | 1973 |

|

SU384131A1 |

| Устройство для контроля амплитудно-частотных характеристик четырехполюсников | 1980 |

|

SU946003A1 |

| Ассоциативное запоминающее устройство | 1977 |

|

SU744728A1 |

| Запоминающее устройство | 1980 |

|

SU911614A1 |

| Устройство для контроля запоминающих матриц на магнитных пленках | 1979 |

|

SU773736A1 |

f

Изобретение относится к запоминающим устройствам.

Известны устройства для контроля элементов запоминающей матрицы, содержащие формирователи управляющих сигналов, дешифраторы, счетчики,схему сравнения i} .

Недостатком этого устройства являются большие аппаратурные затраты. Наиболее близким техническим решением к предлагаемому является устройство для контроля элементов запоминающей матрицы, содержащее имитаторы ввода количества адресов и кода чисел, схему пуск-останов, схемы формирования кода адресов и кода чисел, схемы сравнения и счетчики.

Это устройство предназначено для контроля элементов ферритовой запоминающей матрицы 2j .

Однако это устройство является сложным и не обеспечивает достаточно точности контроля элементов запоминающей матрицы в случае если последняя выполнена из аморфных полупроводников, так как схема управления тако матрицей и методы контроля ее элементов существенно отличаются от таковых для ферритовой запоминающей матрицы.

Цель изобретения - упрощение устройства и повышение точности контроля..

Поставленная цель достигается тем, что в устройство дл5 контроля элементов запоминающей матрицы, содержащее группы ключей, дешифраторы, первый, второй и третий счетчики, генератор импульсов, первый формирователь импульсов, блок согласования, блок считывания и обнаружения неисправностей, элемент И, причем одни из входов ключей первой группы соединены соответственно с выходами первого дешифратора и блока, согласования,одни из выходов ключей первой группы являются одними из (выходов устройства и входами устройства, выходы ключей второй группы являются другими выходами устройства, другие выходы ключей первой группы соединены со входами блока считывания и обнаружения неисправностей, выход первого формирователя импульсов подключен ко входу блока согласования, выход которого соединен с одним из входов блока считывания и обнаружения неиспрарностей, входы ключей второй группы соединены с выходами второго дешифра.тора, входы первого и второго деишфраторов подключены соответственно к выходу второго счетчика соответственно и одному из выходов третьего счетчика, другой выход которого соединен со входом второго счетчика, введены четвертый счетчик, первый и второй триггеры, второй формирователь импульсов, причем выход генератора импульсов подключен ко входу второго формирователя импульсов, один из выходов которого подключен ко входу первого формирователя импульсов и входу второго триггера, другой - к первому входу элемента И,второй вход которого соединен С выхо.дом блока считывания и обнаружения неисправностей, а выход - со входом первого счетчика, выход второго триггера подключен ко входу четвертого счетчика, выход которого соединен со входом третьего счетчика, выход первого счетчика соединен со входом первого триггера, выход которото подключен ко входу генератора импульсов. .

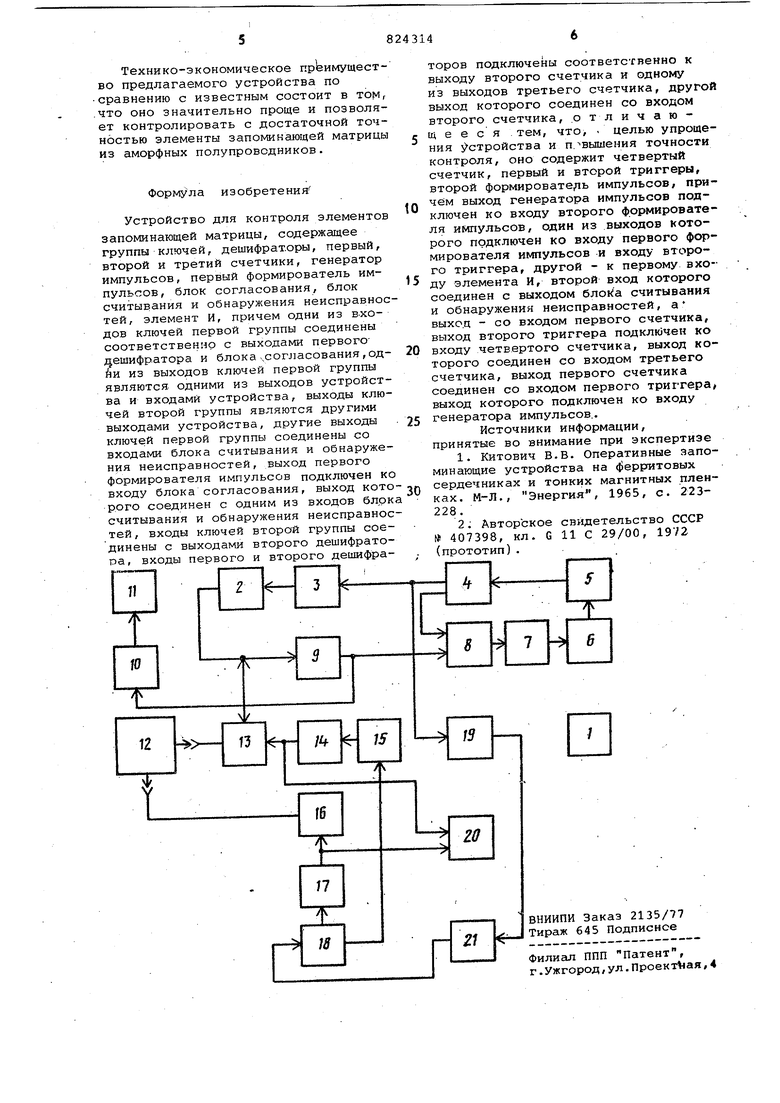

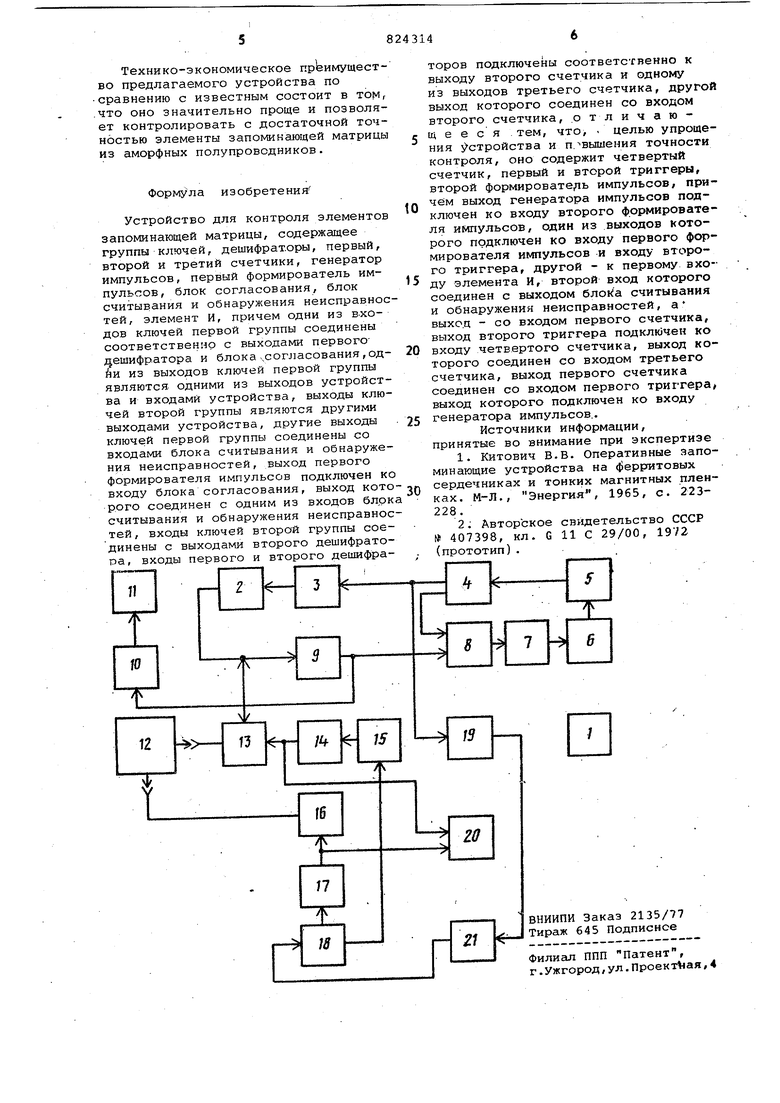

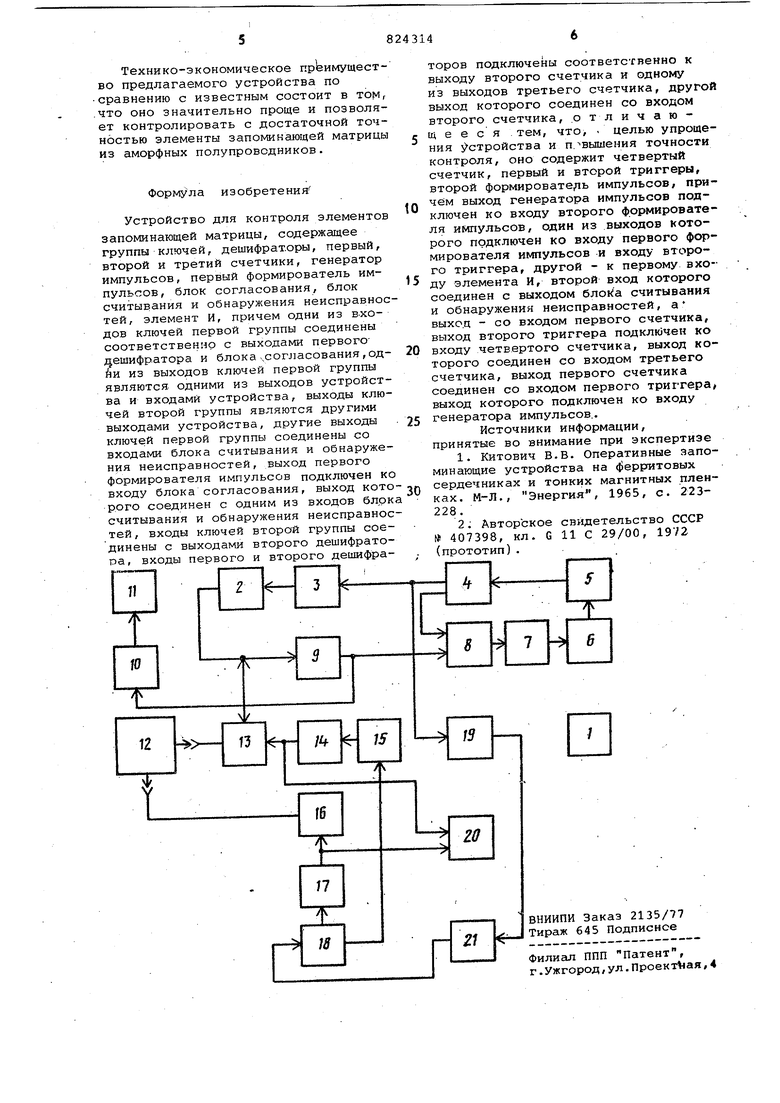

На чертеже изображена структурная схема устройства для контроля элементов запоминающей матрицы, изготовленной из аморфных полупроводников.

Устройство содержит блок 1 питания, блок 2 согласования, первый 3 и второй 4 формирователи импульсов, генератор 5 импульсов, первый триггер б, первый счетчик 7, служащий для подсчета числа циклов, элемент И 8, блок 9 считывания и обнаружения неисправностей, блок 10 управления пишущей машинкой, пишущую машинку 11. Входы и выходы устройства подключаются к выходам и входам контролируемой запоминающей матрицы 12 из аморфных полупроводников. Устройство также содержит первую группу ключей 13, первый дешифратор 14, второй счетчик 15, вторую группу ключей 16, второй дешифратор 17, третий счетчик 18, второй триггер 19, блок 20 индикации, четвертый счетчик 21, служащий для подсчета количества обращений к элементу запоминающей матрицы 12 при его тренировке.

.Выход генератора 5 подключен ко входу формирователя 4, один из выходов которого подключен ко входу формирователя 3 и входу триггера 19, другой. - к первому входу элемента И 8, второй вход которого соединен . с выходом блока 9, а выход - со входом счетчика 7. Выход триггера 19 подключен ко входу счетчика 21, выход которого соединен со входом счетчика 18. Выход счетчика 7 соединен со входом триггера 6, выход которого подключен ко входу генератора 5. Устройство функционирует следующим образом.

При помощи ключей 13 и 16, дешиф раторов 14 и 17, счетчиков 15 и 18 выбирается контролируемый элемент

матрицы 12. Координаты выбранного элемента индуцируются блоком 20,выполненным в виде линейки светодиодов. в зависимости от режима проверки выдаются необходимые управлягадие Сигналы. С выхода формирователя 3 через блок 2, ключи 13, 16 и выбранный элемент матрицы 12, поступают импульсы записи, стирания и считывания.

Считанная информация с выхода блока 9 поступает в блок 10 управления пишущей машинки 11 и на вход элемента И 8, который задает циклы контроля или останавливает устройство.

После тренировки выбранного элемента матрицы К-кратное переключение устанавливаемое насчетчике 21, счетчик 21 вьщаёт импульс и выбирается следующий элемент матрицы 12.

В устройстве предусмотрены следующие режимы работы:

а г автоматический режим Запись последовательное переключение всех элементов матрицы из высокоомного состояния (Выключено) в низкоомное (Включено);

б.автоматический режим Стирание - последовательное переключение всех элементов матрицы из низкоомного состояния (Включено) в высокоомное (Выключено);

в.автоматический режим Тяжелйй код - чередование режимов Запись

и Стирание по всем элементам матрицы в шахматном порядке;

г.автоматический режим Считывание и печать - последовательное считывание и печать состояния элементов матрицы;

д.ручной режим Запись, Стирание и Считывание осуществляет эти ояерации на одном элементе матрицы;

е. автоматический или ручной режим Тренировка - К-кратное переключение всех элементов матрицы или данного элемента матрицы.

В устройстве предусмотрен контрол режимов Запись, Стирание. Если какой-либо элемент матрицы 12, несмотря на подачу соответствующего импульса, не переключается на вход элемента И 8 подается импульс, который запускает счетчик 7 и последний автоматически повторяет переключающий импульс п раз. Если элемент и после этого не переключается, устройство останавливается, а координаты элемента индицируются на линейке светодиодов 20. В формирователе 3 предусмотрена регулировка амплитуды переключающего импульса. Это вызвано тем, что для осуществления первоначального пробоя-переключения элементов матрицы из аморфных полупроводников требуется несколько больиюе напряжение, чем для их последующих переключений.

Авторы

Даты

1981-04-23—Публикация

1979-01-22—Подача