(54) РЕВЕРСИВНЫЙ ДВОИЧНО-ДЕСЯТИЧНЫЙ СЧЕТЧИК ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный двоично-десятичный счетчик импульсов | 1975 |

|

SU577684A1 |

| Адаптивный формирователь опережающего синхросигнала | 1988 |

|

SU1554110A1 |

| Счетчик с неразрушающейся информацией | 1989 |

|

SU1651380A1 |

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА РАЗМАХОВ КОЛЕБАНИЙ НАПРЯЖЕНИЯ | 1993 |

|

RU2075752C1 |

| Реверсивный двоично-десятичный счетчик | 1974 |

|

SU525251A1 |

| Реверсивный двоично-десятичный счетчик | 1978 |

|

SU780205A1 |

| Устройство для измерения давления | 1988 |

|

SU1569610A1 |

| Устройство для определения разностидВуХ п-РАзРядНыХ чиСЕл | 1979 |

|

SU824208A1 |

| Двоично-десятичное пересчетноеуСТРОйСТВО | 1979 |

|

SU843248A2 |

| Устройство для преобразования кодов | 1977 |

|

SU744544A1 |

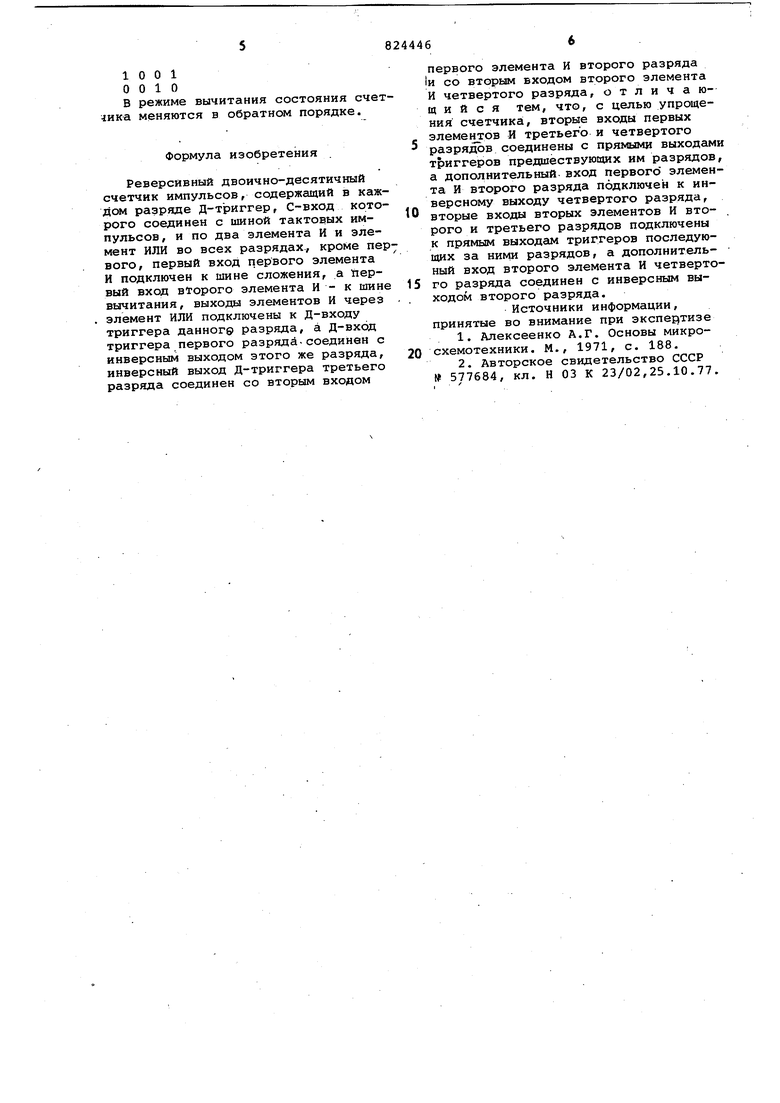

Изобретение относится к импульсной технике и может быть использовано в-автоматике и цифровой измерительной технике. Известен реверсивный двоично-деся тичный счетчик импульсов, содержащий четыре 7)-К-триггера, пять электронных коммутаторов, состоящих из элементов И и ИЛИ, и соответствующие соединения, причем счетные входы триггеров соединены параллельно, один из входов каждого элемента И соединен с шиной сложейия или вычита ния, выходы элементов ИЛИ соединены с входё1ми второго, третьего и четвер того триггеров И . Недостатком данного счетчика является относительная сложность. Известен также реверсивный двоично-десятичный счетчик, содержаиций в каждом разряде Д-триггер, С-вход которого соединен с шиной тактовых импульсов, и по два элемента И во всех разрядах,X кроме первого, первый вход первого элемента И подключен к шине сложения, первый вход второго элемен та И - к шине вычитания, а выходы эл ментов И - к входам элемента ИЛИ, вы ход которого соединен с Д-входом Д-триггера данного разряда, примем вторые входы первых элементов И второго и третьего разрядов подключены к инверсным выходам д-триггеров третьего и четвертого разрядов соответственно, а второй вход первого элемента И четвертого разряда - к прямому выходу Д-триггера второго разряда, второй вход элемента И второго разряда соединен с прямым выходом Д-триггера четвертого разряда, второе входы вторых элементов И третьего и четвертого разрядов - с инверсными выходами Д-триггеров второго и третьего разрядов соответственно f2j. Недостатком известного счетчика также является его относительная слЬжность. Цель изобретения - упрощение счетчика . Поставленная, цель достигается тем, что в реверсивном двоично-десятичном, счетчике импульсов, содержащие в каждсид разряде Д-триггер, Свход которого соединен с шиной тактовых импульсов, и по два элемента И и элемент ИЛИ во всех разрядах, кроме первого, первый вход первого элемента И подключен к щине сложения, .а первый вход второго элемента И - к ишне вычитания, выходы элементов И через элемент ИЛИ подключены к Д-вхО ду триггера-данного разряда, а Двход триггера первого разряда соединен с инверсным выходом этого же разряда, инверсный выход Д-триггера трет его разряда соединен со вторым входов первого элемента И второго разряда и со вторым входом второго элемента И четвертого разряда, вторые входы первых элементов И третьего и четве|)того разрядов соединены с Прямыми выходами триггеров предшествуквдих им разрядов, а-дополнительный вход первого элемента И второго разряда подключен к инверсному выходу четвертог разряда, вторые входы вторых элементов И второго и третьего разрядов подключены к прямым выходам триггеров последующих за ними разрядов, а дополнительный вход второго элемента И четвертого разряда соединен с инве сным выходом второго, разряда. На чертеже представлена-схема реверсивного двоично-десятичного счетчика импульсов. Устройство содержит Д-триггеры 14, элементы И 5-10 и элементы ИЛИ 11-13. Входы С всех триггеров соединены с шиной 14 тактовых импульсов, К первым входам нечетных элементов И подключена шина. 15 сложения, а к пер вым входам четных элементов И - шина 16 вычитания. Устройство работает следукндим- образом. Начальным состоянием триггеров счетчика является состояние 0000. В режиме слбжения на первых входы элементов И 5, 7 и 9 поступает разре и ающий потенциал по шине 15, а на аналогичные входы элементов И 6, 8 и 10- по шине 16 потенциал запрета. В.начс1льном состоянии на Д-вход. триггера 2 второго разряда через элементы 5 и 11 поступает разрешающий потенциал с инверсны выходов триггеров 3 и 4. На входы же элементов 7 и 9 с прямы выходов триггеров 2 и 3 соответственно подаются потенЦИЕШЫ запрета, которые- через элементы ИЛИ 12 и 13поступают на Д-входы триггеров 3 и 4, .Таким образом, nocле прихода первого тактового импульса триггеры счетчика устанавливаются в состоя.ние 1100. При этом сохраняется разрешающий потенциал на Двходе триггера 2, кроме того разрешакэдий потенциал с прямого выхода триггера 2 через элементы 7 и 12 пос тупает на Д-вход триггера 3. Поэтому второй тактовый импу; ьс подтвериадает единичное состояние триггера 2 и переключает триггер 3. Таким образом, после прихода вто рого тактового импульса- триггеры счетчика устанавливаются в состояни ОНО. Далее,аналогично по мере поступления тактовых импульсов счетчик последовательно переходит в состояния1011 0001 1000 0100 1 1 .1 О 0011 1001 0000. В режиме вычитания на элементы И 5, 7 и 9 подается потенциал запрета, а на элементы И 6,- 8 и 10 - разрешающий потенциал. Поэтому в начальном состоянии счетчика разрешающий потенциал с инверсных выходов триггеров 2 и 3 через элементы 10 и 13 поступает на Д-вход триггера 4, а на Д-входы триггеров 2 и 3 подаются потенциалы запрета. После прихода первого тактового импульса триггеры счетчика устанавливаются в состояние 1001. Далее аналогично по мере поступления тактовых импульсов счетчик последовательно принимает состояния 0011 1110 0100 1000 0001 1011 0110 1100 0000. Таким образом, осуществляется счет, тактовых импульсов в режимах сложения и вычитания с основанием счета 10. Положительный эффект предлагаемого счетчика по сравнению с известным заключается в уменьшении числа входов используемых Д-триггерон с до одного и в уменьшении числа внутренних соединений в счетчике с 27 до 25, т.е. достигается упрощение счетчика. Следует также отметить и то, что если в предлагаемом счетчике элементы ИЛИ заменить на элементы ИЛИ-НЕ, причал прямые выходы Д-триггеров второго, третьего и четвертого разрядов подключить так, как подключены их.инверсные выходы, а инверсные как пряАоое, то получаем реверсивный Йвончно-десятичный счетчик, который в режиме сложения последовательно принимает состояния 0010 ,0111 1110 1101 1000 0011 0110 1111 1100

1001 0010

В режиме вычитания состояния счетчика меняются в обратном порядке.

Формула изобретения

Реверсивный двоично-десятичный счетчик импульсов, содержащий в каждом разряде Д-триггер, С-вход которого соединен с шиной тактовых импульсов , и по два элемента И и элемент ИЛИ во всех разрядах, кроме первого, первый вход первого элемента И подключен к шине сложения, а ftepвый вход второго элемента И - к шине вычитания, выходы элементов И через элемент ИЛИ подключены к Д-входу триггера данног© разряда, а Д-вход триггера первого разряда-соединен с инверсным выходом этого же разряда, инверсный выход Д-триггера третьего разряда соединен со вторым входом

первого элемента И второго разряда 1и со вторым входом второго элемента И четвертого разряда, о т л и ч а ювд и и с я тем, что, с целью упрощения счетчика, вторые входы первых - элементов И третьего и четвертого разрядов соединены с прямыми выходами триггеров предшествующих им разрядов, а дополнительный вход первого элемента И второго разряда подключен к инверсному выходу четвертого разряда,

0 вторые входы вторых элементов И второго и третьего разрядов подключены к прямым выходам триггеров последующих за ни1«1И разрядов, а дополнительный вход второго элемента И четверто5го разряда соединен с инверсным выходом второго разряда.

Источники информации, принятые во внимание при экспе тизе

0

577684, кл. Н 03 К 23/02,25.10.77.

Авторы

Даты

1981-04-23—Публикация

1979-07-17—Подача