(54) ДВОИЧНО-ДЕСЯТИЧНОЕ ПЕРЕСЧЕТНОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Двоично-десятичное пересчетное устройство | 1977 |

|

SU746947A1 |

| Реверсивный двоично-десятичный счетчик | 1978 |

|

SU780205A1 |

| Устройство формирования и регистрации путевых параметров для управления шахтной подъемной установкой | 1989 |

|

SU1835383A1 |

| Устройство для преобразования кодов | 1981 |

|

SU968803A1 |

| Реверсивное пересчетное устройство | 1982 |

|

SU1092732A1 |

| Устройство для программного счета изделий | 1983 |

|

SU1113824A1 |

| Адаптивный формирователь опережающего синхросигнала | 1988 |

|

SU1554110A1 |

| Реверсивное пересчетное устройство | 1982 |

|

SU1083365A1 |

| Цифровой фазометр | 1982 |

|

SU1061062A1 |

| Система автоматического сопровожде-Ния зЕВОВ пЕчНыХ МОТАлОК K РЕВЕРСи-ВНОМу лиСТОВОМу СТАНу гОРячЕй пРОКАТКи | 1979 |

|

SU812365A1 |

1

Изобретение относится к электронной и вычислительной технике и может быть использовано в цифровых системах автоматического контроля и управления.

По основному авт. св. № 746947 известно двоично-десятичное пересчетное устройство, содержанлее двоичный реверсивный счетчик, дешифратор и формирователь, счетный вход двоичного реверсивного счетчика соединен со счетным входом двоично-десятичного пересчетного устройства, управляющий вход которого соединен с управляющим входом двоичного реверсивного счетчика, прямее выходы второго и четвертого разрядов которого соединены с входами дешифратора, выход..которого соединен с первым входом формирователя, выход которого соединен с установочными входами второго и третьего разрядов двоичного реверсивного счетчика, вспомогательный вход формирователя соединен с управляющим входом двоично-десятичного пересчетного устройства, счетный вход которого соединен с входом инвертора, выход которого соединен с дополнительным входом формирователя, вспомогателььный выход которого соединен с установочными входами первого и четвертого разрядов двоичного реверсивного счетчика. Формирователь содержит триггер и элемент И-НЕ, входы и выход которого соединены соответственно с вспомогательным входом формирователя, прямым выходом триггера и вспомогательным выходом формирователя, дополнительный вход и выход которого соединены соответственно с первым управляющим входом и инверсным выходом триггера, второй управляющий вход которого соединен с первым входом формирователя 1.

Недостаток известного устройства - снижение быстродействия устройства в целом из-за необходимости применять в формирователе триггер с быстродействием более низким, чем быстродействие триггеров двоичного реверсивного счетчика, поскольку при высоком быстродействии триггера, он реагирует на импульсы с выхода дещифратора, возникающие при переходных процессах в триггерах счетчика с последовательным переносом.

Цель изобретения - повышение быстродействия.

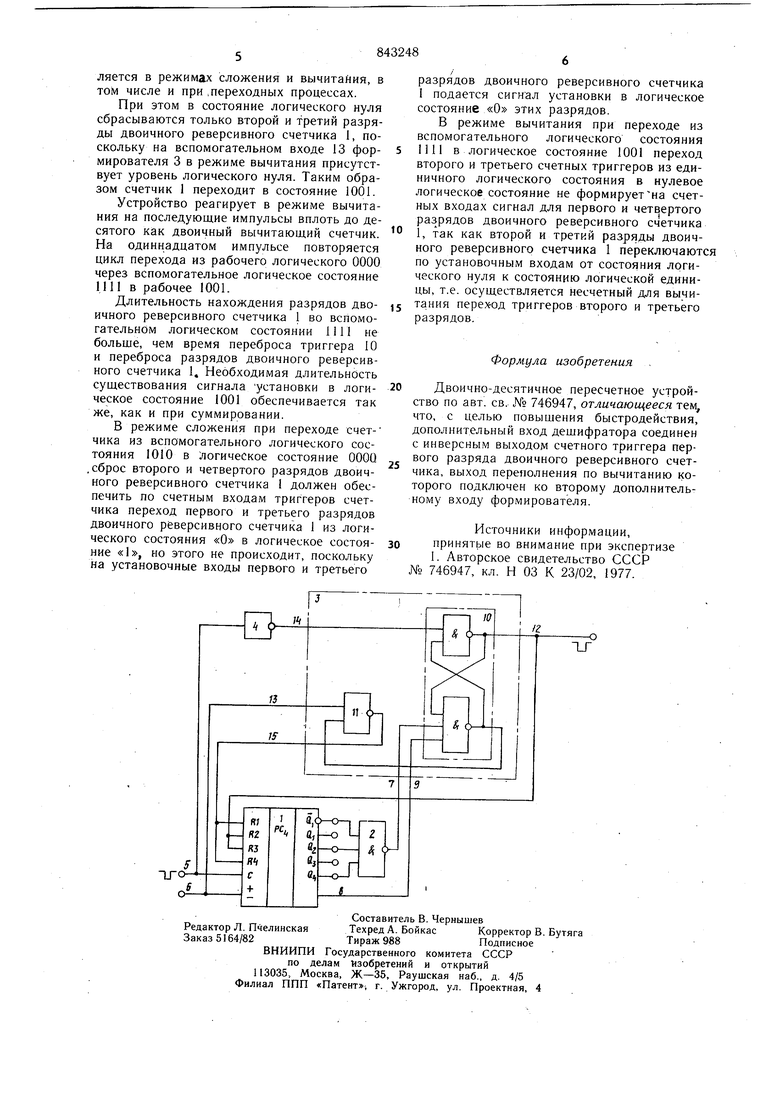

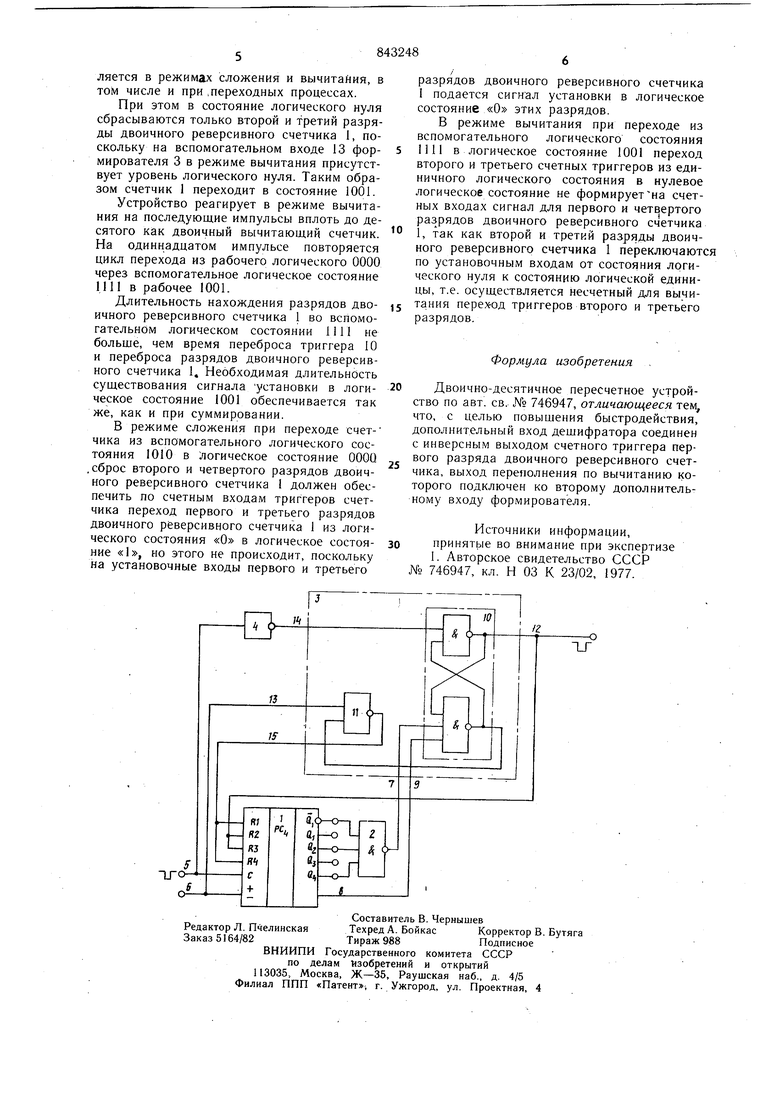

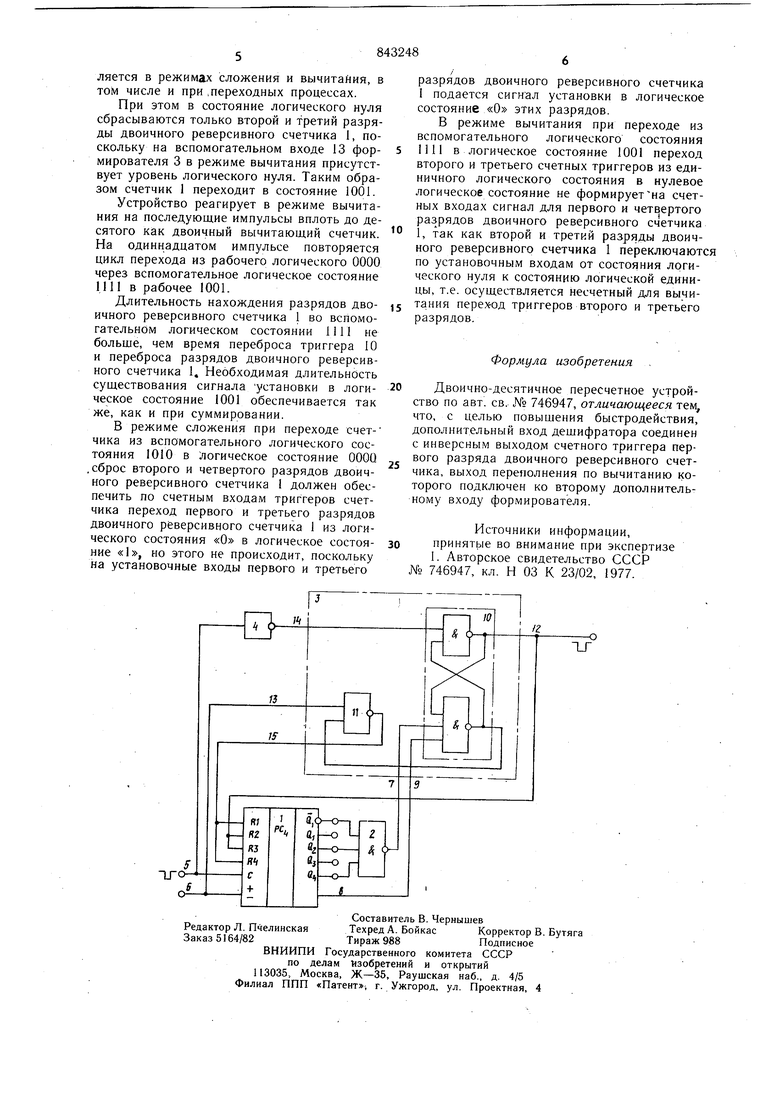

Для достижения этой цели в двоичнодесятичном пересчетном устройстве, содержащем двоичный реверсивный счетчик, дешифратор, инвертор и формирователь, дополнительный вход дешифратора соединен с инверсным выходом счетного триггера первого разряда двоичного реверсивного счетчика, выход переполнения по вычитанию j OToporo подключен ко второму дополнительному входу формирователя. На чертеже представлена структурная электрическая схема двоично-десятичного пересчетного устройства. Двоично-десятичное пересчетное устройство содержит двоичный реверсивный счетчик 1, дешифратора 2, формирователь 3 и инвертор 4. Счетный вход двоичного реверсивного счетчика 1 соединен со счетным входом 5 двоично-десяти.чного пересчетного устройства. Управляющий вход 6 устройства соединен с управляющим входом двоичного реверсивного счетчика 1. Прямые выходы второго и четвертого и инверсный выход первого разрядов счетчика I соединены с входами дешифратора 2. Выход дешифратора 2 соединен с первым входом 7 формирователя 3. Шина 8 импульсов переполнения по вычитанию двоичного реверсивного счетчика 1 соединена со вторым дополнительным входом 9 формирователя 3. Первый 7 и второй 9 дополнительный входы формирователя 3 соединены со вторым управляющим входом триггера 10 на его мнОговходовбй схеме И-НЕ 11. Выход 12 формирователя 3 соединен с установочными входами второго и третьего разрядов двоичного реверсивного счетчика 1. Вспомогательный вход 13 формирователя 3 соединен с управляющим входом 6 двоично-десятичного пересчетного устройства. Счетный вход 5 устройства соединен с входом инвертора 4. Выход инвертора 4 соединен с дополнительным входом ,14 формирователя 3, вспомогательный выход 15 которого соединен с установочными входами первого и четвертого разрядов двоичного реверсивного счетчика 1. Двоично-десятичное пересчетное устройство работает следующим образом. В исходном состоянии двоичный реверсивный счетчик 1 находится в состоянии логического нуля и на выходах всех разрядов этого счетчика нулевые логические состояния. На входе 5 - устройства - единичный логический сигнал, а триггер 10 находится в нулевом логическом состоянии. Устройство изменяет свое состояние от нуля до девяти и от девяти до нуля в режимах соответственно сложения и вычитания, как обычный двоичный реверсивный счетчик благодаря сложению или вычитанию осуществляемому двоичным реверсивным счетчиком 1. В режиме сложения десятый импульс переводит двоичный реверсивный счетчик 1 из логического состояния 1001 во вспомогательное логическое состояние 1010, при этом на все три входа дешифратора 2 поступают уровни логической единицы. Подобный набор сигналов на входах дешифратора 2 больше не появляется ни в режиме вычитания, ни в режиме сложения, в том числе и при переходных процессах. С выхода дешифратора 2 поступает на первый вход 7 формирователя 3 сигнал установки триггера 10 в состояние логической единицы. При этом на первом управляющем входе триггера 10 в это время присутствует сигнал, не мешающий установке триггера 10 в состояние логической единицы. С инверсного выхода триггера 10 уровень логического нуля поступает через выход 12 формирователя 3 на установочные входы второго и третьего разрядов двоичного реверсивного счетчика 1, устанавливая их в состояние логического нуля. Одновременно уровень логической единицы с прямого выхода триггера 10 и вспомогательного входа 13 обуславливает на выходе элемента И-НЕ 11 уровень логического нуля, который обеспечивает установку в «О первого и четвертого разрядов двоичного реверсивного счетчика 1. Таким образом, в режиме сложения сразу же после достижения вспомогательного логического состояния 1010 устройство переходит в логическое состояние 0000. Длительность нахождения счетчика 1 в логическом состоянии 1010 не больше, чем суммарное время срабатывания дешифратора 2, переброса триггера 10 срабатывания элементов И-НЕ 11 и переброса разрядов двоичного реверсивного счетчика 1. Триггер 10 хранит состояние логической единицы до прихода паузы между входными импульсами, которая обеспечивает на входе триггера 10.сигнал установки его в исходное Состояние логического нуля. Таким образом, обеспечивается вполне достаточная длительность существования сигнала установки счетчика 1 в логическое состояние 0000. В режиме вычитания двоичный реверсивный счетчик I переходит после прихода первого импульса из исходного логического состояния 0000 во вспомогательное логическое состояние 1111, при этом дещифратор 2 не выдает сигнал на изменение состояния триггера 10, гак как на его входе присутствует сигнал Q, равный логическому нулю. В режиме вычитания изменение состояния триггера 10 осуществляется импульсом, полученным диффренцированием перепада из «1 в «О на инверсном выходе старшего счетного триггера двоичного реверсивного счетчика 1, т.е. установка триггера 10 в состояние логической единицы осуществляется в режиме вычитания от шины 8 выходных диффренцированных импульсов переполнения по вычитанию двоичного реверсивного счетчика. Подобный сигнал больше не появ

Авторы

Даты

1981-06-30—Публикация

1979-03-05—Подача