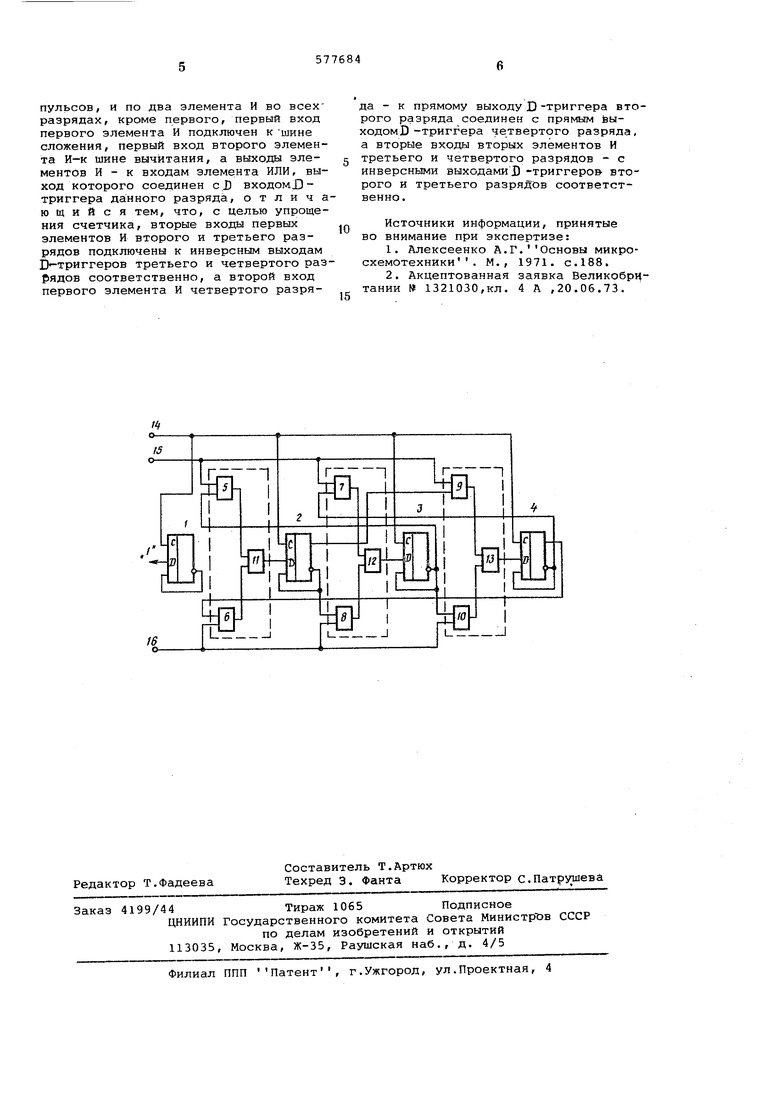

На чертеже дана структурная электрическая схема предлагаемого счетчика Счетчик содержит)/-триггеры 1-4, логические элементы И 15-10, логические элементы ИЛИ 11-13. К С Sxoдам триггеров подключена шина 14 тактовых импульсов, к первым входам логических элементов 5,7 и 9 подключена шина 15 сложения, а к первым входам логических элементов И 6,8,10 шина 16 вычитания. Информационный сиг нал подан на вход D-триггера 1. Рассмотрим работу предлагаемого счетчика сначал- в режиме сложения, затем в режиме вычитания. В режиме сложения начальное состс|яние триггеров счетчика 0000.Потенциал разрешения поступает по шине сложения на первые входы элементов 5,7 и 9. На входы элементов 6,8 и 10 по шине вычитания поступает потенциал запрета . В исходном, состоянии триггеров счетчика потенциал запрета с единичного выхода триггера 2 поступа;ет на вход элемента- 9, Таким образом через элемент 13 на входЗ - триггера 4 потенциал разрешения не поступает. Йа входы элементов 5 и 7 с нулевых выходов триггеров 3 и 4 соответственно поступаютпотенциалы разрешения, которые через элемента 11 и 12 поступают на входыСг риггеров 2 и 3. Триггеры типа 13 iработают так, что если в момент прихода счетного импулЬ са на триггер подан потенциал запрета на входD/ то осуществляется запрет перехода триггера из состояния О в состояние i (переход из 1 в О разрешен).После прихода первого тактового импульса триггеры счетчика таким образом устанавливают ся в положение 1110. При этом потенциал разрешения с единичного выхода триггера 2 поступает на элемент 9 и через элемент 13 открывает входВ триггера 4. Поэтому после лриходй второго тактового импульса триггер 4 переворачивается. Воздействие на вход D-TpHrrepoB 2 и 3, из -рассмотрения исключим, так. как :;пёрех,рд .из состояния р . состояние i ..О, разрешен независимоОТ .потенциала:на входеD,Таким образом,после Прихода второго тактового) импульса триггеры счет чика устанавливаются в положение 0001 Далее аналогично по мере поступлеНИН тактовых импульсов триггеры счетчика принимают положения 1100 в режиме вычитания начальное состояние триггеров счетчика также 0000. Потенциал разрешения поступает по шине вычитания на элементы 6,8 и 10. На входы элементов 5,7 и 9 по шине сложения поступает потенциал запрета. В исходном состоянии триггеров счетчика потенциал запрета с единичного плечатриггера 4 поступает на элемент 6.Таким образом, через элемент 11 на вход) -триггера 2 потенциал разрешения не поступает.На входы элементов 8и10 с нулевых выходов триггеров 2 и 3 поступает потенциал разрешения, который через элементы 12 и 13 поступает на входыО -триггеров 3 и 4. После прихода первого тактового импульса триггеры счетчика- устанавливаются в положение 1011. Далее аналогично по мера поступления тактоваХ импульсов триггеры счетчика принимайт положения: 0100 Таким образом осуществляется счет тактовых импульсов в режиме сложения и вычитания с основанием счета 10. Запрещенными состояниями счетчика являются: Положительный эффект предлагаемого счетчика заключается в уменьшении числа схем И и ИЛИ по сравнению с известным с 14 до 9 -(причем использу ется только двухвходовые схемы И и ИЛИ) и в уменьшении.числа внутренних ежсоединений в счетчике с 51 до 22, т.е. достигается упрощение счетчика. Формула изобретения Реверсивный двоично-десятичный счетчик импульсов, содержащий в каждом разрядеВ .-триггер/ С вход которого соединён с шиной тактовых импульсов, и по два элемента И во всех разрядах, кроме первого, первый вход первого элемента И подключен к шине сложения, первый вход второго элемента И-к шине вычитания, а выходы элементов И - к входам элемента ИЛИ, выход которого соединен cD входомЛ)триггера данного разряда, отличающийся тем, что, с целью упрощения счетчика, вторые входы первых элементов И второго и третьего разрядов подключены к инверсным выходам 1 -триггеров третьего и четвертого разРядов соответственно, а второй вход первого элемента И четвертого разряда - к прямому выходуD-триггера второго разряда соединен с прямым йыходомВ -триггера четвертого разряда, а вторые входы вторых элементов И третьего и четвертого разрядов - с инверсными выходами D -триггеров- второго и третьего разрядов соответственно.

Источники информации, принятые во внимание при экспертизе:

1.Алексеенко А.Г.Основы микросхемотехники. М., 1971. с.188,

2.Акцептованная заявка ВеликобрЦтании № 1321030,кл. 4 А ,20.0&.73.

| название | год | авторы | номер документа |

|---|---|---|---|

| Реверсивный двоично-десятичныйСчЕТчиК иМпульСОВ | 1979 |

|

SU824446A1 |

| Реверсивный двоично-десятичный счетчик | 1973 |

|

SU455493A1 |

| Устройство для преобразования кодов | 1977 |

|

SU744544A1 |

| СЧЕТЧИК ИМПУЛЬСОВ | 2005 |

|

RU2284654C2 |

| Устройство для контроля импульсных последовательностей | 1986 |

|

SU1338034A1 |

| Устройство для вычисления процентного отношения двух величин | 1986 |

|

SU1335986A1 |

| Десятичный реверсивный счетчик с цифровой индикацией | 1985 |

|

SU1279062A1 |

| Устройство для формирования адресов операндов процессора быстрого преобразования Фурье | 1983 |

|

SU1133597A1 |

| Устройство для сложения и вычитания чисел в фазо-импульсной форме | 1976 |

|

SU595732A1 |

| Цифровой интегратор с контролем | 1975 |

|

SU540269A1 |

Авторы

Даты

1977-10-25—Публикация

1975-06-25—Подача