(54) РЕВЕРСИВНЫЙ ДВОИЧНО-ДЕСЯТИЧНЫЙ СЧЕТЧИК

| название | год | авторы | номер документа |

|---|---|---|---|

| Двоично-десятичное пересчетное устройство | 1977 |

|

SU746947A1 |

| Двоично-десятичное пересчетноеуСТРОйСТВО | 1979 |

|

SU843248A2 |

| Реверсивный десятичный счетчик | 1979 |

|

SU822381A1 |

| Устройство для определения квантилей случайного процесса | 1986 |

|

SU1365095A1 |

| Реверсивный двоично-десятичный счетчик | 1974 |

|

SU525251A1 |

| Устройство для преобразования кодов | 1977 |

|

SU744544A1 |

| Реверсивный двоично-десятичный счетчик | 1977 |

|

SU656219A1 |

| Цифровой фазометр | 1982 |

|

SU1061062A1 |

| Реверсивная пятиразрядная двоичнодесятичная счетная декада | 1976 |

|

SU577686A1 |

| Реверсивный формирователь двоичного кода | 1987 |

|

SU1480123A2 |

1

ИэоОретение относится к электронной и вычислительной технике, в частности -к реверсивным двоично-десятичным счетчикам и может быть испоЛьэовано в цифровых системах автоматичес- 5 кого контроля и управления.

Известен разностный двоичный счетчик , ка;кдый разряд которого содержит триггер, элемент ИЛИ и два элемента И, первые входы которых соединены tO соответственно с прямым и инверснЕлм выходами триггера, счетный вход которого соединен с выходом элемента ИЛИ, входы которого соединены с вторыми входами элементов И того же раз-15 ряда и входами сложения и вычитания данного разряда, а выходы первого и второго элементов И соединены соответственно с выходами переноса и за ема данного разряда til.20

Недоста:тком этого счетчика является невозможность счета в двйичнодесятичиом коде.

Известен также реверсивный двоично-десятичный счетчик, содержаний 2S четыре разряда, каждый из которых содержит триггер, элемент ИЛИ и первый и второй элементы И, счетный вход триггера каждого разряда соединен с выходом элемента ИЛИ того же 30

разряда, а входь элемента ИЛИ каждого разряда, креме первого, соединены с выходами соответственно первого и второго элементов И предыдущего разряда, первые входы которых соединены соответственно с прямым и инверсным выходами триггера того же разряда, вторые входы первого и второго элементов И ка) разряда, кроме первого и четвертого разрядов, соединены с выходами соответственно первого и второго элементов И предыдущего разряда, первый и второй входы элемента ИЛИ первого разряда соединены соответственно с входами сложения и вычитания реверсивного двоично-десятичного счетчика, которые соединены с вторыми входами соответственно первого и второго элементов И этого разряда 2.

Недостатком этого реверсивного двоично-десятичного счетчика явля-- . ется относительно низкая достоверность функционирования, что связано с кратковременным появлением в процессе счета кодовых состояний, не входящих в двоично-десятичный код.

Целью изобретения является повышение достоверности функционирования.

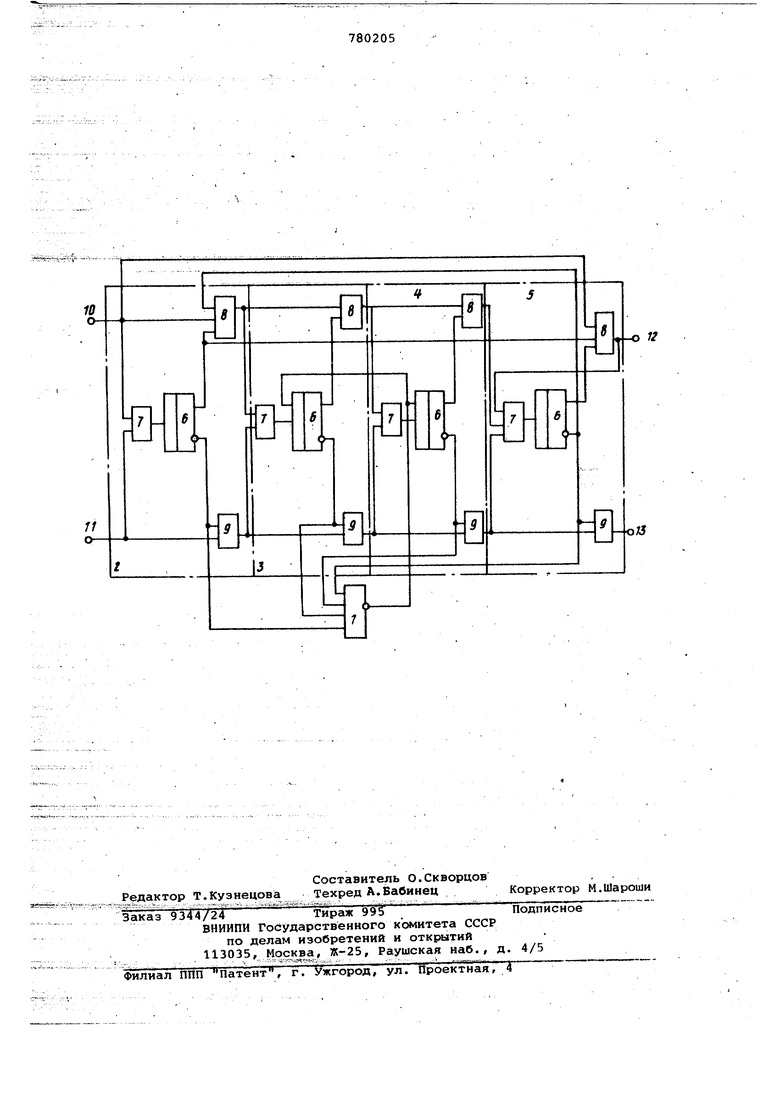

Поставленная цель достигается тем, что в реверсивный двоично-лесятичны счетчик, содерхощий четыре разряда, каждый из которых содержит триггер элемент ИЛИ и первый и второй элементы И, счетный вход триггера ка;; дого разряда соединен с выходом элемента ИЛИ того же разряда, а входы элемента ИЛИ каждого разряда, кроме первого, соединены с выходами соотве ственно первого и второго элементов И предыдущего разряда, первые входы которых соединены соответственно с прямы1 л и инверсным выходами триггера того же разряда, вторьае входы первого и второго элементов И каждого раз ряда кроме первого и четвертого раз рядов соединены с(|рыходами соответст венно первого и второго элементов и предыдущего разряда, первый и второй входы элемента ИЛИ первого разряда соединены соответственно с входами сложения и вычитания реверсивного двоично-десятичного счетчика, которые соединены с вторыми входами соответст венно первого и второго элементов И этого разр5ща, введен элемент И-ИЕ, выходкоторого соединен с- J входами триггеров второго и третьего разрядо входы элемента И-НЕ соединены с инве сными, выходами триггеров всех разрядов, вход сложения реверсивного двоично-десятичного счетчика соединен с вторым входом первого элемента И чет вертого разряда, третий вход которог соединен с первым входом первого эле мента И первого разряда, третий вход которого соединен с инверсным выхо-. дом триггера четвертого разряда, третий, вход элемента ИЛИ соединен с выходом первого элемента И этого разряда и выходом переноса реверсивного двоично-десятичного счетчика, выхрд заема которого соединен с выходом второго элемента И четвертого разряда, второй вход которого соединен с выходом второго элемента И третьего разряда. Структурная схема реверсивного двоично-десятичного счетчика показана на чертеже. . - Реверсивный двоично-десятичный счетчик содержит элемент 1 И-НЕ и четыре разряда 2-5, каждый из которы содержит триггер 6, элемент ИЛИ 7 и первый 8 и второй 9 элементы И, счетный вход триггера 6 каждого раз ряда соединен с выходом элемента ИЛИ 7 того же разряда, а входы элемента Ю1И каждого разряда, кроме первого, соединены с выходами соответственно первого 8 и второго 9 элементов И предыдущего разряда, первые входы которых соединены соответственно с прямым и инверсным выходами триггера 6 того же разряда, вторые входы первого 8 и второго 9 элементов И каждо го разряда, кроме первого 2 и четвер того 5 разрядов,соединены с выходами соответственно первого 8 и второго элементов И предыдущего разряда, первый и второй входы элемента ИЛИ 7 первого разряда 2 соединены соответственно с входами сложения 10 и вычитания 11 реверсивного двоично-десятичного счетчика, которые соединены с вторыми входами соответственно первого 8 и второго 9 элементов. И этого разряда, выход элемента И-НЕ 1 соединен с J входами триггеров 6 второго 3 и третьего 4 разрядов, входы элемента И-НЕ 1 соединены с инверсными выходами триггеров 6 всех разрядов 2, 3, 4. и 5., вход сложения 10 реверсивного двоично-десятичного счетчика соединен с вторым входом первого элемента И 8 четвертого разряда 5, третий вход которого соединен с первым входом первого элемента И 8 первого разряда 2, третий вход которого соединен с инверсным выходом триггера б четвертого разряда 5, третий вход элемента ИЛИ 7 соединен с выходом первого элемента И 8 этого разряда и выходом переноса 12 реверсивного двоично-десятичного счетчика, выход заема 13 которого соединен с выходом второго элемента И 9 четвертого разряда 5, второй вход которого соединен с выходом второго элемента И 9 третьего разряда 4. Работает устройство следующим образом. Предположим, в исходном состоянии триггеры 6 находятся в нулевом логическом состоянии, при этом элементы И 9 открыты, а элементы И 8 закрыты. На выходе элемента И-НЕ 1 присутствует нулевой логический потенциал, запрещающий переход триггеров 6 второго и третьего разрядов в единичное логическое состояние. В режиме сложения первый импульс, поступающий на вход сложения 10, проходит через элемент ИЛИ 7, устанавливает триггер 6 первого разряда в. единичное логическое состояние, которое выдает разрешающий сигнал на элемент И 8 для прохождения последующего импульса. При этом ни выходе элемента И-НЕ 1 появляется логический единичный потенциал, разрещающий переход триггеров 6 второго и третьего разря- дов из логического состояния О в лоВторой импугическое состояние льс устанавливает через элемент ИЛИ 7 триггер 6 первого разярда 3 в нулевое логическое состояние, а через открытый элемент И 8 и элемент ИЛИ 7 - триггер 6 второго разряда в единичное логическое состояние. При дальнейшем поступлении на вход счетчика от третьего до восьмого импульсов, счетчик проходит все состояния, которые соответствуют двоично-десятичному коду 8-4-2-1. После записи счетчике кода 1000, закрывается элемент И 8 первого разряда сигналом

с инверсного выхода триггера 6 четвертого разряда.

Девятый импульс устанавливает через элемент ИЛИ 7 триггер 6 первого разряда в единичное логическое состояние, т. е. записывается код 1001, соответствующий цифре 9. После записи в счетчике цифры 9 открывается элемент И 8 четвертого разряда. Поступающий десятый импульс через элемент ИЛИ 7 первого разряда И 8 четвертого разряда, ИЛИ 7 четвертого разряда устанавливает триггеры 6 первого и четвертого разрядов в нулевое логическое состояние, а на выходе элемента И 8 четвертого разряда образуется сигнал перенос. В счетчике записывается код 0000, что и необходимо для реализации пересчета на десять.

В режиме вычитания, когда все четыре триггера б находятся в нулевом состоянии, элементы И 9 открыты, на выходе элемента- И 8 четвертого разряда присутствует нулевой логический потенциал, который поступает на вход элемента ИЛИ 7 четвертого разряда и не влияет на работу счетчика при реверсе . На входах. J триггеров б втоpoiro и третьего разрядов держится

нулевой логический потенциал, запрещающий переход их с нулевого логического состояния в единичное . Первый входной импульс, поступающий на вход вычитания 11 через элемент ИЛИ б первого разряда, И 9 и ИЛИ 7 четвертого разряда установит триггеры б первого и четвертого разрядов в

единичное логическое состояние, т. е. запишется код 1001, что соответствует цифре 9. При этом на выходе элемента И 9 четвертого разряда вырабатывается сигнал заем. На J входах триггеров б второго и третьего разрядов образуется единичный логический сигнал, не влияющий на работу счетчика в режиме вычитания . Очередными импульсами счетчик последовательно установится в состояния, соответствующие 8, 7,. ..Д, как и в обычном вычитайщем счетчике.

Таким образом, предлагаемое устроство позволяет повысить надежность работы счетчика в коде 8-4-2-1, поскольку исключаются промежуточные кратковременные состояния 1010 и 1111, не соответствующие коду 84-2-1.

Формула изобретения Реверсивный двоично-десятичный счетчик, содержащий четыре разряда, каждый из которых содержит триггер, элемент ИЛИ и первый и второй эле- . менты И, счетный вход триггера каждого разряда соединен с выходом элемента ИЛИ того же разряда, а входы элемента ИЛИ каждого разряда, кроме первого, соединены с выходами соответственно первого и второго элемен0тов И предыдущего разряда, первые входы которых соединены соответственно с прямьЫ и инверсным выходами триггера того же разряда, вторые входы первого и второго элементов И

5 каждого разряда, кроме первого и четвертого разрядов,соединены с выходами соответственно первого и второго элементов И предыдущего разряда, первый и второй входы элемента ИЛИ

0 первого разряда соединены соответственно с входами сложения и вычитания реверсивного двоично-десятичного счетчика, которые соединены с вторыми входами соответственно первого и второго, элементов И этого разряда,

5 отличающийся тем. что, с целью повышения достоверности функционирования, введен элемент И-НЕ, выход которого соединен с J входами триггеров второго и третьего

0 разрядов, входы элемента И-НЕ соединены с инверсными выходами триггеров всех разрядов; вход сложения реверсивного двоично-десятичного счетчика соединен с вторым входом первого

5 элемента И четвертого разряда, третий вход которого соединен с первым входом первого элемента И первого разряда, третий вход которого соединен с инверсным выходом триггера

0 четвертого разряда, третий вход элемента ИЛИ соединен с выходом первого элемента И этого разряда и выходом переноса реверсивного двоично-десятичного счетчика, выход заема которого соединен с выходом второго эле5мента И четвертого разряда, второй вход которого соединен с выходом второго элемента И третьего разряда.

Источники информации, принятые во внимание при экспертизе

0

№ 525251, кл. Н 03 К 23/24, 1977 (про5тотип) .

Авторы

Даты

1980-11-15—Публикация

1978-12-12—Подача