1

Изобретение относится к импульсной технике и может найти применение в устройствах измерительной и вычислительной техники.

Известны устройства управляемой задержки импульсов, содержащие генератор счетных импульсов, первый триггер, дешифратор нуля, выход которого соединен с единичным входом первого триггера, реверсивный счетчик, выходы которого соединены с выходами дешифраторов нуля, первый логический элемент И, подключенный первым входом к источнику задерживаемых имиульсов, вторым входом - к выходу генератора счетных импульсов, а выходом - к суммирующему входу реверсивного счетчика, второй логический элемент И, подключенный первым входом к нулевому выходу первого триггера, вторым входом - к выходу генератора счетных импульсов, а выходом - к вычитающему входу реверсивного счетчика, второй триггер, нулевой вход которого подключен к источнику задерживаемых импульсов, третий логический элемент И, первый вход которого подключен к нулевому выходу второго триггера, а второй вход соединен с выходом генератора счетных импульсов, источник импульсов управления 1.

Такие устройства управляемой задержки не позволяют автоматически управлять временем задержки входных импульсов в течение межимпульсных интервалов. Известно устройство управляемой задержки, содержащее генератор счетных импульсов и два идентичных канала: канал задерживаемых импульсов и канал управления задержкой; при этом каждый канал

включает реверсивный счетчик, суммирующий и вычитающий входы которого подключены к выходам соответственно первого и второго логических элементов И, первый вход второго логического элемента И

соединен с генератором счетных импульсов, а второй вход соединен с триггером, первый вход которого соединен с выходом дешифратора нуля, входами соединенного с выходами счетчика, причем дешифратор нуля

канала управления задержкой соединен со вторым входом триггера канала задерживаемых импульсов, а второй вход триггера канала управления задержкой подключен к источнику задерживаемых импульсов 2.

Это устройство обладает пониженным быстродействием, поскольку не позволяет подавать очередной задерживаемый импульс, пока не будет сформирован на выходе предыдущий задержанный импульс, и

вводить очередной импульс длительности

Задержки, пока не начнется формирование предыдущего задержанного импульса.

Целью изобретения является повышение быстродействия.

Указанная цель достигается тем, что в устройство управляемой задержки импульсов, содержащее генератор счетных импульсов и два идентичных канала: канал задерживаемых импульсов и канал управления задержкой, причем каждый канал включает реверсивный счетчик, суммирующий и вычитающий входы которого подключены к выходам соответственно первого и второго логических элементов И, первый вход второго логического элемента И соединен с генератором счетных импульсов, а второй вход - с выходом триггера, первый вход которого подключен к выходу дешифратора нуля, входами соединенного с выходами счетчика, причем второй вход триггера канала задерживаемых импульсов соединен с выходом дешифратора нуля канала управления задержкой, а второй вход триггера канала управления задержкой подключен к источнику задерл иваемых импульсов, в каждый канал введены пересчетный блок, три дополнительных логических элемента И, дополнительный триггер и формирователь импульсов, при этом вход пересчетного блока через последовательно соединенные первый и второй дополнительные логические элементы И подключен к выходу генератора счетных импульсов, а выход пересчетного блока подключен ко входу одного из разрядов реверсивного счетчика и к первому входу дополнительного триггера, первый выход которого соединен со вторым входом второго дополнительного логического элемента И; второй выход этого триггера соединен с первым входом первого основного логического элемента И, второй вход которого подключен к выходу первого дополнительного логического элемента И, а второй вход дополнительного триггера подключен ко второму входу первого дополнительного логического элемента И через формирователь импульсов и третий дополнительный логический элемент И, второй вход которого подключен к выходу основного триггера канала; кроме того, вход формирователя импульсов канала задерживаемых импульсов подключен к источнику задерживаемых импульсов, а вход формирователя импульсов канала управления задержкой подключен к источнику импульсов управления.

Введение новых элементов и связей позволяет повысить быстродействие устройства управляемой задержки импульсов.

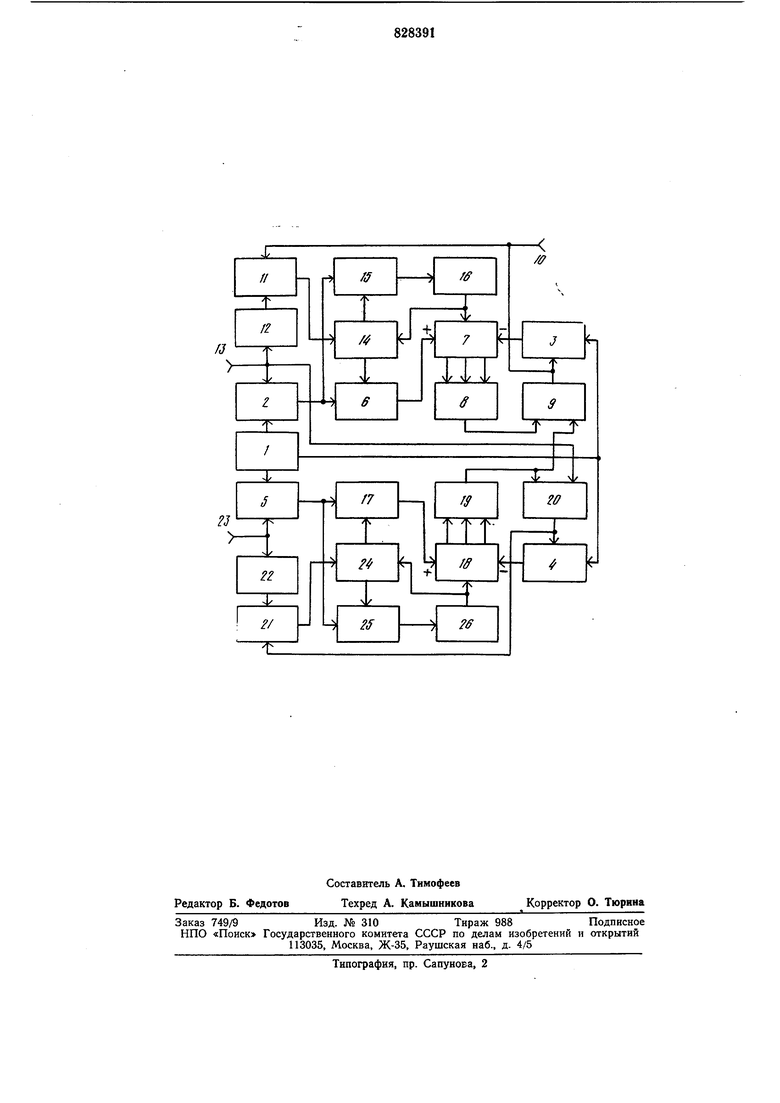

На чертеже представлена функциональная электрическая схема устройства.

Устройство управляемой задержки импульсов содержит генератор счетных импульсов 1, соединенный с первыми входами логических элементов И 2-5. Выход логического элемента И 2 через логический элемент И 6 соединен с суммирующим входом реверсивного счетчика 7, вычитающий вход которого подключен к выходу логического элемента И 3, а выходы разрядов через дешифратор нуля 8 подключены к нулевому входу триггера 9, единичный выход которого соединен со вторым входом логического элемента И 3, с выходом устройства 10 и с первым входом логического элемента И 11. Второй вход логического элемента И 11 через формирователь импульсов 12 подключен ко второму входу элемента 2 и ко входу 13, на который поступают задерживаемые импульсы; выход элемента И 11 подключен к единичному входу триггера 14. Нулевой выход триггера 14 подключен ко второму входу элемента И 6, единичный выход - к первому входу логического элемента И 15, второй вход которого соединен с выходом элемента И 2, а выход - со входом пересчетного блока 16. Выход пересчетной схемы 16 подключен ко входу одного из последних каскадов реверсивного счетчика 7 и к нулевому входу триггера 14. Элементы 2, 3, 6-16 и связи между ними составляют канал задерживаемых импульсов.

Выход логического элемента И 5 через логический элемент И 17 соединен с суммирующим входом реверсивного счетчика 18, вычитающий вход которого подключен к выходу логического элемента И 4, а выходы разрядов через дешифратор нуля 19 подключены к нулевому входу триггера 20, единичный выход которого соединен со вторым входом логического элемента И 4 и с первым входом логического элемента И 21. Второй вход логического элемента И 21 через формирователь импульсов 22 подключен ко второму входу элемента 5 и ко входу 23, на который поступают импульсы управления; выход элемента И 21 подключен к единичному входу триггера 24. Нулевой выход триггера 24 подключен ко второму входу элемента И 17, единичный выход - к первому входу логического элемента И 25, второй вход которого соединен с выходом элемента 5, а выход - со входом пересчетного блока 26. Выход пересчетного блока 26 подключен ко входу одного из последних каскадов реверсивного счетчика 18 и к нулевому входу триггера 24. Элементы 4, 5, 17-26 и связи между ними составляют канал импульсов управления.

Кроме того, единичный вход триггера 20 подключен ко входу задерживаемых импульсов 13, а единичный вход триггера 9 соединен с выходом дешифратора нуля 19.

В исходном состоянии сигналы на входах 13 и 23 отсутствуют, поэтому импульсы генератора 1 через логические элементы И 2 и 5 не проходят; триггеры 9 и 20 находятся в нулевом состоянии, поэтому импульсы генератора 1 через логические элементы И 3

и 4 не проходят. Триггеры 14 и 24 находятся в нулевом состоянии, при котором «разрешающее напряжение подано на логические элементы И 6 и 17. Пересчетные блоки 16 и 26, как и реверсивные счетчики 7 и 18, находятся в исходном нулевом состоянии.

Работа устройства начинается с поступления на вход 23 прямоугольного импульса управления, длительность которого равна требуемому времени задержки Тз,. Этот импульс поступает на вход логического элемента И 5, разрешая прохождение импульсов с генератора 1 через логический элемент И 17 на суммируюш,ий вход реверсивного счетчика 18. Таким образом, сигнал управления преобразуется в импульсы, число которых пропорционально требуемому времени задержки. Это число импульсов записывается в- счетчик 18 в виде кода и может храниться сколько угодно.

После установки необходимого значения времени задержки устройство готово принять задерживаемый импульс. Прямоугольный импульс, который необходимо задержать, поступает через вход 13 на логический элемент И 2, с помош.ыо которого импульсы генератора 1 через логический элемент И 6 поступают на суммирующий вход реверсивного счетчика 7. Таким образом, задерживаемый сигнал преобразуется в импульсы, число которых пропорционально длительности задерживаемого импульса. Это число в виде кода хранится в счетчике 7.

Одновременно задерживаемый импульс со входа 13 поступает на единичный вход триггера 20 и переводит его в единичное состояние, при котором на выходе триггера появляется «разрешающее напряжение. Под действием этого напряжения логический элемент И 4 пропускает на вычитающий вход счетчика 18 импульсы генератора 1. После того как число импульсов станет равным числу импульсов, введенному ранее на его суммирующий вход, счетчик 18 переходит в исходное нулевое состояние, и на выходе дешифратора нуля 19 появляется импульс. Этот импульс поступает на нулевой вход триггера 20, возвращая его в исходное нулевое состояние, и на единичный вход триггера 9, перебрасывая последний в единичное состояние, при котором на входе логического элемента И 3 появляется «разрещающее напряжение. Через открытый этим напряжением элемент 3 импульсы с генератора 1 поступают на вычитающий вход реверсивного счетчика 7. После того как число этих импульсов станет равным числу импульсов, введенному ранее на его суммирующий вход, счетчик 7 переходит в исходное нулевое состояние, и на выходе дешифратора нуля 8 появляется импульс. Этот импульс поступает на нулевой

вход триггера 9, возвращая его в исходное состояние. Устройство возвращается в исходное состояние, сформировав на выходе 10 прямоугольный импульс, по длительности равный поступившему на вход 13 задерживаемому импульсу, но задержанный относительно последнего.

Для задержки очередного импульса на вход 23 должен быть подан очередной импульс, обеспечивающий необходимое время задержки. Если этот импульс управления поступает на вход 23 после того, как появился сигнал формирования начала задерживаемого импульса на выходе дещифратора нуля 19, канал управления задержкой работает, как было описано выще. Но предлагаемое устройство в отличие от прототипа позволяет подавать очередной импульс управления до появления сигнала с дешифратора нуля 19.

В этом случае формирователь импульсов 21 формирует короткий импульс в момент начала импульса управления. Этот импульс через логический элемент И 21, на управляющем входе которого имеется «разрешающее напряжение с выхода триггера 20, поступает на единичный вход триггера 24. Триггер 24 перебрасывается в единичное состояние, при котором «разрещающее напряжение снимается с логического элемента И 17 и подается на логический элемент И 25. Импульс управления открывает логический элемент И 5, и импульсы генератора 1 через логические элементы И 5 и 25

поступают иа вход пересчетного блока 26, который начинает считать импульсы.

Пересчетный блок 26 (а аналогично ему и пересчетная схема 1 работает в том же коде, что и реверсивный счетчик 18 (7), но

имеет меньщее число разрядов, чем счетчик 18 (7). Допустимая соответствующая пересчетная схема имеет п разрядов. Тогда выход этой пересчетной схемы подключается ко входу п-1-го разряда соответствующего

реверсивного счетчика. При этом максимальное число импульсов, которое может принять пересчетная схема до переполнения, должно быть меньще числа импульсов генератора 1, укладывающихся в минимальной длительности импульсов, поступающих на вход соответствующего канала устройства.

Пока пересчетный блок 26 считает импульсы генератора 1, завершается процесс

вычитания в счетчике 18, срабатывает дешифратор нуля 19 и, как было описано выще, в канале задерживаемых импульсов начинается формирование очередного задержанного импульса. В момент времени, когда число импульсов, поступивщих на вход пересчетной схемы, сравняется с коэффициентом пересчета этой схемы, она переполняется, переходит в исходное состояние, и на ее выходе вырабатывается импульс.

Этот импульс поступает на n+1-вый разряд реверсивного счетчика, записывая в этом разряде единицу, и на нулевой вход триггера 24, перебрасывая его в нулевое состояние, снимая «разрешающее напряжение с логического элемента И 25 и подавая «разрешающее напряжение на логический элемент И 17. Поэтому последующие импульсы записи интервала задержки с выхода элемента 5 поступают уже на суммирующий вход реверсивного счетчика 18, и к моменту окончания импульса управления в счетчике будет зафиксировано полностью число, соответствующее очередному времени задержки Тз,, хотя часть этого времени счетчик не принимал участия в фиксации этого интервала. Аналогично работе канала управления задержкой работают элементы канала задерживаемых импульсов, когда очередной задерживаемый импульс поступает на вход 13 в процессе формирования каналом задержанного выходного импульса. Как следует из приведенного выше, предлагаемое устройство обладает более высоКИМ быстродействием, чем прототип, так как в отличие от последнего позволяет подавать управляющие сигналы до начала процесса формирования очередного задержанного импульса на выходе и подавать задерживаемые импульсы до окончания этого процесса. Формула изобретения Устройство управляемой задержки импульсов, содержащее генератор счетных импульсов и два идентичных канала: канал задерживаемых импульсов и канал управления задержкой, причем каждый канал содержит реверсивный счетчик, суммирующий и вычитающий входы которого подключены к выходам соответственно первого и второго логических элементов И, первый вход второго логического элемента И соединен с генератором счетных импульсов, а второй вход - с выходом триггера, первый вход которого подключен к выходу дещифратора нуля, входами соединенного с выходами счетчика, при этом второй вход триггера капала задерживаемых импульсов соединен с выходом дешифратора нуля канала управления задержкой, а второй вход триггера канала управления задержкой подключен к источнику задерживаемых импульсов, отличающееся тем, что, с целью повышения быстродействия, в каждый канал введены пересчетный блок, три дополнительных логических элемента И, дополнительный триггер и формирователь импульсов, при этом вход пересчетного блока через последовательно соединенные первый и второй дополнительные логические элементы И подключен к генератору счетных импульсов, а выход пересчетного блока - ко входу одного из разрядов реверсивного счетчика и к первому входу дополнительного триггера, первый выход которого соединен со вторым входом второго дополнительного логического элемента И, второй выход этого триггера соединен с первым входом первого основного логического элемента И, второй вход которого подключен к выходу первого дополнительного логического элемента И, а второй вход дополнительного триггера подключен ко второму входу первого дополнительного логического элемента И через формирователь импульсов и третий дополнительный логический элемент И, второй вход которого подключен к выходу основного триггера канала; кроме того, вход формирователя импульсов канала задерживаемых импульсов подключен к источнику задерживаемых импульсов, а вход формирователя импульсов канала управления задержкой подключен к источнику импульсов управления. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 396822, кл. И ОЗК 5/153, 23.08.71. 2.Авторское свидетельствоСССР № 573865, кл. Ы ОЗК 5/153, 20.04.75 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство преобразования медленноменяющейся частоты в код | 1977 |

|

SU687589A1 |

| Устройство управляемой задержки импульсов | 1980 |

|

SU936412A1 |

| Многоканальное устройство задержки импульсных сигналов | 1981 |

|

SU945970A1 |

| Умножитель частоты следования импульсов | 1980 |

|

SU923002A2 |

| Устройство для программного счета изделий | 1983 |

|

SU1113824A1 |

| Умножитель частоты следованияиМпульСОВ | 1979 |

|

SU845290A1 |

| Цифровое фазосдвигающее устройство | 1984 |

|

SU1241148A1 |

| Устройство для управленияТиРиСТОРНыМ АВТОНОМНыМ иНВЕРТОРОМ | 1977 |

|

SU794704A1 |

| Устройство выделения первого и пос-лЕдНЕгО иМпульСОВ B пАчКЕ | 1979 |

|

SU839035A1 |

| Устройство формирования и регистрации путевых параметров для управления шахтной подъемной установкой | 1989 |

|

SU1835383A1 |

Авторы

Даты

1981-05-07—Публикация

1978-06-01—Подача