Изобретение относится к автоматике и вычислительной технике и может использоваться для построения различных устройств обработки дискретной информации.

Известно устройство для обнаружения ошибок в параллельном п-разрядном коде с постоянным- весом hi , содержащее 2п входных и два выходных сердечника, диоды и схемы совпадения, при этом выходные парафазные обмотки входного сердечника через диода последовательно соединены с соответствующими данному разряду входными обмотками эаписи или запрета двух выходных сердечников, параллельные ветви обмоток всех разрядов соединены последовательно и замкнуты в кольцо через резистор, выходные обмотки выходных сердечников соединены со схемой совпадения,выход которой сооветствует результату контроля l ,

- Однако в этом устройстве число возможных входов практически оказывается ограниченным несколькими единицами из-за неидентичности характеристик магнитных сердечникоэ и изменения их параметров под

действием внешних факторов, .и времени. Принцип работы устройства, связанный с необходимостью перемагничивания сердечников, не обеспечивает достаточной надежности функционирования из-за неидентичности их параметров.

Кроме того, это устройство имеет импу 1ьсные входные и выходные

сигналы и требует для работы подачи целого ряда синхронизирукнцих сигналов, из-за чего оно плохо согласуется с логическими узлгили современных цифровых устройств, имеющих

потенциальные входные и выходные сигналы.

Наиболее близким к предлагаемому является устройство для обнаружения оишбок в параллельном п-разрядном коде с постоянным весом К, содержащее два пороговых элемента с порогами (К+1) и К, причем выход первого соединен со входом инвертора, соединенного выходом со входом выходного элемента И, второй вход которого соединен с выходом порогового элемента с порогом К 2 ,

Однако.данное устройство имеет большой объем оборудования, так как требует для своей реализации два пороговых элемента сложной логической структуры.

Цель изобретения - -сокращение объемаоборудования.

Указанная цель достигается тем, что в устройство для обнаружения ошибок в параллельном п-разрядном кеде с постоянныги весом К -S- , содержащее блок формирования порога, равного К, блок формирования порога, равного (К+1), элемент НЕ и элемент И, причем выходы блоков формирования порогов К и {К+1) соединены соответственно с первым входом элемента И и со входом элемента НЕ, выход которого соединен- со вторым входом Элемента и, выход . элемента И является выходом устройства, устройство дополнительно содержит первый и второй преобразователи весов входов, выходы каждого из которых соответствуют пороговой функции от 1 до (К+1), причем выходы первого и второго преобразователей весов входов соединены с соответствующими входами блока, формирования порога, равного (К+1), а выходы первого и второго преобразователей весов, соответствующие пороговой функции от 1 до К, соединены с соответствующими входами блока формирования порога, равного К, входы первого преобразователя в&соъ входов соединены с И/2 старшими разрядами контролируемого кода, а входы второго преобразователя соединены с оставшимися младшими разрядами контролируемого кода, а каждый преобразователь весов входов состоит из последовательно соединенных групп пороговых узлов, пороговые узлы первой группы соединены со.входами преобразователя весов входов, а выходы пороговых узлов соединены с соответствующими входами пороговых узлов посдедующей группы, на выходах пороговых узлов 6-й группы; реализуются пороговые функции от 1 д-о 2 о

Построе-ние устройства таким образом обеспечивает сокращение объема оборудования, требуемого для его реализации. Гто достигается за

счет двух преобразователей весов h

( 1 ) входов, являющихся многоTпороговыми, элементами на - ( ) входов. При этом данные преобразователи совместно с блоком формирования порога, равного (К+1), обеспечивают реализацию пороговой функции от п переменных -с порогом (К+1), а совместно с каскадом формирования порога, равного К, обеспечивают реализацию пороговой функции от п переменных с порогом К. Указанная структура устройства позволяет исключить пороговый элемент с порогом К, заменив его блоком формирования данного порога, соединенным входами с выходами преобразователей весов -() входов , образующих совместно с блоком формирования порога, равного (К+1), пороговый элемент на п входов с порого (К+1) .

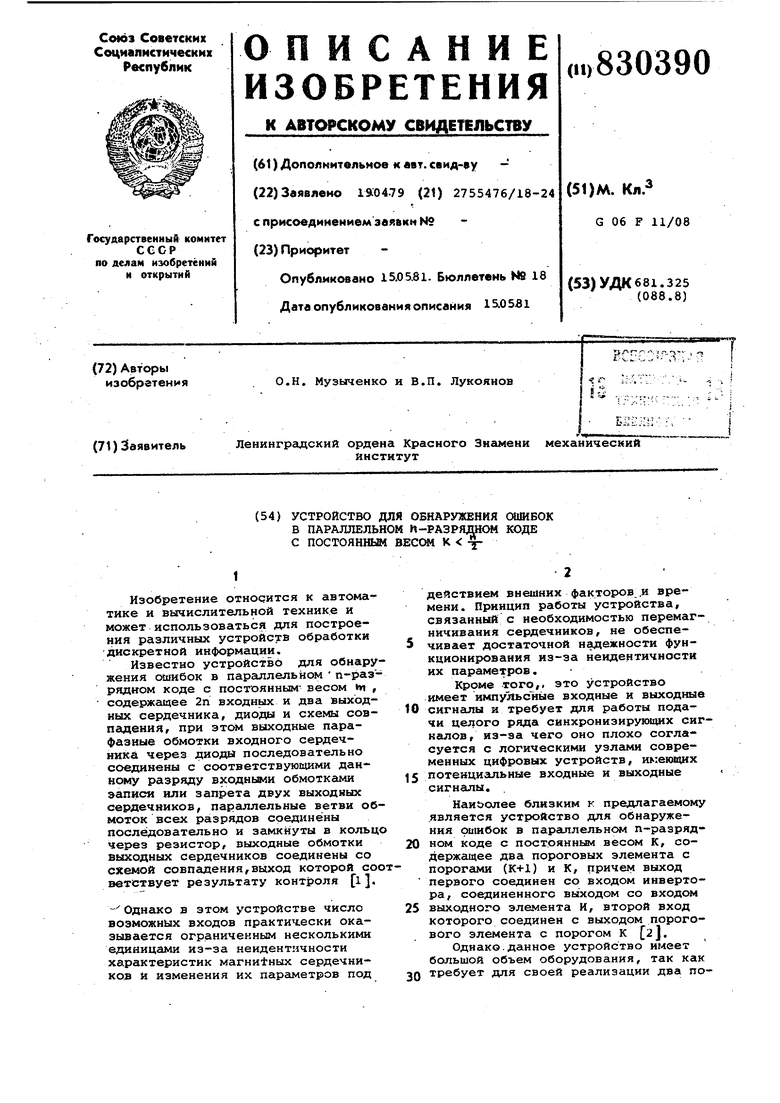

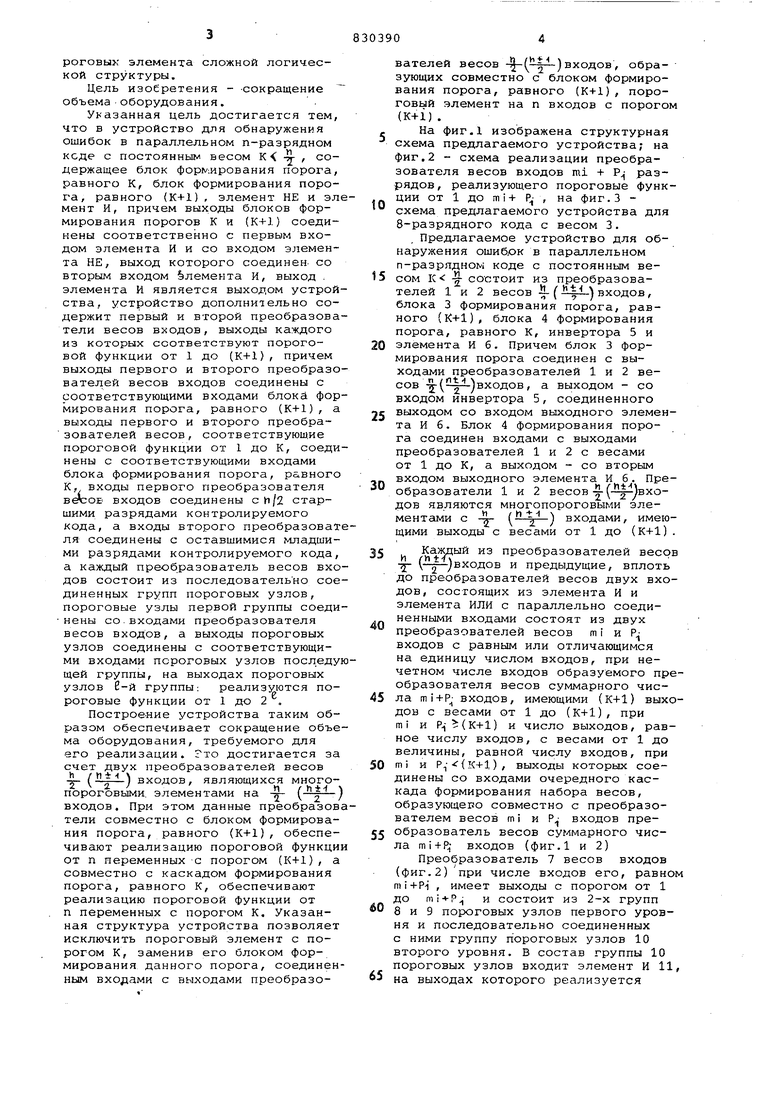

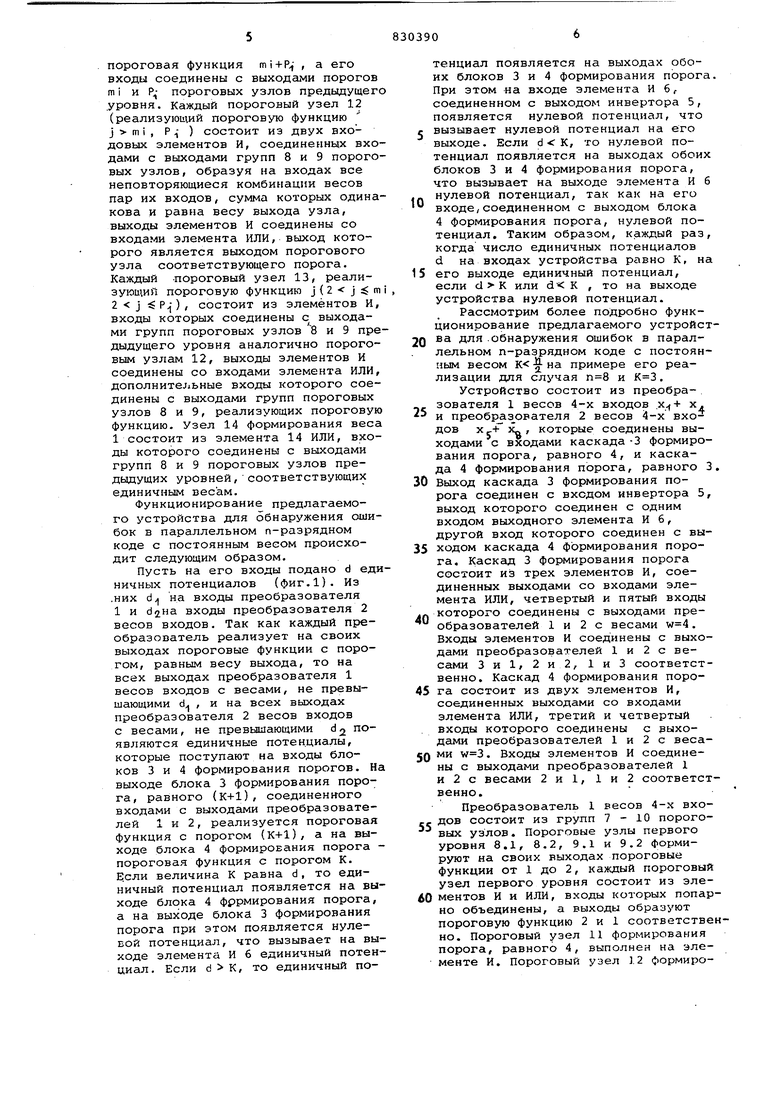

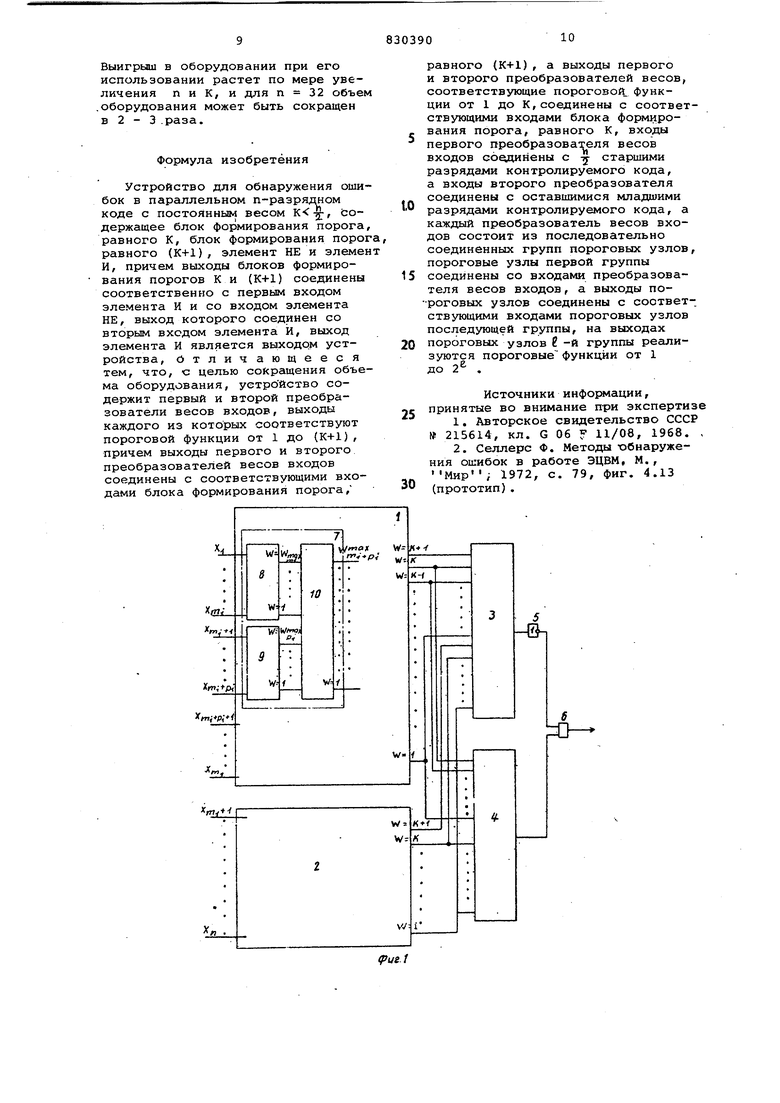

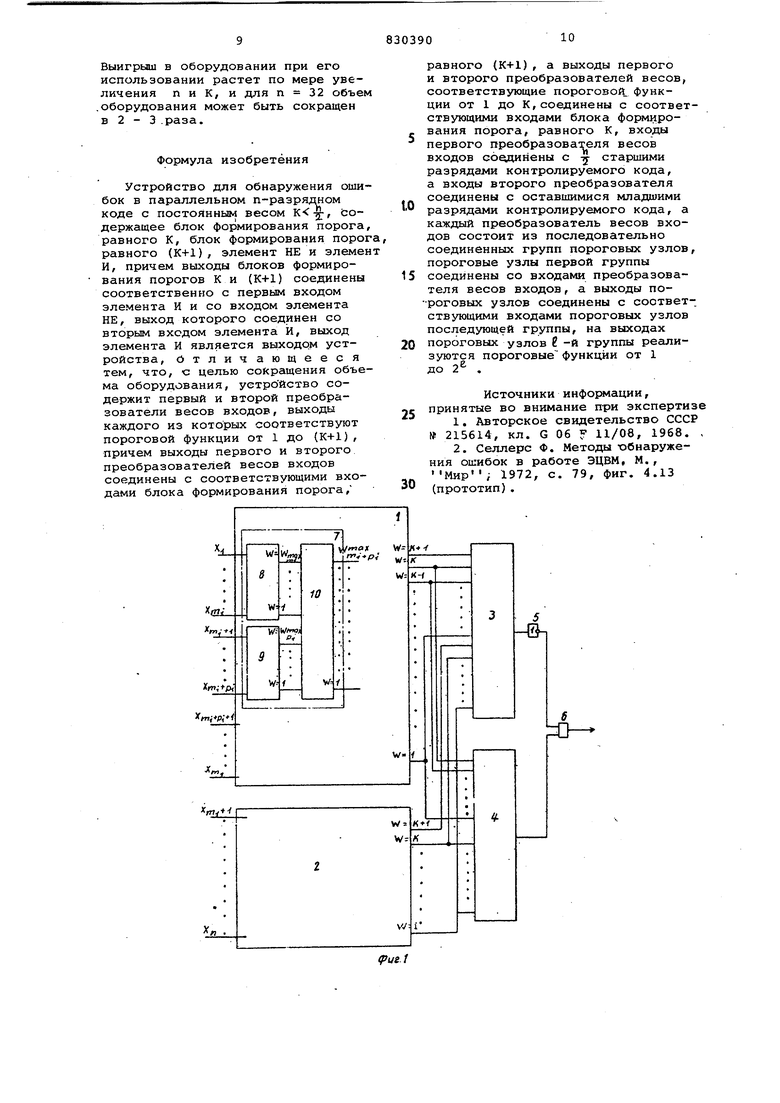

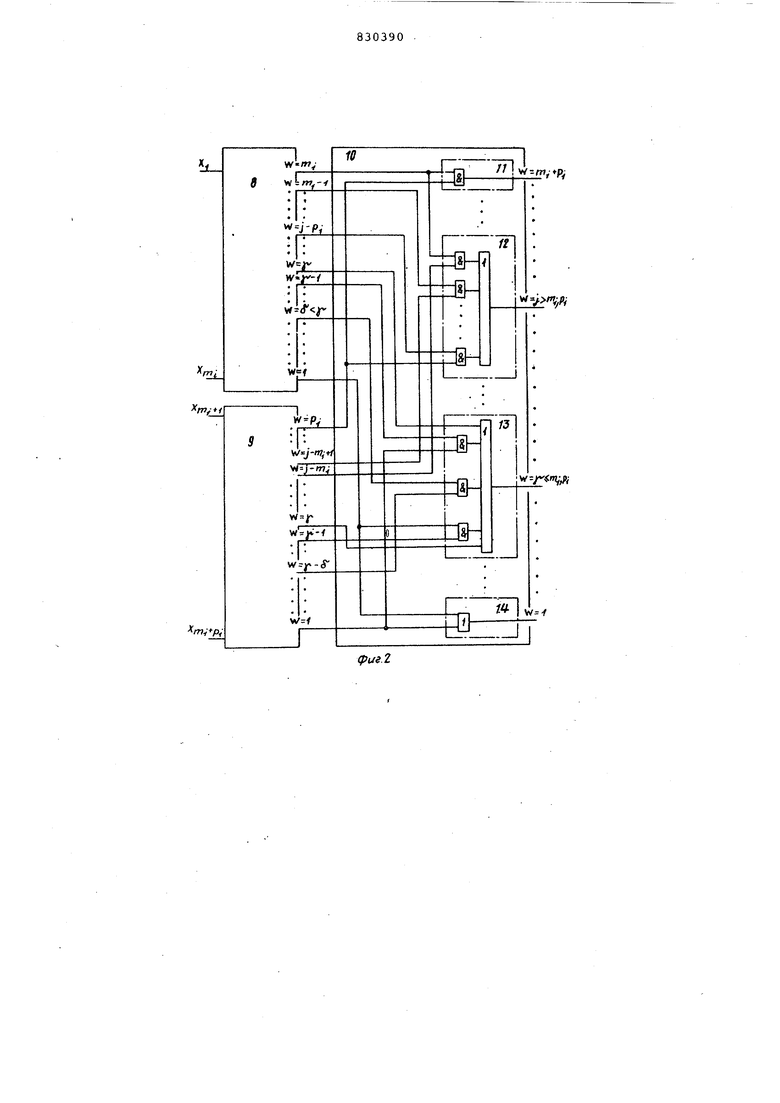

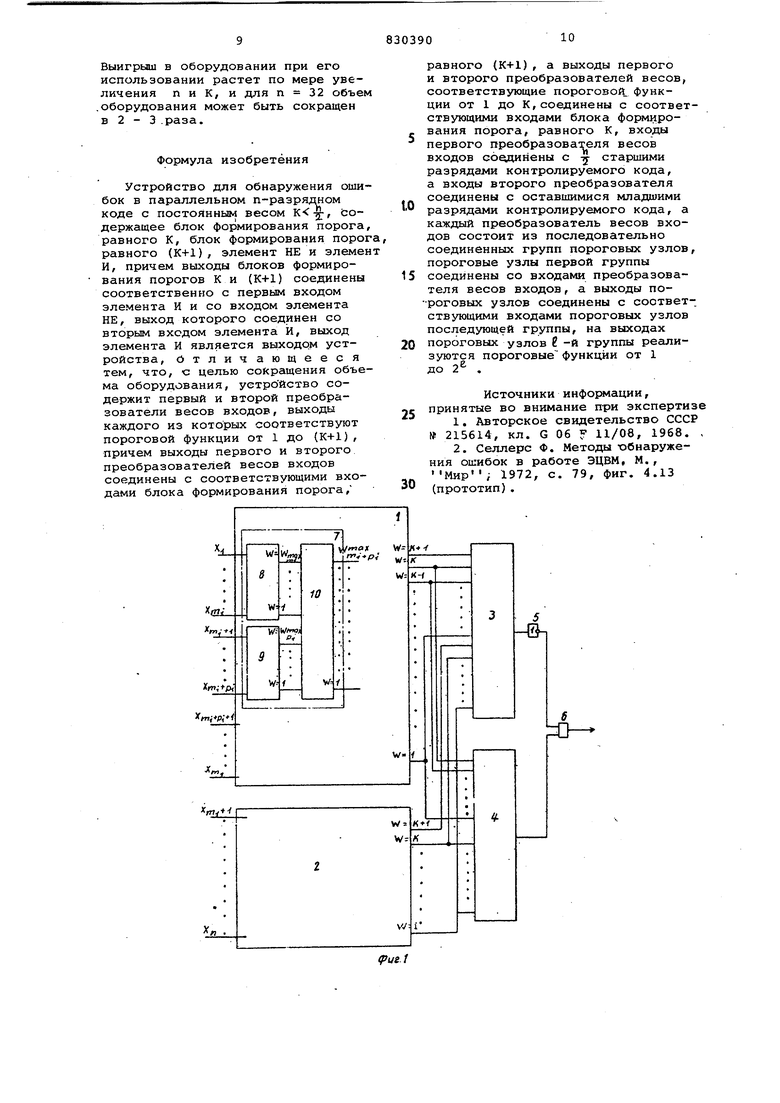

На фиг.1 изображена структурная схема предлагаемого устройства; на фиг.2 - схема реализации преобразователя весов входов mi + разрядов, реализующего пороговые функции от 1 до m i + , на фиг.З схема предлагаемого устройства для 8-разрядного кода с весом 3.

Предлагаемое устройство для обнаружения ошиб/ок в параллельном п-разрядном коде с постоянным весом К -j состоит из преобразователей 1 и 2 весов ( ) входов, блока 3 формирования порога, равного (К+1), блока 4 формирования порога, равного К, инвертора 5 и элемента И б. Причем блок 3 формирования порога соединен с выходами преобразователей 1 и 2 весов -2(у), а выходом - со входом инвертора 5, соединенного выходом со входом выходного элемента И б . Блок 4 формирования порога соединен входами с выходами преобразователей 1 и 2 с весами от 1 до К, а выходом - со вторым входом выходного элемента И б. Преобразователи 1 и 2 весов Y (J xoдов являются многопороговыми элементами с - ( ) входами, имеющими выходы с весами от 1 до (К+1)

Каждый из преобразователей весо -j- (-)входов и предыдущие, вплоть до преобразователей весов двух входов, состоящих из элемента И и элемента ИЛИ с параллельно соединенными входами состоят из двух преобразователей весов m i и Р. входов с равным или отличающимся на единицу числом входов, при нечетном числе входов образуемого пробразователя в-есов суммарного числа mi + входов, имеющими (К+1) выхдов с весами от 1 до (К+1), при mi и 5(К+1) и число выходов, равное числу входов, с весами от 1 до величины, равной числу входов, при mi и Р.,.K+l) , выходы которых соединены со входами очередного каскада формирования набора весов, образующего совместно с преобразователем весов mi и входов преобразователь весов суммарного числа mi+R; входов (фиг.1 и 2)

Преобразователь 7 весов входов (фиг.2) при числе входов его, равно mi+Pi , имеет выходы с порогом от 1 до и состоит из 2-х групп 8 и 9 пороговых узлов первого уровня и последовательно соединенных с ними группу пороговых узлов 10 второго уровня, в состав группы 10 пороговых узлов входит элемент И 11 на выходах которого реализуется

пороговая функция , а его входы соединены с выходами порогов mi и Р,- пороговых узлов предыдущег уровня. Каждый пороговый узел 12 (реализующий пороговую функцию j m i , Р - ) состоит из двух входовых элементов И, соединенных входами с выходами групп 8 и 9 пороговых узлов, образуя на входах все неповторяющиеся комбинации весов пар их входов, сумма которых одинакова и равна весу выхода узла, выходы элементов И соединены со входами элемента ИЛИ, выход которого является выходом порогового узла соответствующего порога. Каждый -пороговый узел 13, реализующий пороговую функцию j{2 j m 2 j ), состоит из элементов И, входы которых соединены с выходами групп пороговых узлов 8 и 9 предыдущего уровня аналогично пороговым узлам 12, выходы элементов И соединены со входами элемента ИЛИ, дonoлнитeJiЬныe входы которого соединены с выходами групп пороговых узлов 8 и 9, реализующих пороговую функцию. Узел 14 формирования веса 1 состоит из элемента 14 ИЛИ, входы которого соединены с выходами групп 8 и 9 пороговых узлов предыдущих уровней, соответствующих единичным весам.

Функционирование предлагаемого устройства для обнаружения ошибок в параллельном п-разрядном коде с постоянным весом происходит следующим образом.

Пусть на его входы подано d единичных потенциалов (фиг.1). Из .них d;) на входы преобразователя 1 и входы преобразователя 2 весов входов. Так как каждый преобразователь реализует на своих выходах пороговые функции с порогом, равным весу выхода, то на всех выходах преобразователя 1 весов входов с весами, не превышающими d , и на всех выходах преобразователя 2 весов входов с весами, не превышающими d появляются единичные потенциалы, которые поступают на входы блоков 3 и 4 формирования порогов. На выходе блока 3 формирования порога, равного (К+1), соединенного входами с выходс1ми преобразователей 1 и 2, реализуется пороговая функция с порогом (К+1), а на выходе блока 4 формирования порога пороговая функция с порогом К. Если величина К равна d, то единичный потенциал появляется на выходе блока 4 формирования порога, а на выходе блока 3 формирования порога при этом появляется нулевой потенциал, что вызывает на выходе элемента И 6 единичный потенциал. Если d К, то единичный потенциал появляется на выходах обоих блоков 3 и 4 формирования порога. При этом на входе элемента И 6, соединенном с выходом инвертора 5, появляется нулевой потенциал, что е вызывает нулевой потенциал на его вьлходе. Если d К, то нулевой потенциал появляется на выходах обоих блоков 3 и 4 формирования порога, что вызывает на выходе элемента И 6 нулевой потенциал, так как на его входе,соединенном с выходом блока 4 формирования порога, нулевой потенциал. Таким образом, каждый раз, когда число единичных потенциалов d на входах устройства равно К, на

5 его выходе единичный потенциал, если или d К , то на выходе устройства нулевой потенциал.

Рассмотрим более подробно функционирование предлагаемого устройства для .обнаружения ощибок в параллельном п-разрядном коде с постоянным весом К - на примере его реализации для случая и .

Устройство состоит из преобра- зователя 1 весов 4-х входов . х.

и преобраз ователя 2 весов 4-х входов х, которые соединены выходами с входами каскада -3 формирования порога, равного 4, и каскада 4 формирования порога, равного 3.

0 Выход каскада 3 формирования порога соединен с входом инвертора 5, выход которого соединен с одним входом выходного элемента И б, другой вход которого соединен с выходом каскада 4 формирования порога. Каскад 3 формирования порога состоит из трех элементов И, соединенных выходами со входами элемента ИЛИ, четвертый и пятый входы

которого соединены с выходами пре0

образователей 1 и 2 с весами . Входы элементов И соединены с выходами преобразователей 1 и 2 с весами Зи1/2и2, 1иЗ соответственно. Каскад 4 формирования порога состоит из двух элементов И, соединенных выходами со входами элемента ИЛИ, третий и четвертый входы которого соединены с рыходами преобразователей 1 и 2 с весаQ ми . Входы элементов И соединены с выходами преобразователей 1 и 2 с весами 2 и 1, 1 и 2 соответственно.

Преобразователь 1 весов 4-х входов состоит из групп 7-10 порого5вых узлов. Пороговые узлы первого уровня 8.1, 8.2, 9.1 и 9.2 формируют на своих выходах пороговые функции от 1 до 2, каждый пороговый узел первого уровня состоит из элементов И и ИЛИ, входы которых попарно объединены, а выходы образуют пороговую функцию 2 и 1 соответственно. Пороговый узел 11 формирования порога, равного 4, выполнен на элементе И. Пороговый узел 12 формирования порога, равного 3, состоит из двух элементов И и элемента ИЛИ На входы элементов И поступают вых ды групп 8 и 9 пороговых узлов пре дыдущих уровней, с порогом 2 и 1 на первый элемент И и 1 и 2 на вто ро.й. Пороговый узел формирования порога 2 состоит из элемента И, со диненного входами с выходами групп пороговых узлов предыдущего уровня 8.1, 8.2 (9.1, 9.2) на выходах которых реализуется пороговая функ ция, равная единице, и элемента ИЛИ, соединенного одним выходом с выходом элемента ИЛИ, а двумя дополнительными входами с выходами группы пороговых УЗЛОВ, реализующих пороговую функцию 2. Пороговый узел 14 формирования порога, равно го 1, выполнен на элементе ИЛИ, входы которого соединены с выхода ми пороговых узлов предыдущей гру пы 8.1, 8.2 (9.1, 9.2), реализующих порог, равный 1. На выходах преобразователей весов двух входо реализуются функции И и ИЛИ, являющиеся пороговыми функциями от дву переменных с порогами,равными 2 и соответственно, т.е. с порогами, ра вными весам выходов. На выходах преобразователя 1.и 2, например выходе преобразователя 1, реализуются функции: f4 UHXi ).(х,Х4) , которые являются пороговыми функц ми 4-х переменных с порогами 1т.е. с порог-ами, равными весам вы ходов . Пусть на входы преобразователя 1 .подано 2 единичных потенциала, при этом единичные потенциалы поя ются на его выходах с весами и , которые поступают на входы элементов И блоков 3 и 4. Однако вторых входах всех элементов И указанных блоков, а также на входах элементов ИЛИ, соединенных с выходами преобразователей 1 и 2 имеются нулевые потенциалы, .при этом нулевые потенциалы появляются на выходах блоков 3 и 4, а сле довательно, и на выходе элемента И 6 , являющемся выходом устройства. При подаче единичного потенциала на один из входов преобразователя 2 единичный потенциал появляется на его выходе с единичным весом и поступает на входы элемен тов И блоков 3 и 4. При этом на входах элемента И блока 4, соединенного входами с выходами преобразователер 1 и 2 с весами и w lcooTBeTCTBeHHO, появляются единичные потенциалы, что вызывает единичный потенциал на его выходе на выходе элемента ИЛИ, являющемся выходом блока 4. При этом на обоих входах элемента И 6 появляются единичные потенциалы, что вызывает единичный потенциал на его выходе, являющемся выходом устройства. Пусть на вход преобразователя 1 подан еще один единичный потенциал, при этом единичный потенциал по- .. является на его выходе с весом . Единичный потенциал с данного выхода преобразователя 1 поступает на вход элемента ИЛИ блока 4, подтверждая единичный потенциал на его выходе, а также на вход элемента И блока 3, второй вход которого соединен с выходом преобразователя 2 с единичным весом. При этом на выходе данного элемента И появляется единичный потенциал, который вызывает единичный потенциал на выходе элемента ИЛИ, являющемся выходом блока 3. При этом на выходе инвертора 5 появляется нулевой потенциал, который вызывает нулевой потенциал на выходе элемента И б , являющемся выходом устройства. Таким образом, единичный потенциал на выходе устройства появляется только в тех случаях, когда на его входах точно 3 единичных потенциала, независимо от того, на какие входы они поданы. Построение устройства для об- . наружения ошибок в параллельном п-разрядном коде с постоянным весом К)1/2. предлагаемой структуры позволяет сократить объем оборудования для его реализации. Так для реализации известного и предлагаемого устройства при требуется элементов И и ИЛИ (без учета ограничений по числу входов) для п 8 - 40 и 26 соответственно, для п 16 - 81 и 58, для п 32 164 и 122, для п 64 - 299 и 250, Однако более точным показателем сложности является количество двухвходовых элементов И и ИЛИ, которое составляет для известного и предлагаемого устройства соответственно: для п 8 - 53 и 31, п 16 - 151 и 71, п 32 - 489 и 151, п 64 - 1547 и 309. Следовательно, выигрыш в оборудовании при использовании предлагаемого устройства составляет по количеству элементов, без учета реальных ограничений на число входов: для п 8 - в 1,54 раза, для п 16 - в 1,4 раза, для п 32 - в 1,35 раза, для п 64 - в 1,17 раза. А по объему оборудования (по числу двухвходовых элементов) для п 8 в 1,7 раза, для п 16-в2,13 раза, для п 32 - в 3,15 раза, для п 64 - в 5 раз. Таким образом, предлагаемое устройство требует для реализации существенно меньшего объема оборудования по сравнению с известным.

Выигрыш в оборудовании при его использовании растет по мере увеличения п и К, и для п 32 объем .оборудования может быть сокращен в 2 - 3 .раза.

Формула изобретения

Устройство для обнаружения ошибок в параллельном п-разрядном коде с постоянным весом К , Содержащее блок формирования порога, равного К, блок формирования порог равного (К+1), элемент НЕ и элемен И, причем выходы блоков формирования порогов К и (К+1) соединены соответственно с первым входом элемента И и со входом элемента НЕ, выход которого соединен со вторым входом элемента И, выход элемента И является выходом устройства, Отличающееся тем, что, с целью сокращения объема оборудования, устройство содержит первый и второй преобразователи весов входов, выходы каждого из которых соответствуют пороговой функции от 1 до (К+1), причем выходы первого и второго преобразователей весов входов соединены с соответствующими входами блока формирования порога,

равного (К+1), а выходы первого и второго преобразователей весов, соответствующие пороговой функции от 1 до К,соединены с соответствующими входами блока формирования порога, равного К, входы первого преобразователя весов входов соединены с -j старшими разрядами контролируемого кода, а входы второго преобразователя соединены с оставшимися младшими

0 разрядами контролируемого кода, а каждый преобразователь весов входов состоит из последовательно соединенных групп пороговых узлов, пороговые узлы первой группы

5 соединены со входами преобразователя весов входов, а выходы пороговых узлов соединены с соответ-, ствующими входами пороговых узлов последующей группы, на выходах пороговых узлов 2-и группы реали0зуются пороговые функции от 1 до 2 .

Источники информации, принятые во внимание при экспертизе

5

1.Авторское свидетельство СССР 215614, кл. G 06 11/08, 1968. ,

2.Селлерс Ф. Методы обнаружения ошибок в работе ЭЦВМ, М., 1972, с. 79, фиг. 4.13

0 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Пороговый логический элемент | 1981 |

|

SU991612A1 |

| Устройство для обнаружения ошибок в параллельном @ -разрядном коде с постоянным весом @ | 1981 |

|

SU1027729A1 |

| Пороговый логический элемент | 1981 |

|

SU1005317A1 |

| Пороговый логический элемент | 1981 |

|

SU1005316A1 |

| Пороговый элемент | 1981 |

|

SU1046932A1 |

| Устройство для умножения по модулю К | 1989 |

|

SU1691834A1 |

| Пороговый элемент | 1987 |

|

SU1584098A1 |

| Пороговый элемент (его варианты) | 1980 |

|

SU1034188A1 |

| Пороговый элемент | 1983 |

|

SU1126924A1 |

| Аналого-цифровой преобразователь изображений | 1989 |

|

SU1803902A1 |

Авторы

Даты

1981-05-15—Публикация

1979-04-19—Подача