i (54) пороговый ЛОГИЧЕСКИЙ ЭЛЕМЕНТ

| название | год | авторы | номер документа |

|---|---|---|---|

| Пороговый логический элемент | 1981 |

|

SU1005317A1 |

| Пороговый логический элемент | 1987 |

|

SU1506544A1 |

| Пороговый логический элемент | 1987 |

|

SU1510078A1 |

| Пороговый элемент | 1987 |

|

SU1584098A1 |

| Пороговый элемент | 1983 |

|

SU1126924A1 |

| СПОСОБ ПОЛНОГО СЛОЖЕНИЯ - ВЫЧИТАНИЯ ЧИСЕЛ, КОДИРУЕМЫХ СИГНАЛАМИ, И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1998 |

|

RU2132566C1 |

| ПОРОГОВЫЙ ЭЛЕМЕНТ | 1987 |

|

RU2034401C1 |

| Многофункциональное вычислительное устройство | 1985 |

|

SU1293727A1 |

| Запоминающее устройство | 1982 |

|

SU1023393A1 |

| Генератор сочетаний | 1984 |

|

SU1166090A1 |

1

Изобрегение огнсюигся к авгомагике и вычислительной технике и можег быть использовано для построения раэ- личных устройств переработки дискрет ной информации.

Известен пороговый логический элемент, содержащий многовходовой элемент ИЛИ, входы которого соединены с выходами пяти трехвходовых элементов И, две группы по четыре цвухвхоцовых элемента ИЛИ, соединенных со входами элементов И Cl Т .

Недостатком данного элемента являются ограниченныефункциональные возможности, так как он реализует только пороговую функцию семи переменньк с порогом 3.

Известен также мажоритарный логический элемент, содержащий преобразователи весов двух входов, состоящие, из элемента И и элемента ИЛИ с параллельно соединенными входами, блок формирования порога Н выходной элемент ИЛИ. Блок формирования порога выполнен пвухступенчатым, содержащим два однотипных каскаоа формирования набора весов первой сту1юни, взаимно-дополняющие, весовью выходы которых попарно соеци нены со входами элементов И каскада формирования порога второй ступени С23.

Недостатком таких устройств является малые функциональные возможности.

10

Наиболее близким по технической сущности к изобретению является пороговый логический элемент, содержащий К столбцов сумматоров, входы сумматоров первого столбца из которых под15ключены к одним шинам входных сиг налов СЗ 3 ;

Недостатками такого устройства явnЯi ются сложность технической реализации, малые функциональные возможности и

20 малое быстродействие.

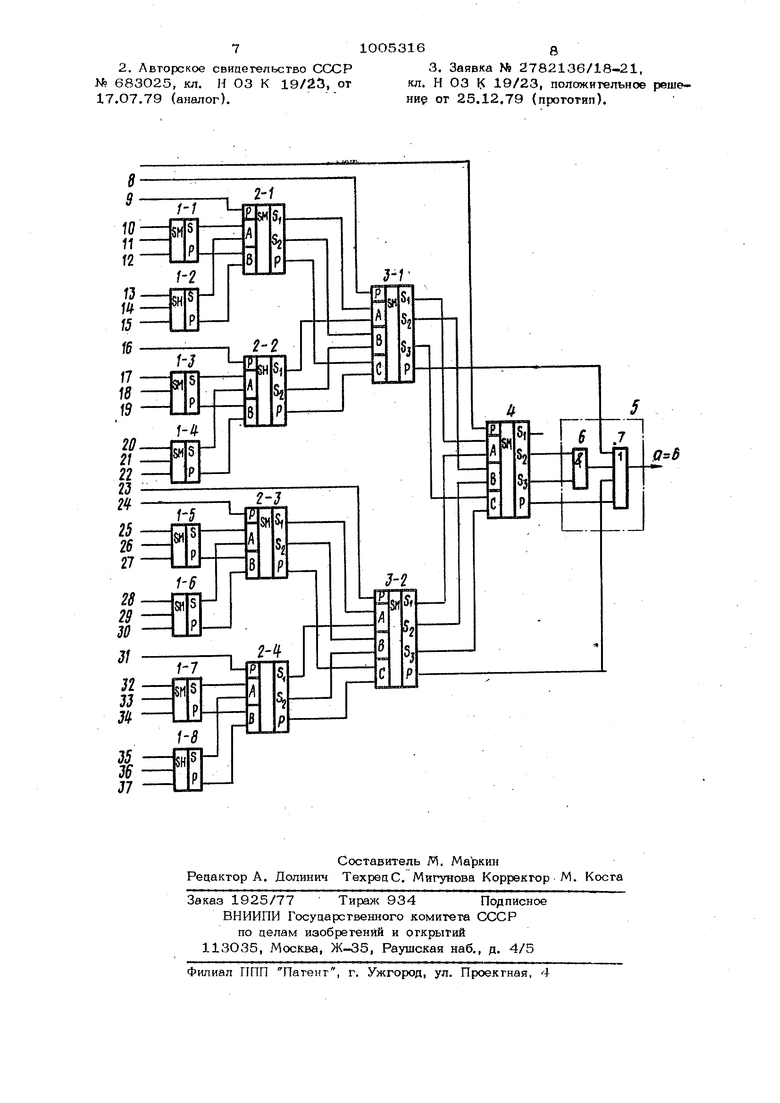

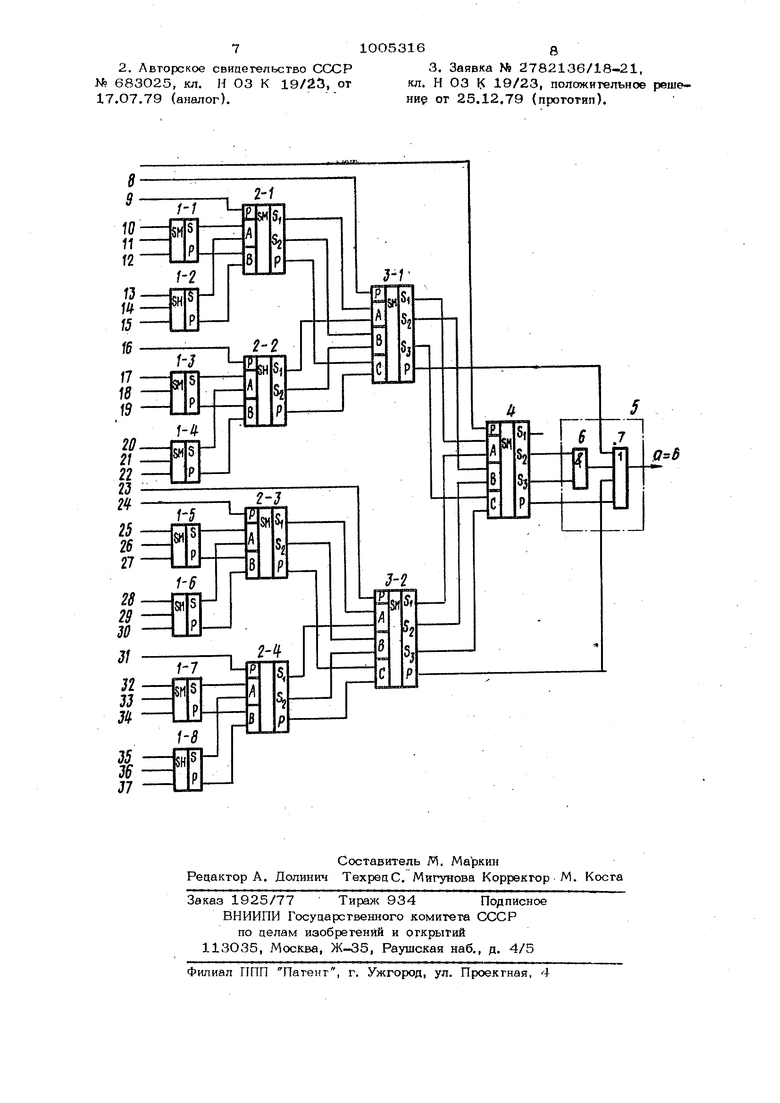

Цель изобретения - повьш1ение быстродействия и расширения функциональных возможностей. Для достижения поставленнойцели в пороговый логический элемент, содержащий К столбцов суммгзторов, входы сумматоров первого столбца подключены к шинам входных сигналов, введен блок формирования порога, выход которого подключен к шине входных сигналов, а входы - к выходам сумматора последне- столбца и выходам переноса суммато ров столбцов от Р-го до К-го, для Р--1р порога в пределах от 2 до 2, а выходы каждого из сумматоров столбцов от первого до (р-1)го подключены к входам одного из сумматоров последующих столбцов, выходы суммы каждого из сумматоров остальных столбцов подключены к входам одного из сумматоров последующих столбцов, при этом входы переноса сумматоров всех столбцов подключены к шинам входных сигналов. На чертеже изображен предлагаемый пороговый; логический элемент для случая числа входов п -31 и порога С 6. Предлагаемый пороговый элемент для случая и а 6 состоит из сумматоров , входы которых подключены к входным шинам порогового логического элемента, сумматоров 2-1-2-4 двухразрядных двоичных чисел, сумматоров 3-1, 3-2, 4 трехразрядных двоичных чисел, блок формирования порога 5 и элементов И 6 и ИЛИ 7, входы 8-37. Выходы каждых двух сумматоров 1 соединенысо входами соответствующего сумматора 2, вход переноса которого соединен с входом порогового элемента. ВЗыходы сумматоров 2-1 и 2-2 соединены с входами сумматора 3-1, а выходы сумматоров 2-3 и 2-4 - со входами сум матора 3-2. Выходы суммы сумматоров 3-1 и 3-2 Р-разряцных двоичных чисел () соединены ио входами поч (Слецнего сумматора 4 трехразрядных двоичных чисел, вход переноса которого соединен со входной шиной порогового элемента. Входы переноса сумматоров 3-1 и 3-2 соединены со входами порогового логического элемента. Выходы сумматора 4, начиная с Т-го (), и выходы. переноса сумматоров 3-1, 3-2, 4 соединены со входами блока формирования порога, входы которого подключены к входам элементов И 6 и ИЛИ 7. Двоичное представление порога Q рав- но 2 +i-2 1-2, В соответствии с этим второй и третий выходы суммагора 4 соединены со входами элемента И 6, выход которого, а также выходы переноса сумматоров 3-1, 3-2 и 4 соединены со входами элемента ИЛИ 7. Функционирование предлагаемого порогового логического элемента для случая с тридцатью одним входом и порогом а 6 происходит следующим образом. На выходах каждого из сумматоров 1 формируется двоичный код числа единич- Hbtx потенциалов на их входа с. Двоичные коды с выходов каждого из сумматоров 1 поступают на входы соответствующего сумматора 2, на выходах при этом формируется двоичный код числа единичных потенциалов на соответствующих семи входах. Так на входах сумматора 2-1 формируется двоичный код числа гп единичньрс потенциалов на входах 10-16. Причем на выходе переноса сумматора 2-1 появляется единичный потенциал, если число гп единичных потенциалов на входах 10-16 больше или равно 4. Двоичные коды с выходов сумматоров 2 поступают на входы соответствующего сумматора 3, на выходах которого при этом формируется двоичный -. код числа m единичных потенциалов на соответствующих пятнадцати входах. Так на выходах сумматора 3-1 формируется двоичный код числа т,, единичных потенциалов на входах 9-23. Причем на выходе переноса сумматора 3-1 появляется единичный потенциял, если число ТЦ 7 единичных потенциалов на входах . 9-23 больше или равно 8. На выходах суммы сумматора 3-1 формируется код числа -Ь,,,где т -число единичных потенциалов на входах 9-23. На выходах сумматора 3-2 формируется двоичный код числа rrti единичных потенциалов на входах 24-37, Причем на выходах суммы сумматора 3-2 фо{ мируется двоичный код числа -fcn 7 -Cm2./8}.8. Двоичные коды чисел -t-i и -t2 с выходов суммы сумматоров 3-1, 3-2 . поступают на входы сумматора 4, на выходах которого формируется двоичный код числа i -fe2 3 на вход переноса сумматора 4 подан единичный потенциал, и з сли на данный вход подан нулевой потенциал. На выходе переноса сумматора 4 поя&ляется единичный потенциал, если ® ® выходах суммы данного сумматора формируется двоичный код числа -fc1- t2 3-0(1+t2 ti /-82 . 51О Таким образом, всякий раз, когца число tn единичных потенциалов на входах порогового логического элемента больше или равно 8, на выходах перенос суммато юв 3-1, 3-2, 4 появляется единичных потенциалов. Например, при поцаче m : 8 единичных потенциалов на входы 9-23 единич- нь1й потенциал появляется на выходе переноса сумматора 3-1. Появление еци- ничиого потенциала на выходе переноса сумматоров 3-1, 3-2, 4 вызывает появление единичного поте нциала на выходе элемента ИЛИ 7. При поцаче на входы порогового логического элемента m 8 единичных потенциалов на выходах суммы сумматора 4 появляется двоичный код числа rtv ; Если или , единичные потенциалы появляются на втором и третьем выходах сумматора 4 (выходах 82 и За) соединенньЕх; с входами элемента И 6, При этом на выходе элемента И 6 появляется-единичный потенциал, который вызывает единичный потенциал на выходе элемента ИЛИ 7. Если число m единичных потенциалов на входах порогового логического элемента меньше 6, то единичный потенциал появляется только на втором или третьем выходе сумматора 4, т.е. на выходе элемента И 6 будет нулевой потенциал. На выходах переноса сумматоров 3-1, 3-2, 4 при этом будут нулевые потенциалы. Следовательно-на всех входах элемента ИЛИ 7 и на его выходе будут нулевые потенциалы. Таким образом, всякий раз, когда число единичных потенциалов на входах порогового логического элемента больше и ..равно порогу, на его выходе появляет ся единичный потенциал. Следовательно,, предлагаемый пороговый логический элемент обладает значительно большими функциональными возможностями по сравнению с прототипом так как реализует любую пороговую фун цию с порогом с 2}Boaj2() Of любого числа переменных. И. . jf trTit.TV fri Кроме того, предлагаемый элемент имеет большее быстродействие, чем про тотип. Например,для случая протот имеет время задержки Т-(8-18)1 гд ТГа - время задержки переключения полного сумматора в Ьависимости от поряа ка соединения сумматоров в блоках сло жения по модулю два. В предложенном устройстве при п 31 и время за держки равно Т2 Сз 2Сз | ® 6 2 - время задержки двухразрядного сумматора, Та - время задержки грехраэрядного- сумматора, т: - время задержки блока формирования порога 5. В большинстве случаев можно считать .ь /ч Tf У 3- Например, для элементов cepHH lSS tig Jf 8Онс, Т 42 не, 1Г| 48 НС. При этом , т.е. предлагаемое устройство обеспечивает примерно в 1,5-3 раза большее быстро- действие. Кроме того, предлагаемое устройство обеспечивает уменьшение объема обору дования. Так прототип требует для реализации 26 сумматоров, а предлагаемое устройство 25. При реализации на микросхемах серии 155 прототип требует 26 микросхем, а предлагаемое - 16, , т.е. в 1,5 раза меньше. При 63 прототип содержит 57 сумматоров, а предлагаемое устройство для ся 5-7 только 53, а для сумматоров. При реализации на микросхемах серии 155 для реализации прототипа требуется 57 микросхем, а для предлагаемого устройства - 31 микросхемаФормула изобретения Пороговый логический элемент, содержащий К столбцов сумматоров, входы сумматоров первого столбца подключены к шинам входных сигналов, о т л и«чающийс я тем, что, с целью повышения быстродействия, упрошения и расширения функциональных возможностей, в него введен блок формирования порога, выход которого подключен к шине выходных сигналов, а входы - к . Ьыхоцам сумматора последн,его столбца и выходам переноса сумматоров столбцов от Р-го до1С-го, для порога в пределах 2 Р - 2 , а выходы каждого из сумматоров столбцов от первого до {р-1)-го подключены к входам одного из сумматоров последующих столбцов, выходы суммы каждого из сумматоров остальных столбцов подключены к входам одного из сумматоров последующих столбцов, при этом входы переноса сумматоров всех-столбцов подключены к шш&ы входных сигналов. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР N9 598252, кл. Н 03 К 19/24, от О7.О5.76 (аналог).

71ОО53168

№ 683025, кл. И 03 К 19/23, от 17.07.79 (аналог).

кл. Н 03 15 19/23, положительное решение от 25.12.79 (прототип).

пТ1

Авторы

Даты

1983-03-15—Публикация

1981-04-28—Подача