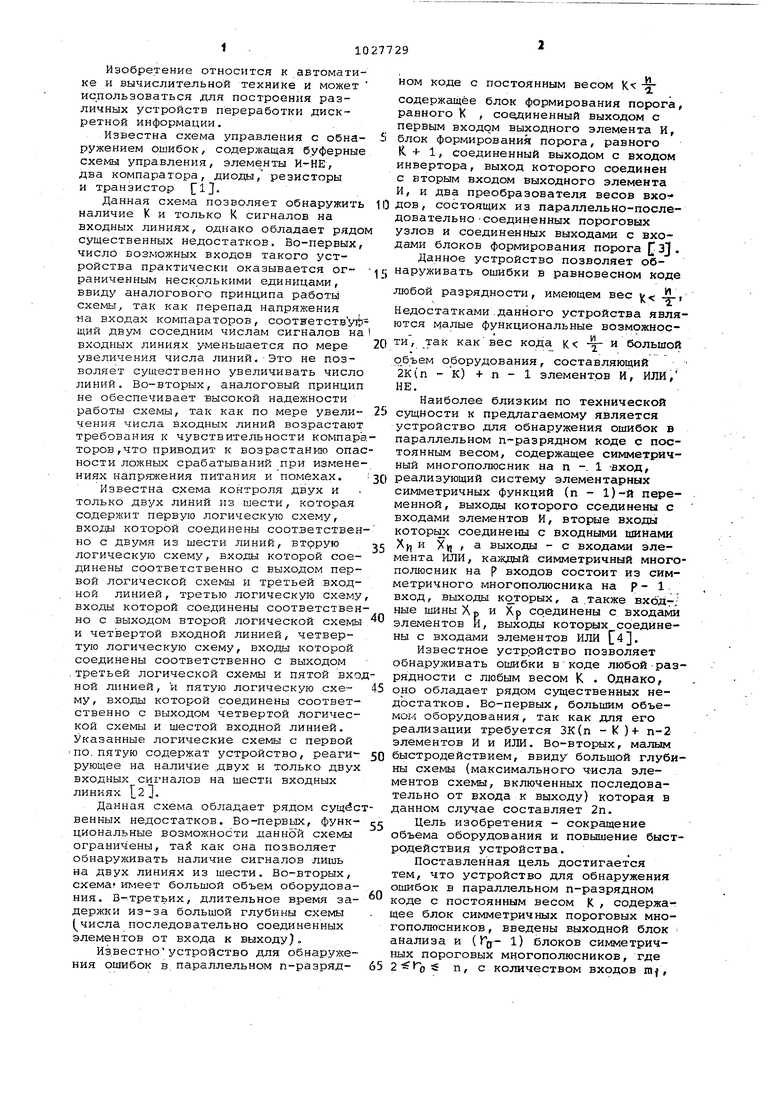

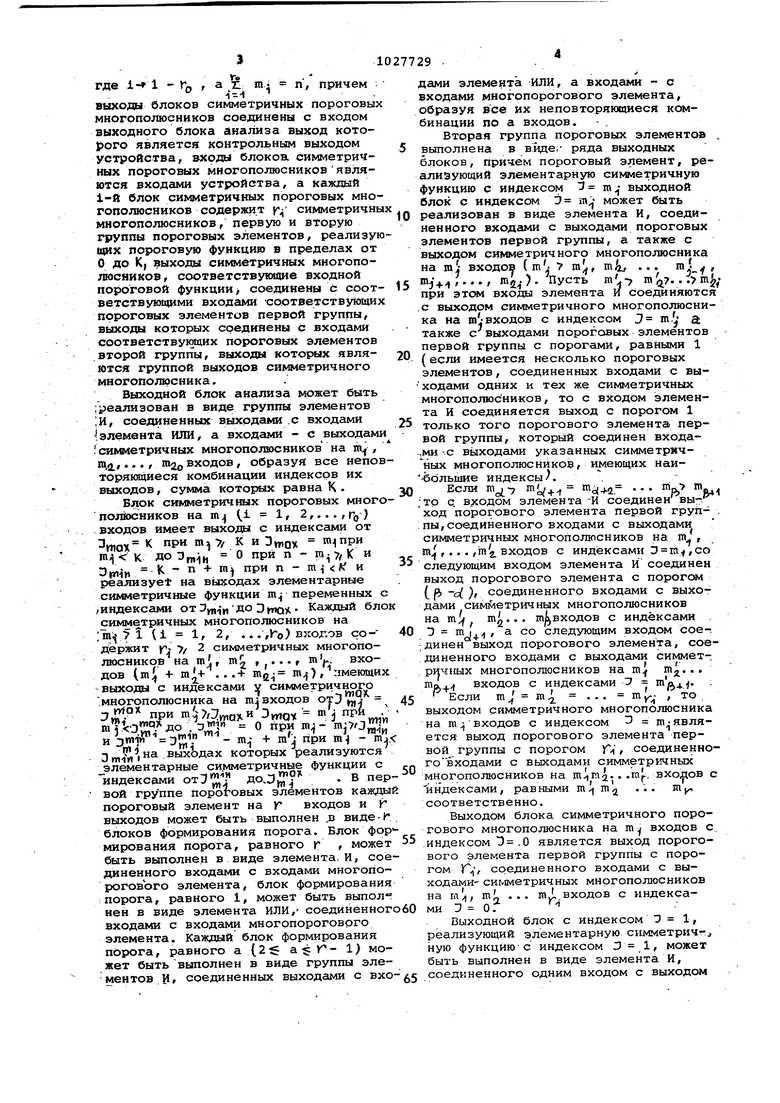

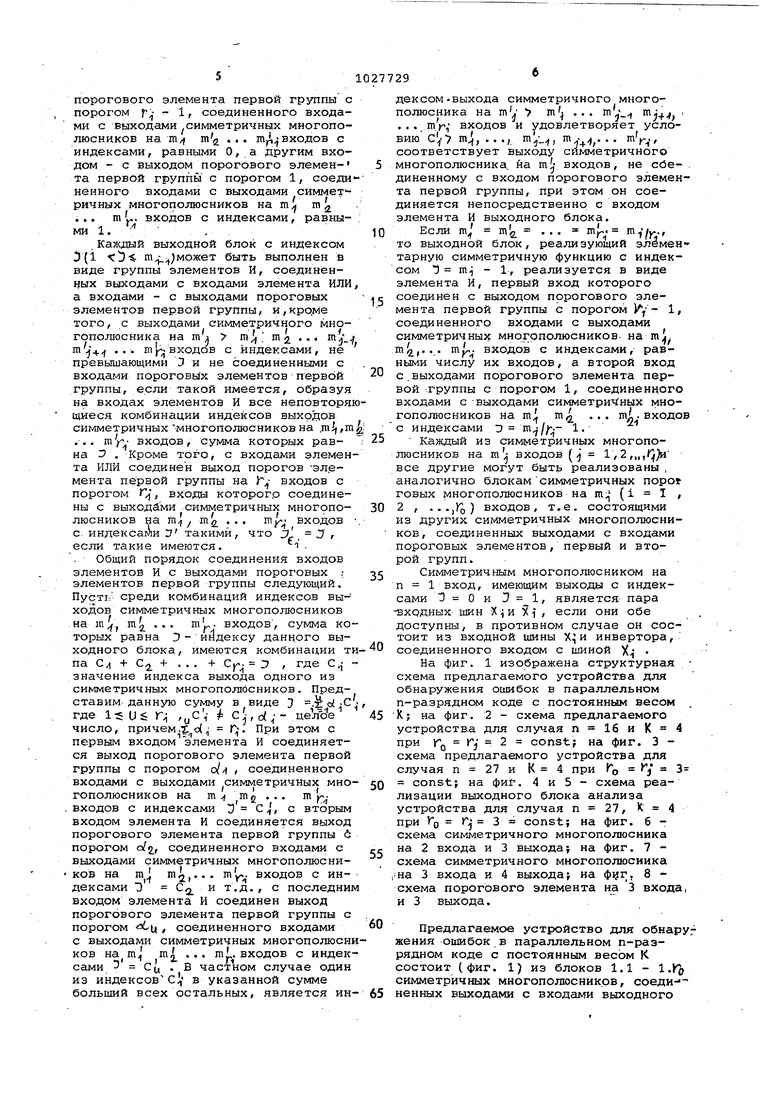

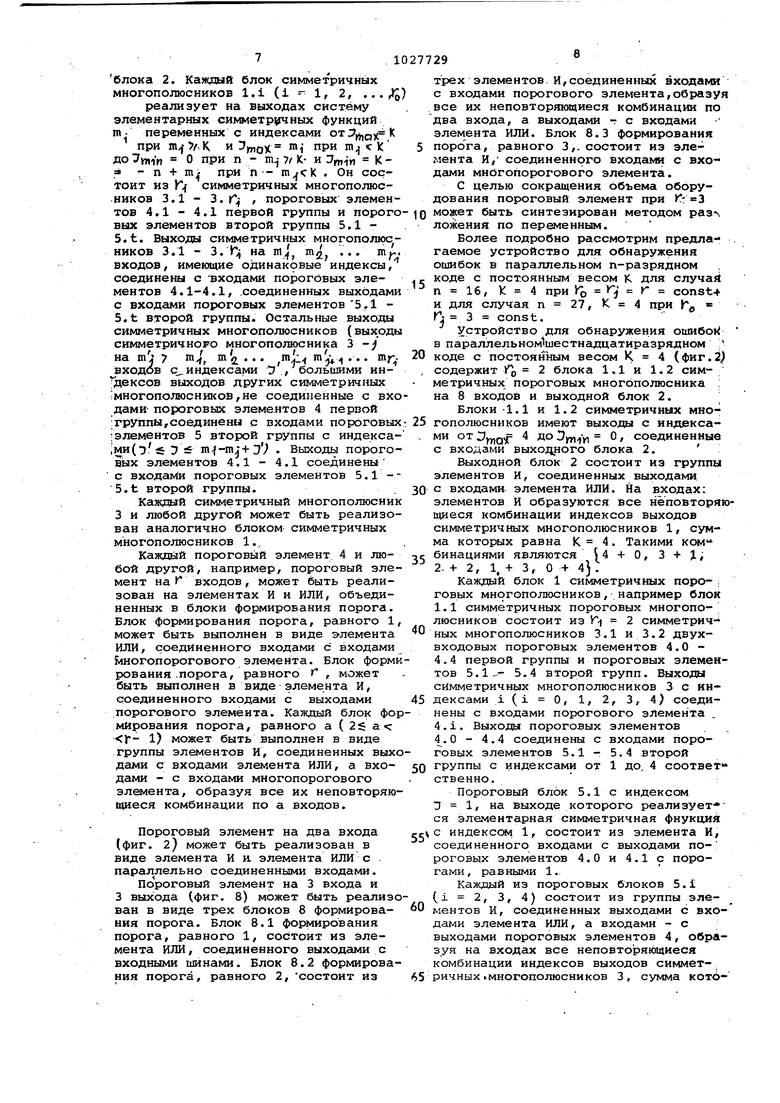

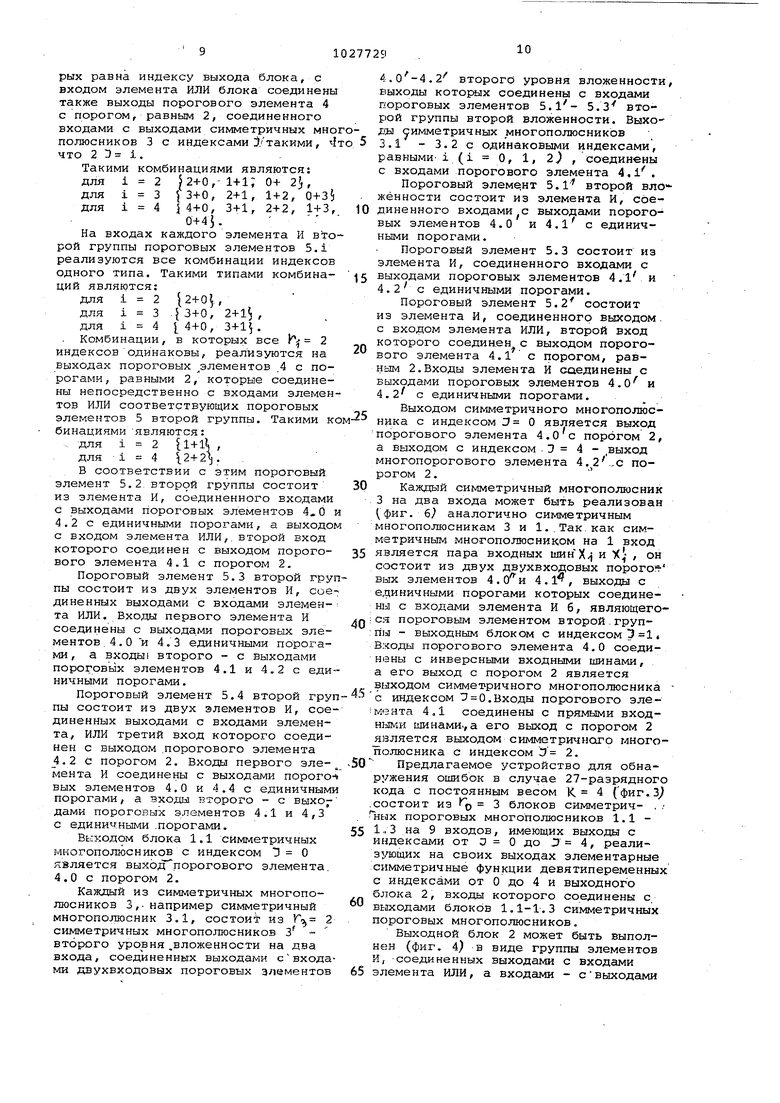

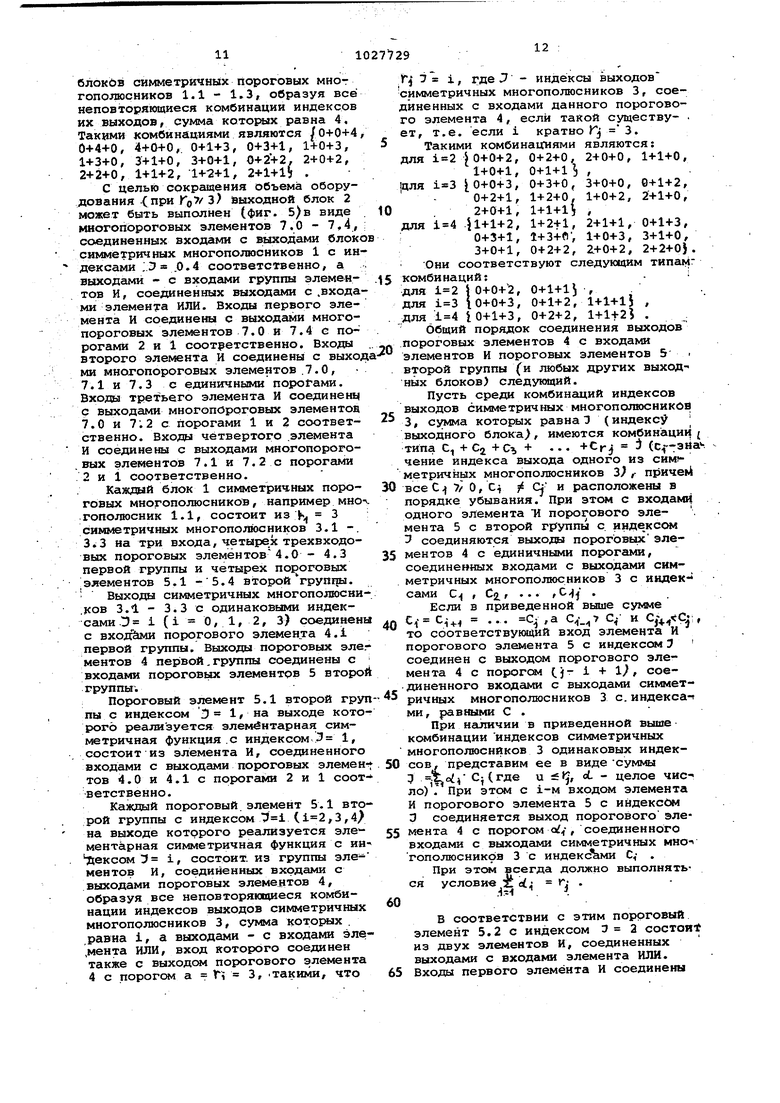

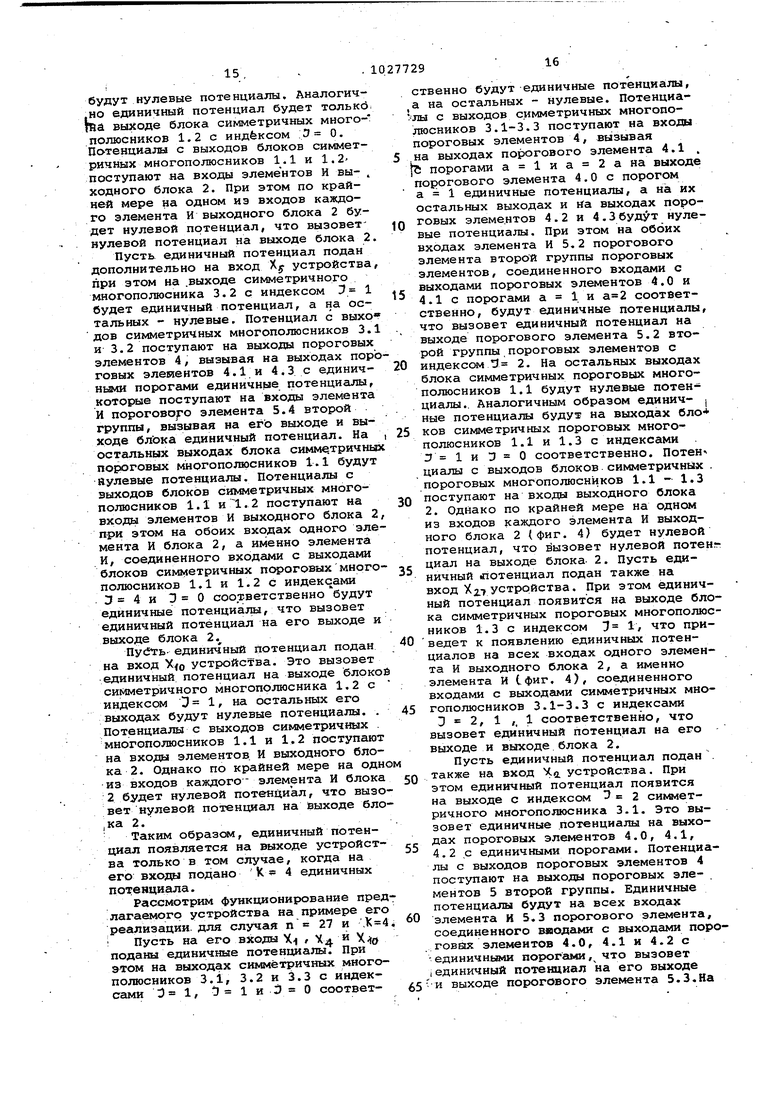

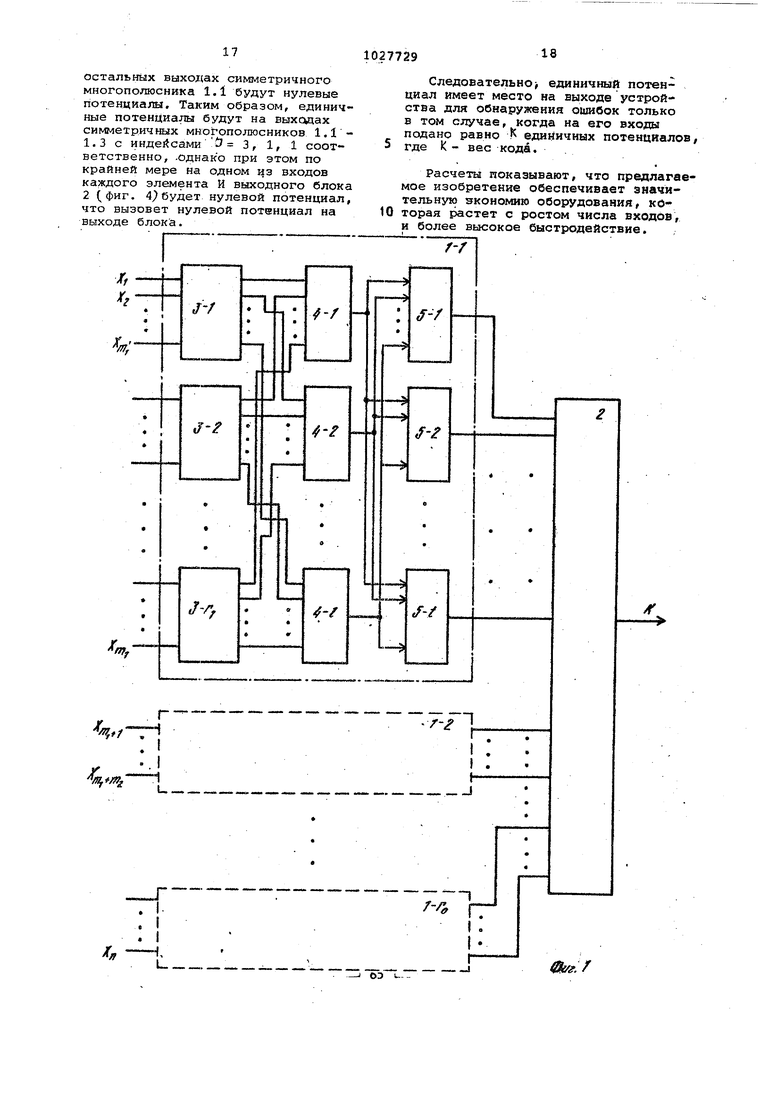

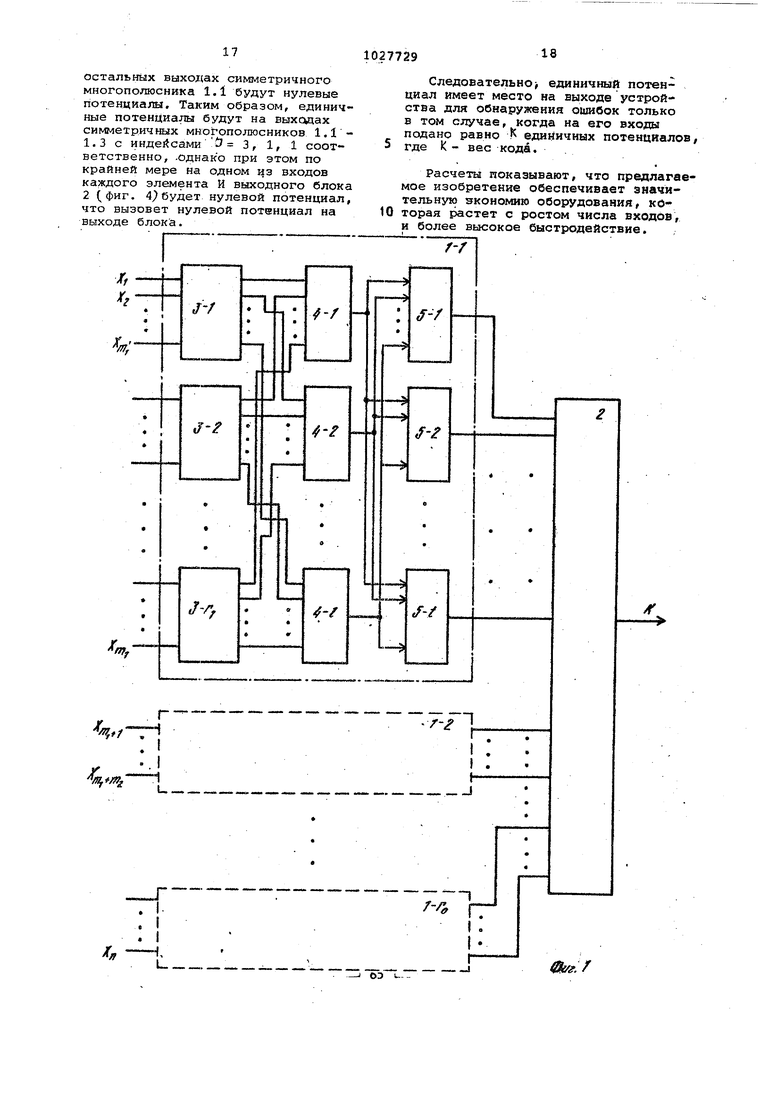

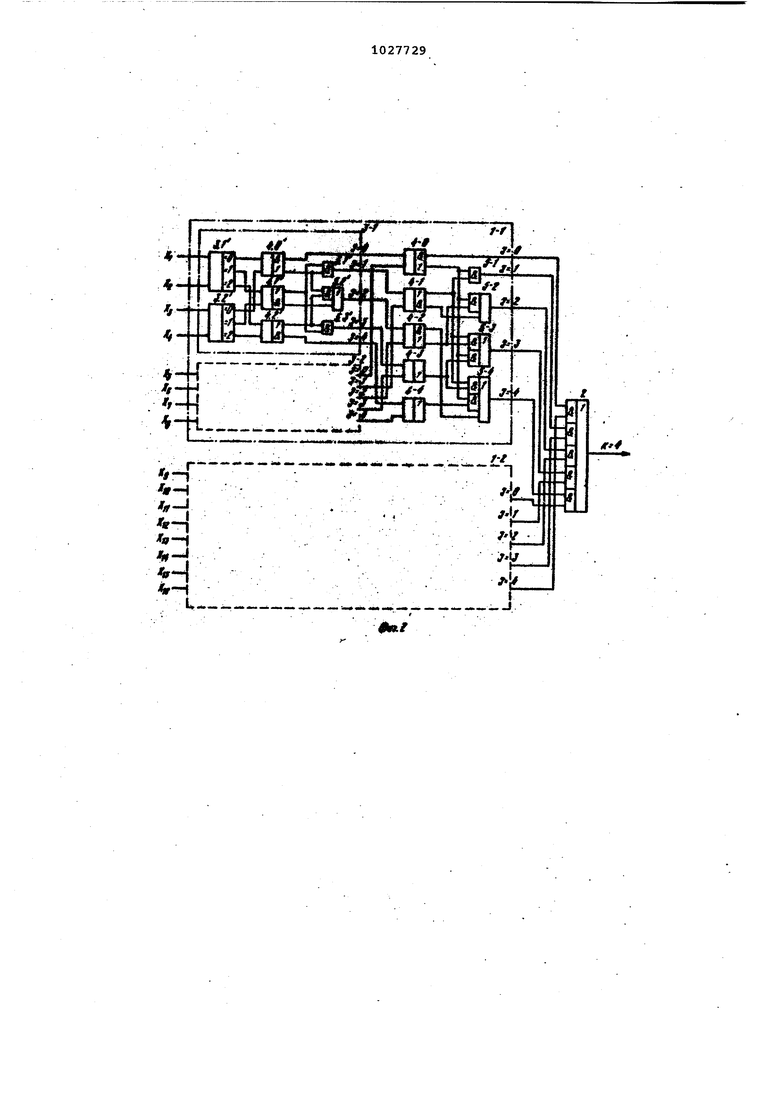

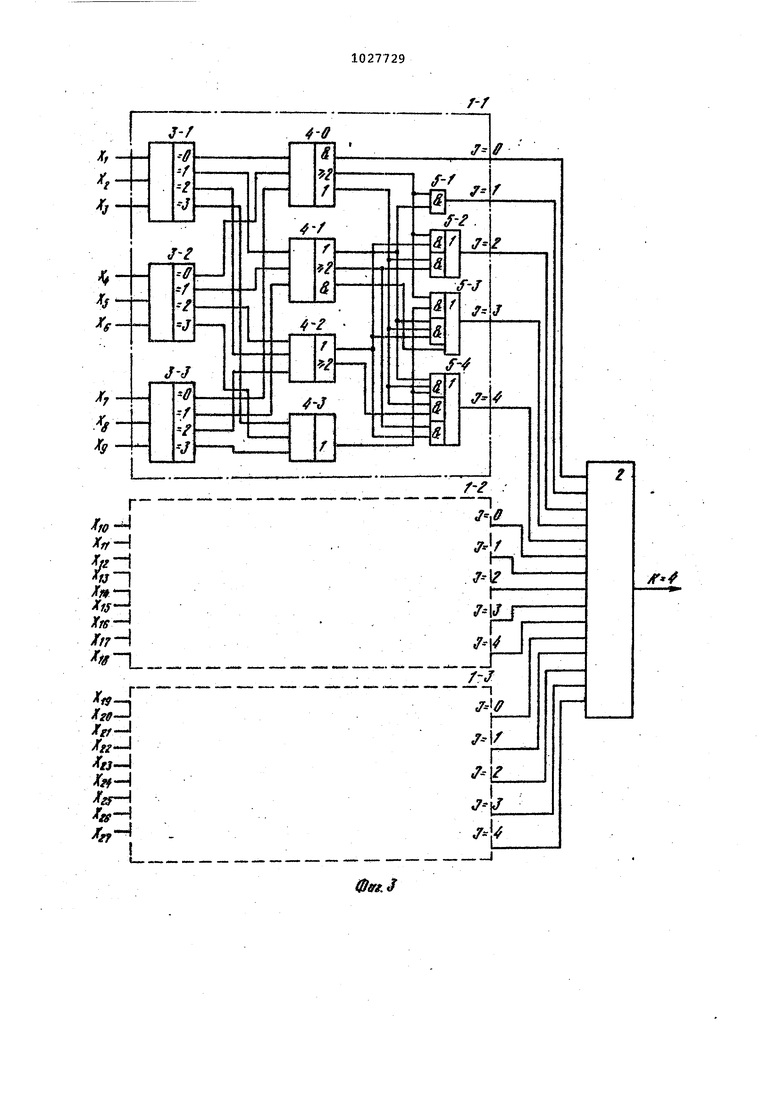

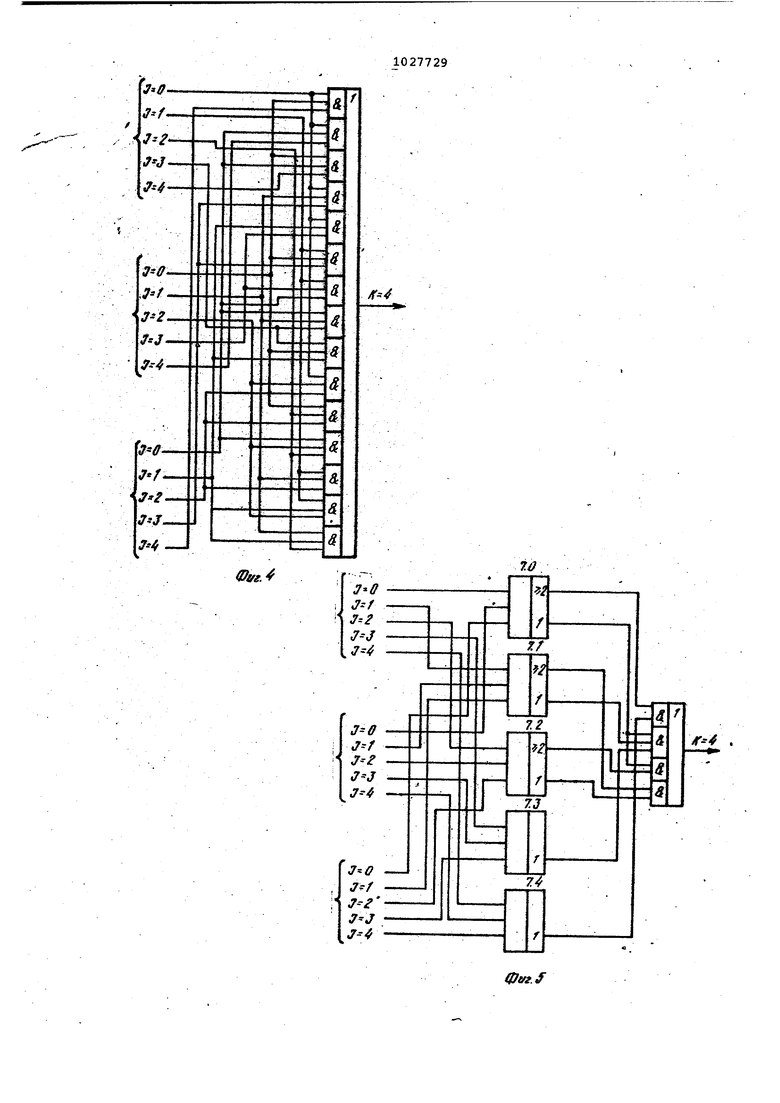

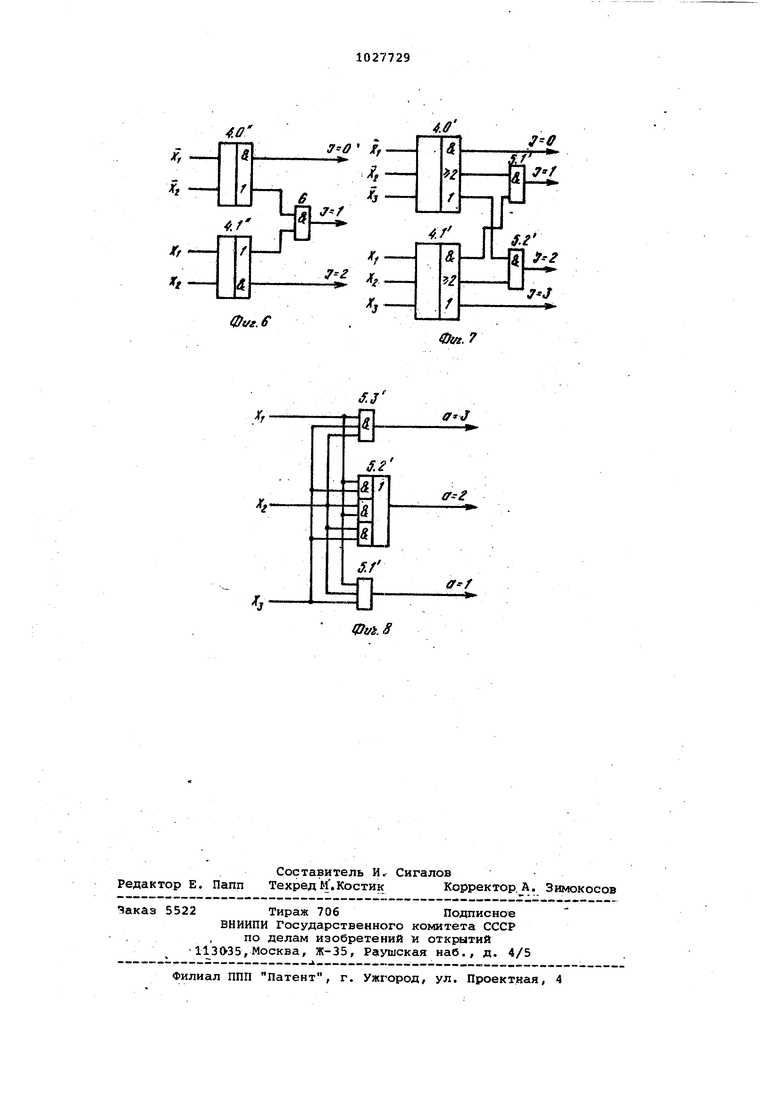

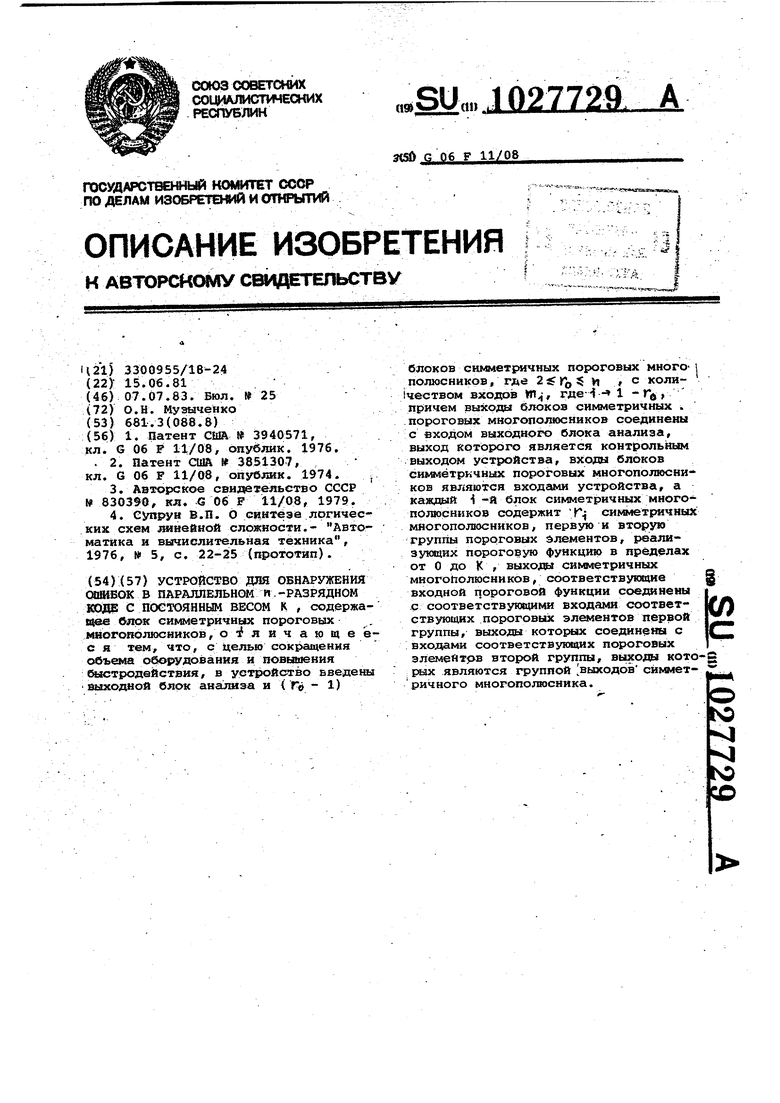

Изобретение относится к автоматике и вычислительной технике и может использоваться для построения различных устройств переработки дискретной информации. Известна схема управления с обнаружением ошибок, содержащая буферные схемы управления, элементы И-НЕ, два компаратора, диоды, резисторы и транзистор jjiiJ. Данная схема позволяет обнаружить наличие К и только К сигналов на входных линиях, однако обладает рядо существенных недостатков. Во-первых, число возможных входов такого устройства практически оказывается ограниченным несколькими единицами, ввиду аналогового принципа работы схемы, так как перепад напряжения -иа входах компараторов, cooTHeTCTByit; щий двум соседним числам сигналов на входных линиях уменьшается по мере увеличения числа линий,-Это не позволяет сущ-ественно увеличивать число линий. Во-вторых, аналоговый принцип не обеспечивает высокой надежности работы схемы, так как по мере увеличения числа входных линий возрастают требования к чувствительности компара торов , что приводит к возрастанию опас ности ложных срабатываний при изменениях напряжения питания и помехах. Известна схема контроля двух и только двух линий из шести, которая содержит первую логическую схему, входы которой соединены соответствен но с двумя из шести линий, вторую логическую схему, входы которой соединены соответственно с выходом первой логической схемы и третьей входной линией, третью логическую схему входы которой соединены соответствен но с выходом второй логической схемы и четвертой входной линией, четвертую логическую схему, входы которой соединены соответственно с выходом .третьей логической схемы и пятой вхо ной линией, и пятую логическую схему, входы которой соединены соответственно с выходом четвертой логической схемы и шестой входной линией. Указанные логические схемы с первой по. пятую содержат устройство, реагирующее на наличие .двух и только двух входных сигналов на шести входных линиях . Данная схема обладает рядом сущес венных недостатков. Во-первых, функциональные возможности ланной схемы ограничены, тай как она позволяет обнаруживать наличие сигналов лишь на двух линиях из шести. Во-вторых, схема имеет большой объем оборудования. В-третьих, длительное время задержки из-за большой глубины схемы (числа последовательно соединенных элементов от входа к выходу). Известно;устройство для обнаружения ошибок в. параллельном п-разрядном коде с постоянным весом К содержащее блок формирования порога, равного К , соединенный выходом с первым входом выходного элемента И, блок формирования порога, равного К. 1, соединенный выходом с входом инвертора, выход которого соединен с вторым входом выходного элемента И, и два преобразователя весов вхот дов, состоящих из параллельно-последовательно-соединенных пороговых узлов и соединенных выходами с входами блоков формирования порога З}. Данное устройство позволяет обнаруживать ошибки в равновесном коде любой разрядности, имеющем вес Л-V Недостатками.данного устройства являются малые функциональные возможности, так каквес кода к. - и большой объем оборудования, составляющий 2К(п - к) + п - 1 элементов И, ИЛИ, НЕ. Наиболее близким по технической сущности к предлагаемому является устройство для обнаружения ошибок в параллельном п-разрядном коде с постоянным весом, содержащее симметричный многополюсник на п -. 1 -вход, реализующий систему элементарных симметричных функций (п - 1)-й переменной, выходы которого соединены с входами элементов И, вторые входы которых соединены с входными шинами Х( и Xjj , а выходы - с входами элемента ИЛИ, каждый симметричный многополюсник на р входов состоит из симметричного многополюсника на р- 1. вход, выходы которых, а .также входг; ные шиныХр и Хр соединены с входами элементов И, выходы которых соединены с входами элементов ИЛИ 4. Известное устройство позволяет обнаруживать ошибки в коде любой разрядности с любым весом К . Однако, он.о обладает рядом существенных недостатков. Во-первых, большим объемом оборудования, так как для его реализации требуется ЗК(п -К)+ п-2 элементов И и ИЛИ. Во-вторых, малым быстродействием, ввиду большой глубины схемы (максимального ч-исла элементов схемы, включенных последовательно от входа к выходу) которая в данном случае составляет 2п. Цель изобретения - сокращение объема оборудования и повышение быстродействия устройства. Поставленная цель достигается тем, что устройство для обнаружения ошибок в параллельном п-разрядном коде с постоянным весом К / содержащее блок симметричных пороговых многополюсников , введены выходной блок анализа и ( 1) блоков симметричных пороговых многополюсников, где ) п, с количеством входов mf, где i- 1 - n. a :t 144 n, причем 1-1 / выходы блоков симметричных пороговых многополюсников соединены с входом выходного блока диализа выход которого является контрольным выходом устройства, входы блокоа симметричных пороговых многополюсниковявляются входами устройства, а каждый 1-й блок симметричных пороговых мноГОПОЛЮСНИКОВ содержит rv симметричны многополюсников, первуюи вторую группы пороговых элементов, реализую щих пороговую функцию в пределах от О до К| выходы симметричных многополюсников , соответствующие входной пороговой функцииу соединены с COOTветствующими входами -соответствуювдх пороговых элементов первой группы, выходы которых соединены с входами соответствующих пороговых элементов второй группы, выходы которых являются группой выходов симметричного многополюсника. Выходной блок анализа может быть ;реалиэован в виде группы элементов И, соединенных выходами .с входами Iэлемента или, а входами - с выходами I симметричных многополюсников на т , Ща. . Го2о входов, образуя все непов торякяциеся комбинации индексов их выходов, сумма которых равна К. Блок симметричных пороговых много пол1юсников на т 1, 1 2,...,рд) входов имеет выходы с индексами от ШОХ Р №ОХ т;} К до On,;i,, 0 при п - т,К и Эрчп К п + mj при п - и реализует на вькодах элементарные симметричные функции т переменных с /индексами отЭ,„-до DrnQit Каждый бло симметричных многополюсников на jlmij 7 1 1 i 1, 2, .. .,Vo) входов соjEsepmHT 7/ 2 симметричных многополюсников на т;, т; , , , дов (mjj + ...+ TRQ. го),имеющих выходы с индексами симметричного многополюсника на mi входов , - - :3J; при т /;7и1пхИ Эмп m J при . ю|оС;Я ДО .W° о и :)«i« 3j;;7 - i - j р« Ч - -);, на выходах которых реализуются элементарные си.мметричные функции с «тон индексами OT JJ : .В пер До.уя ВОЙ группе пороговых элёментов кажды пороговый элемент на Г входов и Г выходов может быть выполнен .в виде - f блоков формирования порога. Влок фор мирования порога, равного г , может быть выполнен в виде элемента. И, сое диненного входами с входами многопорогового элемента, блок формирования порога, равного 1, Может быть вьтол иен в виде элемента ИЛИ, соединенног входами с входгили многопорогового элемента. Каждый блок формирования порога, равного а(2$ 1) может быть выполнен в виде группы элементов И, соединенных выходами с вхо дами элемента ИЛИ, а входами - с входами многопорогового элемента, образуя все их неповторяющиеся комбинации по а входов. -, Вторая группа пороговых элементов ВЕлполнена в вйде,- ряда выходных блоков, причем пороговый элемент, реализующий элементарную симметричную функцию с индексом 3 m - выходной блок с индексом 0 т;: может быть ° индексом - „. ....л.. реализован в виде элемента И, соединенного входами с выходами пороговых элементов первой группы, а также с выходом симметричного многополюсника на mi входов (т . 7 raj,, ... u)- Пусть m-7 m(j7...m j-t-Л- -а / о--- - . Р элемента li соединяются выходом симметричного многополюснис индексом J m/j- a ка на т-входов также с выходами пороговых элементов первой группы с порогами, равными 1 (если имеется несколько пороговых элементов, соединенных входами с выходами одних и тех же симметричных многополюсников, то с входом элемента И соединяется выход с порогом 1 только того порогового элемента первой группы, который соединен входа.ми --С выходами указанных симметрмчных многополюсников, имеющих наибольшие индексы . , Если mj m, ... m.f т то с. входом элемента И соединен вы-. ход порогового элемента первой груп- . пы,соединенного входами с выходами симметричных многополюсников на .1 .,m2. входов с индексами Э П1., со следующим входом элемента И соединен выход порогового элемента с порогом ( Р) -ai )t соединенного входами с выходами симметричных многополюсников на т т... т входов с индексами Э m , а со следующим входом сое-. динен выход порогового элемента, соединенного входами с выходами CHNiMeT-; ричных многополюсников на т т.. . Ий,. входов с индексами У - ,. Т ггпл s :тп.. т выходом симметричного многополюсника на m входов с индексом т является выход порогового элемента первой группы с порогом Т- I соединенноговходами с вьаходами симметр1 чных MHoronojnocHHKOB на m.Iim2... ., входов с индексами, равными m.1| mlj ... m соответственно. Выходом блока симметричного порогового многополюсника на т входов с индексом3 ,О является выход порогового элемента первой группы с порогом 1C,, соединенного входами с выходами- cи пvIeтpичныx многополюсников иа га,, mjj. m входов с индекса1ми 31 ОГ Выходной блок с индексом Э 1, реализующий элементарную симметричг ную функцию-с индексом :Э 1, может быть выполнен в виде элемента И, соединенного одним входом с выходом порогового элемента первой группы с порогом ryj - 1 г соединенного входами с выходами симметричных многополюсников на m/f mg ... m -входов с индексами, равными О, а другим входом - с выходом порогового элемента первой группы с порогом 1, соеди ненного входами с выходами симмет ричных многополюсников на т m ... m . входов с индексами, равными 1 . , Каиоднй выходной блок с индексом {i 3- ,)может быть выполнен в виде группы элементов И, соединенных выходами с входами элемента ИЛИ а входами - с выходами пороговых элементов первой группы, и,кро.ме того, с выходами симметричного многополюсника на mj nijj m 2. nijm,j ... mj. входов с индексами, не превьпаающими Э и не соединенными с входами пороговых элементов первой группы, если такой имеется, образуя на входах элементов И все неповторя щиеся комбинации индексов выходов симметричныхмногополюсниковна ,m,m ... m входов, сумма которых равна 3 . Кроме того, с входами элемен та ИЛИ соединен выход порогов -элемента первой группы на входов с порогом , входы которого соединены с выходами симметричных многополюсников на т т ... т входов с. индексами 17 такими, что J J , если такие имеются. ч Общий порядок соединения входов элементов И с выходами пороговых г элементов первой группы следующий. Пусть- среди комбинаций индексов выходов симметричных многополюсников на ш m5 ... m,. входов , сумма ко торых равна D- индексу данного выходного блока, имеются комбинации т па Си + С + ... + CY 3 , где C,j значение индекса выхода одного из симметричных многополкэсников. Пред ИМ данную сумму в виде J , ставим 1:5 Us П С 5, о( V - Це где число, причем. Г;. При этом с первым входом элемента И соединяется выход порогового элемента первой группы с порогом o//t / соединенного входами с выходами симметричных мно гополюсников на т mg ... m| входов с индексами , с вторым входом элемента И соединяется выход порогового элемента первой группы и порогом с1/2, соединенного входами с выходами симметричных многополюсников на mj,... т ,л,. входов с индексами Т) С, и т.д. , с последни входом элемента И соединен выход порогового элемента первой группы с порогом 5tt| , соединенного входами с выходами симметричных многополюсн ков на т{ т ... т , входов с индек сами Сц . В частном случае один из индексовс в указанной сумме больший всех остальных, является ий дексом-выхода симметричного много S т ... ту mj, . полюс ник а на т; mt входов и удовлетворяет усло ВИЮ Су mjj, .,т-. тп.. тп.) l+f, соответствует выходу симметричного многополюсника, на входов, не cde- . диненному с входом порогового элемента первой группы, при этом он соединяется непосредственно с входом элемента И выходного блока. Если щ ... т}-. ., то выходной блок, реализующий эл ментарную симметричную функцию с индексом D т - 1, реализуется в виде элемента И, первый вход которого соединен с выходом порогового элемента первой группы с порогом 1, соединенного входами с выходами симметричных многополюсников, на т т,... т. входов с индексами, равными числу их входов, а второй вход с.выходами порогового элемента первой группы с порогом 1, соединенного входами с -выходами симметрич ных многополюсников на т т ... mi. входов с индексами э .- 1. Каждый из симметричных многополюсников на т; входов () 1,2,„, все другие могут быть реализованы , аналогично блокамсимметричных nopot говых многополюсников на т (, 2 , ...j)) входов, т.е. состоящими из других симметричных многополюсников, соединенных выходами с входами пороговых элементов, первый и второй групп. Симметричным многополюсником на п 1 Вход, имеющим выходы с индексами t) О и D 1, является, пара -вхрдных шин Х{и )(i , если они обе доступны, в противном случае он состоит из входной шины инвертора, соединенного входом с шиной Х На фиг. 1 изображена структурная схема предлагаемого устройства для обнаружения ошибок в параллельном п-раэряднсм коде с постоянным весом К; на фиг. 2 - схема предлагаемого устройств.а для случая при Гц Tj 2 const; на фиг. 3 схема предлагаемого устройства для случая п 27 и К 4 при (о - J 3 const; на фиг. 4 и 5 - схема реализации выходного блока анализа устройства для случая п 27, К 4 при KO 3 const; на фиг. б схема симметричного многополюсника на 2 входа и 3 выхода; на фиг. 7 схема симметричного многополюсника на 3 входа и 4 выхода; на , 8 схема порогового элемента на 3 входа, и 3 выхода. Предлагаемое устройство для обнаруг жения ошибок в параллельном п-раэрядном коде с постоянным весом К состоит (фиг. 1) иэ блоков 1.1 - 1.KJ) симметричных многополюсников, соеди- ненных выходами с входами выходного блока 2. Каждый блок симметричных многополюсников l.i (1 - 1, 2, ...J реализует на выходах систему элементарных симметр ных функций т- переменных с индексами при m.fVK ,ох т,- при ДО Jtnir О при п - т 7 (С- и К - п + т при п - . Он состоит из К} симметричных многополюсников 3.1 - 3. К , пороговых элементов 4.1 - 4.1 первой группы и порого вых элементов второй группы 5.1 5.t. Выходы симметричных многополюс ников 3.1 - 3.1 на mjj mg ... входов, имеющие одинаковые индексы, соединены с входами пороговых элементов 4.1-4.1, .соединенных выходами с входами пороговых элементов 5.1 5.t второй группы. Остальные выходил симметричных многополюсников (выходы симметричного многополюсника 3 на fflj 7 , mjj.... ... ту входов с индексами , большими ин ексов выходов других симметричных многополюсн1яков,не соединенные с вхо дами пороговых элементов 4 первой :группы,соединены с входами пороговых элементов 5 второй группы с индекса|ми(« : m -mj+У . Выходы порого вых элементов 4.1 - 4.1 соединены с входами пороговых элементов 5.1 5.t второй группы.. Каждый симметричный многополюсни 3 и любой другой может быть реализо ван аналогично блоком- симметричных многополюсников 1., Каждый пороговый элемент. 4 и любой другой, например, пороговый эле мент на ( входов, может быть реализован на элементах И и ИЛИ, объединенных в блоки формирования порога. Блок формирования порога, равного 1 может быть выполнен в виде элемента ИЛИ, соединенного входами с входами RiHoronoporoBoro элемента. Блок форм рования .порога, равного 1 , может быть выполнен в виде элемента И, соединенного входами с выходами .порогового элемента. Каждый блок фо мирования порога, равного а ( 2$ |Г- 1) может быть выполнен в виде группы элементов И, соединенных вых дами с входами элемента ИЛИ, а входами - с входами многопорогового , образуя все их неповторяю щиеся комбинации по а входов. Пороговый элемент на два входа (фиг. 2) может быть реализован в виде элемента И и, элемента ИЛИ с парал лельно соединенными входами. Пороговый элемент на 3 входа и 3 выхода (фиг. 8) может быть реализо ван в виде трех блоков 8 формирования порога. Блок 8.1 формирования порога, равного 1, состоит из элемента ИЛИ, соединенного выходами с входными шинами. Блок 8.2 формирова ния порога, равного 2, состоит из трех элементов. И,соединенных входами с входами порогового элемента,образуя все их неповторяющиеся комбинации по два входа, а выходами - с входами элемента ИЛИ. Блок 8.3 формирования порога, равного 3,. состоит из элемента И, соединенного входами с входами многопорогового элемента. С целью сокращения объема оборудования пороговый элемент при К: 3 может быть синтезирован методом раз ложения по переменным. Более подробно рассмотрим предлагаемое устройство для обнаружения ошибок в параллельном п-раэрядном коде с постоянным весом К. для случай п 16, К 4 при VJ, Г. г const4 и для случая п 27, К 4 при 1 Г: 3 const. Устройство для обнаружения ошибой в параллельном шестнадцатиразрядном коде с постоянным весом К, 4 (фиг.2 содержит У 2 блока 1.1 и 1.2 симметричных пороговых многополюсника ; на 8 входов и выходной блок 2. Блоки -1.1 и 1.2 симметричных многополюсников имеют выходы с индексами от f 4 , О, соединенные с входами выxoJ5нoгo блока 2. Выходной блок 2 состоит из группы элементов И, соединенных выходаг ш с входами элемента ИЛИ. На входах: элементов И образуются все неповторяющиеся комбинации индексов выходов симметричных многополюсников 1, сумма которых равна К 4. Такими ком бинациями являются 54+0, 3+1; 2. + 2, 1, + 3, О + 4). Каждый блок 1 симметричных поро-. говых многополюсников, например блок 1.1 симметричных пороговых многополюсников состоит из Г 2 симметричных многополюсников 3.1 и 3.2 двухвходовых пороговых элементов 4.0 4.4 первой группы и пороговых элементов 5. 5.4 второй групп. Выходы симметричных многополюсников 3 с индексами i(i О, 1, 2, 3, 4) соединены с входами порогового элемента 4.1. Выходы пороговых элементов 4.0 - 4.4 соединены с входами пороговых элементов 5.1 - 5.4 второй группы с индексами от 1 до. 4 соответ ственно. Пороговый блок 5.1 с индексом 3 1, на выходе которого реализует- ся элементарная симметричная фнукция с индексе 1, состоит из элемента И, соединенного входами с выходами по-; роговых элементов 4.0 и 4.1 с порогами, равными 1. Каждый из пороговых блоков 5.1 (i 2, 3, 4) состоит из группы элементов И, соединенных выходами с входами элемента ИЛИ, а входами - с выходами пороговых элементов 4, образуя на входах все неповторяющиеся комбинации индексов выходов симмет-, ричных многополюсников 3, сумма которых равна индексу выхода блока, с входом элемента ИЛИ блока соединены также выходы порогового элемента 4 с порогом, равным 2, соединенного входами с выходами симметричных многпогаосников 3 с индексами такими, что 2 :) i.

Такими комбинациями являются:

для 1 2 52+0,-i+i; 0+ 25,

для 1 3 3+0, 2+1, 1 + 2, 0+3

для 14+0, 3+1, 2+2, 1+3, 0+4.

На входах каждого элемента И второй группы пороговых элементов 5.1 реализуются все комбинации индексов одного типа. Такими типами комбинаций являвдтся:

для 1 2 2+0.,

для 1 3.} 3+0, 2+1 ,

для 1 4 4+0, 3+15 .

Комбинации, в которых все К 2 индексов одинаковы, реализуются на выходах пороговых элементов .4 с порогами, равными 2, которые соединены непосредственно с входами элементов ИЛИ соответствующих пороговых элементов 5 второй группы. Такими кобинациями являются: . для 1 2 U+l ,

для 1 4 i2+2tj.

В соответствии с этим пороговый элемент 5.2. второй группы состоит из элемента И, соединенного входами с выходами пороговых элементов 4.О и 4.2 с единичными порогами, а выходом с входом элемента ИЛИ,, второй вход которого соединен с выходом порогового элемента 4.1 с порогом 2.

Пороговый элемент 5.3 второй группы состоит из двух элементов И, соединенных выходами с входами элемен-: та ИЛИ, Входы первого элемента И соединены с выхода.ми пороговых элементов 4.0 и 4.3 единичными порогами, а входыI второго - с выходами пороговых элементов 4.1 и 4.2 с единичными порогами.

Пороговый элемент 5.4 второй группы состоит из двух элементов И, соединенных выходами с входами элемента, ИЛИ третий вход которого соединен с выходом .порогового элемента 4.2 с порогом 2. Входы первого элемента И соединетл с выходами порого- вых элементов 4.0 и 4.4 с единичными порогами, а входы второго - с выходами пороговых элементов 4.1 и 4,3 с единичными .порогами.

Выходом блока 1.1 симметричных мкогополюсников с индексом f О является выход порогового элемента. 4,0с порогом 2,

Каждый из симметричных многополюсников 3,- например симметричный многополюсник 3.1, состоит из Гэ 2 симметричных многополюсников З второго уровня .вложенности на два входа, соединенных выходами свходами двухвходовах пороговых элементов

4.о-4.2 второго уровня вложенности выходы которых соединены с входами пороговых элементов 5.1- 5.3 второй группы второй вложенности, Выхо ды симметричных многополюсников 3.1 - 3.2 с одинаковыми индексами, равными- 1(1 О, 1, 2) , соединены с входами порогового элемента 4,1.

Пороговый элемент 5.1 второй вло жённости состоит из элемента И, соединенного входами с выходами пороговых элементов 4.0 и 4.1 с единичными порогами.

Пороговый элемент 5.3 состоит из элемента И, соединенного входами с выходами пороговых элементов 4,1 и 4.2 с единичными порогами.

Пороговый элемент 5,2 состоит из элемента И, соединенного выходом, с входом элемента ИЛИ, второй вход которого соединен с выходом порогового элемента 4,1 с порогом, равным 2.Входы элемента И соединены с выходами пороговых элементов 4.0 и 4.2 с единичными порогами.

Выходом симметричного многополюсника с индексом Л О является выход порогового элемента 4,Ос порогом 2, а выходом с индексом 4 выход многопорогового элемента 4.2.,с порогом 2.

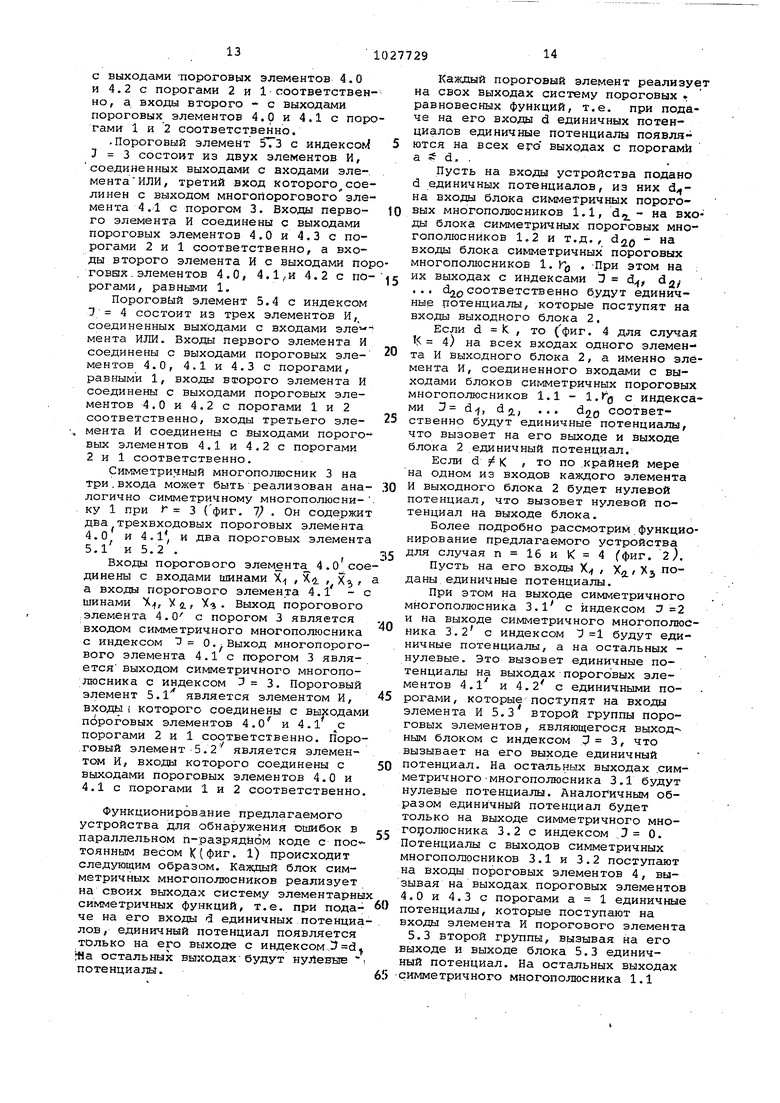

Каждый симметричный многополюсник 3 на два входа может быть реализован (фиг. 6) аналогично симметричным многополюсникам 3 и 1..Так.как симметричным многополюсником на 1 вход является пара входных шинХ и , он состоит из двух двухвходовых порого вых элементов 4. 4.1, выходы с единичными порогами которых соединены с входами элемента И 6, являющего;ся пороговым элементом второй.груп:пы - выходным блоком с индексом , Входы порогового элемента 4.0 соединены с инверсными входными шинами, . а его выход с порогом 2 является выходом симметричного многополюсника с индексом О,Входы порогового эле мента 4,1 соединены с прямыми входшлми шинами., а его выход с порогом 2 является выходом симметричного многоТтолюсника с индексом i7 2.

Предлагаемое устройство для обнаружения ошибок в случае 27-разрядног кода с постоянным весом К 4 {фиг,3 .состоит из о 3 блоков симметрич- . ных пороговых многополюсников 1,1 1„3 на 9 входов, имеющих выходы с индексами от о О до 11 4, реализующих на своих выходах элементарные симметричные функции девятипеременны с индексами от О до 4 и выходного блока 2, входы которого соединены с, выходами блокбв 1,1-1.3 симметричных пороговых многополюсников.

Выходной блок 2 может быть выполнен (фиг, 4) -в виде группы элементов И, соединенных выходами с входами элемента ИЛИ, а входами - свыходами блокбв симметричных пороговых мнот гополюснкков 1,1 - 1.3, образуя всё неповторяющиеся комбинации индексов их выходов, сумма котоЕ%1Х равна 4, Такими комбинациями являются /0+0+4 0+4+0, 4+0+0, 0+1+3, 0+3+1, 1+0+3, 1+3+0, 3+1+0, 3+0+1, 0+2+2. 2+0+2, 2+2+0, 1+1+2, 1+2+1, 2+1+1V . С целью сокращения объедла оборудования (при toi З) выходной блок 2 может быть выполнен (фиг. 5)в виде многопороговых элементов 7.0 - 7,4, соединенных входгши с выходами блоко симметричных многополюсников 1 с ин дексами Э .0.4 соответственно, а выходами - с входами группы элементов И, соединенных выходами с .входа ми-элемента ИЛИ. Входы первого элемента И соединены с выходами многопороговых элементов 7.0 и 7.4 с порогами 2 и 1 соответственно. Входы второго элемента И соединены с выход ми многопороговых элементов .7.0, 7.1 и 7.3 с единичными порогами. Входы третьего элемента И соединень) с выходами многопороговых элементов 7.0 и 7;2 с порогами 1 и 2 соответственно. Входы четвертого .элемента И соединены с выходами многопорого.вых элементов 7.1 и 7.2с порогами .2 и i соответственно. Каждый блок 1 симметричных пороговых многополюсников, например многополюсник 1.1, состоит из 3 симметричных многополюсников 3.1 -. на три входа, четырех трехвходовых пороговых элементов4.0 - 4.3 первой группы и четырех пороговых элементов 5.1 -5.4 второйгруппы. Выходы симметричных многополвосни .ков 3.1 - 3.3 с одинаковыми индексг№Ш t) 1 (i О, 1, 2, 3) соединены с входйми порогового элемента 4.1 первой группы. Выходы пороговых эле ментов 4 первой.группы соединены с входами пороговых элементов 5 второй группы. Пороговый элемент 5.1 второй груп пы с индексом 3 1, на выходе которого реализуется элементарная симметричная функция .с индексом/3 1, состоитИЗ элемента И, соединенного входами с выходами пороговых элемен тов 4.0 и 4.1 с порогами 2 и 1 соответственно. Каясдый пороговый, элемент 5.1 второй группы с индексом С ,3,4 на выходе которого реализуется эле- ментарная симметричная функция с ин Дексом i, состоит, из группы элементов и, соединенных входами с выходами пороговых элементов 4, образуя все неповторяющиеся комбинации индексов выходов симметричных многополюсников 3, сумма которых . ,равна i, а выходами - с входами эле,мента ИЛИ, вход которого соединен также с выходем порогового элемента 4 с порогом а ti 3, .такшш, что Ti i, где J - индексы выходов -симметричных многополюсников 3, соединенных с входами данного порогового элемента 4, если такой существу- . ет, т.е. если i кратно Kj 3. Такими комбинахшями являются: для I0+0+2, 0+2+0, 2+0+0, 1+1+0, 1+0+1, 0+1+1 , цля 0+0+3, 0+3+0, 3+0+0, е+1+2, 0+2+1, 1+2+0, 1+0+2, 2+1+0, 2+0+1, 1+1+1 , для .U+1+2, 1+2+1, 2+1+1, 0+1+3, ; 0+3+1, i+3+fi, 1+0+3, 3+1+0, 3+0+1, 0+2+2, г+0+2, 2+2+OJ. Они соответствуют следующим типам комбинаций:- для iO+0+2, O+1+li , для i0+0+3, 0+1+2, 1+1+1S , для i0+1+3, 0+2+2, l+l+2i . Общий порядок соединения выходов .пороговых элементов 4 с входами элементов И пороговых элементов 5 второй группы (и любых других выходных блоков) следующий. Пусть среди комбинаций индексов выходов симметричных многополюсников 3, сумма которых равна 1 (индексу выходного блока, имеются комбинаци1 | j типа С., +С2 +С, + ... -Crj i (с -зйач чение индекса выхода одного из сим;метричных многополюсников 3 f приче всеС 7/ О, С4 j Cj- и расположены в порядке убывания. При этом с входами одного элемента И порогового элемента 5 с второй группы с индексе соединяются выхо№з порюговЕлх элементов 4 с единичными порогами, соединенных входами с выходами симметричных многополюсников 3 с индексами С , Cg., ... , . Если в приведенной выше сумме С С ... С| ,а С,, и Cj-4.C:;, то соответствующий вход элемента И порогового элемента 5 с индексом 3 соединен с выходом порогового элемента 4 с порогом (.J- i + i), соединенного входакш с выходами симметричных многополюсников 3 с. индексам ми, равными С . При нгшичии в приведенной выше комбинации индексов симметричных многополюсников 3 одинаковых индексов, представим ее в виде суммы 5 U ifj, i. - целое число) . При этом с i-M входом элемента И порогового элемента 5 с индексйм D соединяется выход порогового элемента 4 с порогом , соединенного входами с выходс1ми симметричных мно- гополюсников 3 с индекс ми С,- . При этом всегда должно выполняться условие d i В соответствии с этим пороговый. элемент 5.2 с индексом J 2 состоя из двух элементов И, соединенных выходами с входами элемента ИЛИ. Входы первого элемента И соединены с выходами -пороговых элементов 4.О и 4,2 с порогами 2 и 1 соответственно, а входы второго - с выходами пороговых элементов 4.0 и 4.1 с поро гами- 1 и 2 соответственно. .Пороговый элемент 5.3 с индексог состоит из двух элементов И, соединенных выходами с входами элементаИЛИ, третий вход которого,соелинен с выходом многопорогового элемента 4.1 с порогом 3. Входы первого элемента И соединены с выходами пороговых элементов 4.0 и 4.3 с порогами 2 и 1 соответственно, а входы второго элемента И с выходами пор гових.элементов 4.0, 4.1,и 4.2 с порогами, равными 1. Пороговой элемент 5.4 с индексом Т 4 состоит из трех элементов И, соединенных выходами с входами эле-- мента ИЛИ. Входы первого элемента И соединены с выходами пороговых элементов 4.0, 4.1 и 4.3 с порогами, равными 1, входы вссорого элемента И соединены с выходами пороговых элементов 4.0 и 4.2 с порогами 1 и 2 соответственно, входы третьего элемента И соединены с выходами пороговых элементов 4.1 и 4.2 с порогами 2 и 1 соответственно. Симметричный многополюсник 3 на три.входа может быть реализован аналогично симметричному многополюснику 1 при 3 (фиг. 7 . Он содержит два трехвходовых пороговых элемента 4.0и 4.1 и два пороговых элемента S.l и 5.2 . Входа порогового элемента 4 . динены с входами шинами Х , Х , Х, f а входы порогового элемента 4.1 - с шинами Ч, X 2., Xi . Выход порогового :Элемента 4.0 с порогом 3 является входом симметричного многополюсника с индексом 3 0. Выход многопорогового элемента 4.1 с порогом 3 является выходом симметричного многополюсника с индексом 3 п 3. Пороговый элемент 5.1 является элементом И, входы I которого соединены с выходами пороговых элементов 4.0 и 4.1 с порогами 2 и 1 соответственно. Поро.говый элемент-5.2 является элементом И, входы которого соединены с выходами пороговых элементов 4.0 и 4.1с порогами 1 и 2 соответственно Функционирование предлагаемого устройства для обнаружения ошибок в параллельном п-разрядйом коде с пос тоянным весом К(фиг. 1) происходит следующим образом. Каждый блок симметричных многополюсников реализует на своих выходах систему элементарны симметричных функций, т.е. при подаче на его входы d единичных потенциа лов, единичный потенциал появляется только на его выходе с индексомЛ d остальных выходах-будут нулевые потенциалы. Каждый пороговый элемент реализует на свох выходах систему пороговых равновесных функций, т.е. при подаче на его входы d единичных потенциалов единичные потенциалы появляются на всех его выходах с порогами а г d. .. Пусть на входы устройства подано d единичных потенциалов, из них d,на входы блока симметричных пороговых многополюсников 1.1, d,. - на входы блока симметричных пороговых многополюсников 1.2 и т.д., - на входы блока симметричных пороговых многополюсников 1. TO . -При этом на , их выходах с индексами 13 d, dgy ... d ; j5соответственно будут единичные потенциалы, которые поступят на входы выходного блока 2. Если d К , то (fфиг. 4 для случая S 4) на всех входах одного элемента И выходного блока 2, а именно элемента И, соединенного входами с выходами блоков симметричных пороговых многополюсников 1.1 - 1.(б с индексами й- в., d5L, ... djo соответственно будут единичные потенциалы, что вызовет на его выходе и выходе блока 2 единичный потенциал. Если d К , то по .крайней мере на одном из входов каждого элемента И выходного блока 2 будет нулевой потенциал, что вызовет нулевой потенциал на выходе блока. Более подробно рассмотрим функционирование предлагаемого устройства для случая (фиг. 2), Пусть на его входы Х , Х. Хэ п° даны единичные потенциалы. При этом на выходе симметричного многополюсника 3.1 с индексом У 2 и на выходе симметричного многополюсника 3.2 с индексом :3 1 будут единичные потенциалы, а на остальных нулевые. Это вызовет единичные потенциалы на выходах пороговых элементов 4.1 и 4.2 с единичными порогами, которые поступят на входы элемента И 5.3 второй группы пороговых элементов, являющегося выход ным блоком с индексом , что вызывает на его выходе единичный потенциал. На остальных выходах симметричного -многополюсника 3.1 будут нулевые потенциалы. Аналогичным образом единичный потенциал будет только на выходе симметричного много олюсника 3.2 с индексом 0. Потенциалы с выходов симметричных многополюсников 3.1 и 3.2 поступают на входы пороговых элементов 4, вызывая на выходах пороговых элементов 4.0 и 4.3 с порогами а 1 единичные потенциалы, которые поступают на входы элемента И порогового элемента 5.3 второй группы, вызывая на его выходе и выходе блока 5.3 единичный потенциал. На остальных выходах симметричного многополюсника 1.1 будут нулевые потенциалы, Аналогич.но единичньай потенциал будет толькй ша выходе блока симметричных многополюсников 1,2 с индексом .3 О, Потенциалы с выходов блоков симметричных многополюсников 1.1 и 1.2 поступают на входы элементов И вы- , ходного блока 2, При этом по крайней мере на одном из входов каждого элемента И выходного блока 2 будет нулевой потенциал, что вызовет нулевой потенциал на выходе блока 2 Пусть единичный потенциал подан дополнительно на вход Ху устройства при этом на .выходе симметричного многополюсника 3.2 с индексом ; 1 будет единичный потенциал, а на остальных - нулевые. Потенциал с выхо дов симметричных многополюсников 3. и 3.2 поступают на выходы пороговых элементов 4, вызывая на выходах пор говых злеяентов 4,1 и 4,3 с единичными порогами единичные потенциалы, которые поступают на входы элемента И порогового элемента 5.4 второй группы, вызывая на его выходе и выходе блЬка единичный потенциал. На остальных выходах блока симметричны пороговых многополюсников 1,1 будут йулевые пoтeнциaJaI, Потенциалы с выходов блоков симметричных многополюсников 1,1 и 1, 2 поступают на входы элементов И выходного блока 2 при этом на обоих входах одного эле мента И блока 2, а именно элемента И, соединенного входами с выходами блоков симметричных пороговыхмного полюсников 1,1 и 1,2 с индексами 3 4 и Э О соответственно будут единичные потенциалы, что вызовет единичный потенциал на его выходе и выходе блока 2. Пу(гь- единичный потенциал подан на вход Xfo устройства. Это вызовет единичный потенциал на выходе блоко сигфлетричного многополюсника 1,2 с индексом 3 1, на остальных его выходах будут нулевые потенциалы, . Потенциалы с выходов симметричных . многополюсников 1,1 и 1.2 поступают на входы элементов. И выходного блока 2. Однако по крайней мере на одн из входов каждого элемента И блока 2 будет нулевой потенциал, что вызо вет нулевой потенциал на :выходе бло ,ка 2, : Таким образом, единичный потенциал появляется на выходе устройства только в том случае, когда на его входы подано К 4 единичных потенциала. Рассмотрим функционирование пред лагаемого устройства на примере его реализации, для случая п 27 и , Пусть на его входы Xi , Хл « поданы единичные потенциалы. При этом на выходах симметричных многополюсников 3,1, 3,2 и 3,3 с индексами , 1и1)0 соответственно будут -единичные потенциалы, а на остальных - нулевые, Потенциалы с выходов симметричных многополюсников 3,1-3,3 поступают на входы пороговых элементов 4, вызывая на выходах порогового элемента 4,1 . C порогами выходе порогового элемента 4,0 с порогом а 1 единичные потенциалы, а на их остальных выходах и На выходах пороговых элементов 4,2 и 4,3будут нулевые потенциалы. При этом на обоих входах элемента И 5.2 порогового элемента второй группы пороговых элементов, соединенного входсши с выходами пороговых элементов 4,0 и 4.1с порюгами а 1 и соответственно, будут единичные потенциалы, что вызовет единичный потенциал на выходе порогового элемента 5,2 второй группы , пороговых элементов с индексом tJ 2. На остальных выходах блока симметричных пороговых многополюсников 1,1 будут нулевые потенциалы. Аналогичным образом единичные потенциалы будут на выходах бло ков симметричных пороговых многополюсников 1,1 и 1,3 с индексами Л 1 и D О соответственно. Потен циалы с выходов блоков симметричных . пороговых многополюсников 1,1 - 1.3 поступсшзт на входы выходного блока 2. Однако по крайней мере на одном из входов каждого элемента И выходного блока 2 (фиг. 4) будет нулевой потенциал, что вызовет нулевой потенциал на выходе блока. 2, Пусть единичный потенциал подан также на вход Х2.7 устройства. При этом единичный потенциал появится на выходе блока симметричных пороговых многополюсников 1,3 с индексом 1, что приведет к появлению единичных потенциалов на всех входах одного элемента И выходного блока 2, а именно элемента И Сфиг, 4), соединенного входами с выходами симметричных многополюсников 3,1-3,3 с индексами Э 2, 1 ,, 1 соответственно, что вызовет единичный потенциал на его выходе и выходе.блока 2, Пусть единичный потенциал подан . также на вход 4(2. устройства. При этом единичный потенциал появится на выходе с индексом 2 сиьметричного многополюсника 3.1, Это вызовет единичные потенциалы на выходах пороговых элементов 4.0, 4.1, 4.2с единичными порогами. Потенциалы с выходов пороговых элементов 4 поступают на выходы пороговых элементов 5 второй группы. Единичные потенциалы будут на всех входах элемента И 5.3 порогового элемента, соединенного вяодами с выходами пороговах элементов 4.0, 4.1 и 4.2с единичньвли порогами, что вызовет единичный потенциал на его выходе н выходе порогового элемента 5.3.На

остальных выходах симметричного многополюсника 1.1 будут нулевые потенциалы. Таким образом, единичные потенциалы будут на выхсадах симметричных многополюсников 1.11.3 с индейсами 5 3, 1, 1 соответственно, .однако при этом по крайней мере на одном цз входов каждого элемента И выходного блока 2 (фиг. 4 будет нулевой потенциал, что вызовет нулевой потшнциал на выходе блока.

Следовательно единичный потенциал имеет место на выходе устройства для обнаружения ошибок только в том случае, когда на его входы подано равно 1 единичных потенциалов/ где К - вес кода.

Расчеты показывают, что предлагаемое изобретение обеспечивает значительную экономию оборудования, которая растет с ростом числа входов, и более высокое быстродействие.

Ф&г.З

фаг./

.O

//

LLTI 6

- Lra jf / JK

Фуг.е

фуг.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многопороговый логический элемент | 1984 |

|

SU1223359A1 |

| Многопороговый логический элемент (его варианты) | 1983 |

|

SU1261106A1 |

| МНОГОПОРОГОВОЕ УСТРОЙСТВО | 2000 |

|

RU2181926C2 |

| Устройство для обнаружения ошибокВ пАРАллЕльНОМ -РАзРядНОМ КОдЕС пОСТОяННыМ BECOM | 1979 |

|

SU830390A1 |

| Пороговый элемент | 1981 |

|

SU1046932A1 |

| Многопороговый логический элемент | 1977 |

|

SU1078620A1 |

| Пороговый логический элемент | 1981 |

|

SU991612A1 |

| Многопороговый логический элемент | 1982 |

|

SU1042183A1 |

| Сумматор унитарных кодов | 1982 |

|

SU1182511A1 |

| Многопороговый логический элемент четности | 1980 |

|

SU900455A2 |

УСТРОЙСТВО ДЛЯ ОБНАРУЖЕНИЯ СОИБОК В ПАРАЛЛЕЛЬНОМ И.-РАЗРЯДНОМ КОДЕ С ПОСТОЯННЫМ ВЕСОМ К , содержащее бярк симметричных пороговых многонолюсников, о : л и ч а р щ е ес я тем, что, с целью сокращения объема о€}о1 удования и повышения ж;тродействня, в устройство Бведешл Выходной блок aHajmsa и ( Г0 - 1) ; с I .-«аг.блоков симметричных пороговых много- полюсников, где и , с коли1чеством входов И1, где -ч I - 1 , причем выходы блоков симметричных . пороговых многополюсников соединены с входом выходного блока анализа, выход которого является контрольным выходом устройства, входы блоков си ф;ётричных пороговых многополюсников являются входга и устройства, а каждый { -и блок симметричных многополюсников содержит Т си11тетричных многополюсников, первую и втсчрую группы пороговых элементов, реализукяцих пороговую функцию в пределах от О до К, выхода симметричных многополюсников, соответствующие входной пороговой функции соединены (П .р соответствую«цими входами соответствующих пороговых элементов первой группы, выходы которых соединены с входами соответствуквдих пороговых элемейтрв второй группы, выходы кото-g .рых являются группой выходов сймметричного многополюсника.

llJvi.8

Авторы

Даты

1983-07-07—Публикация

1981-06-15—Подача