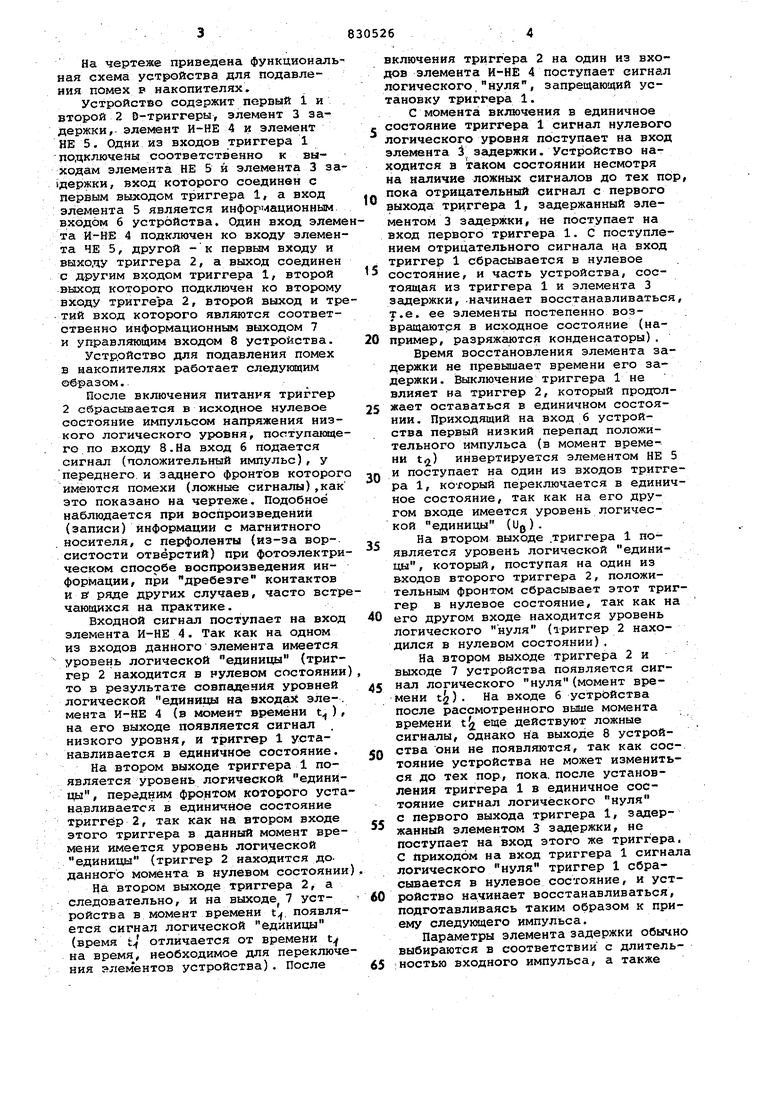

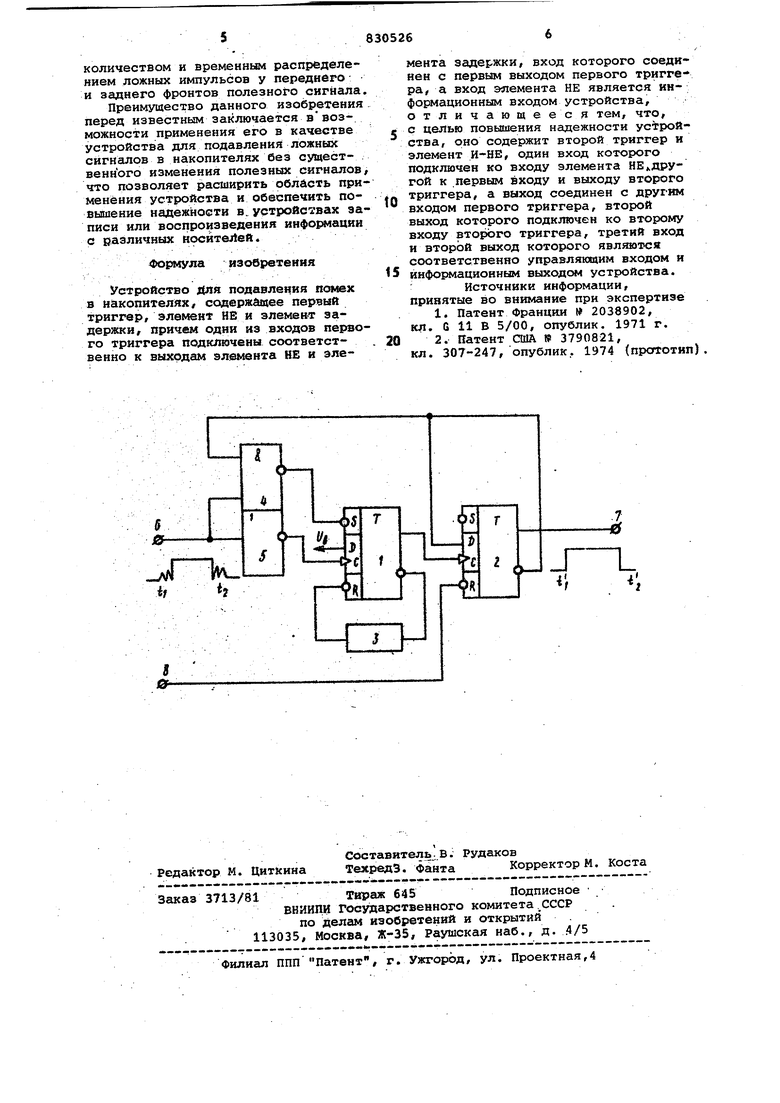

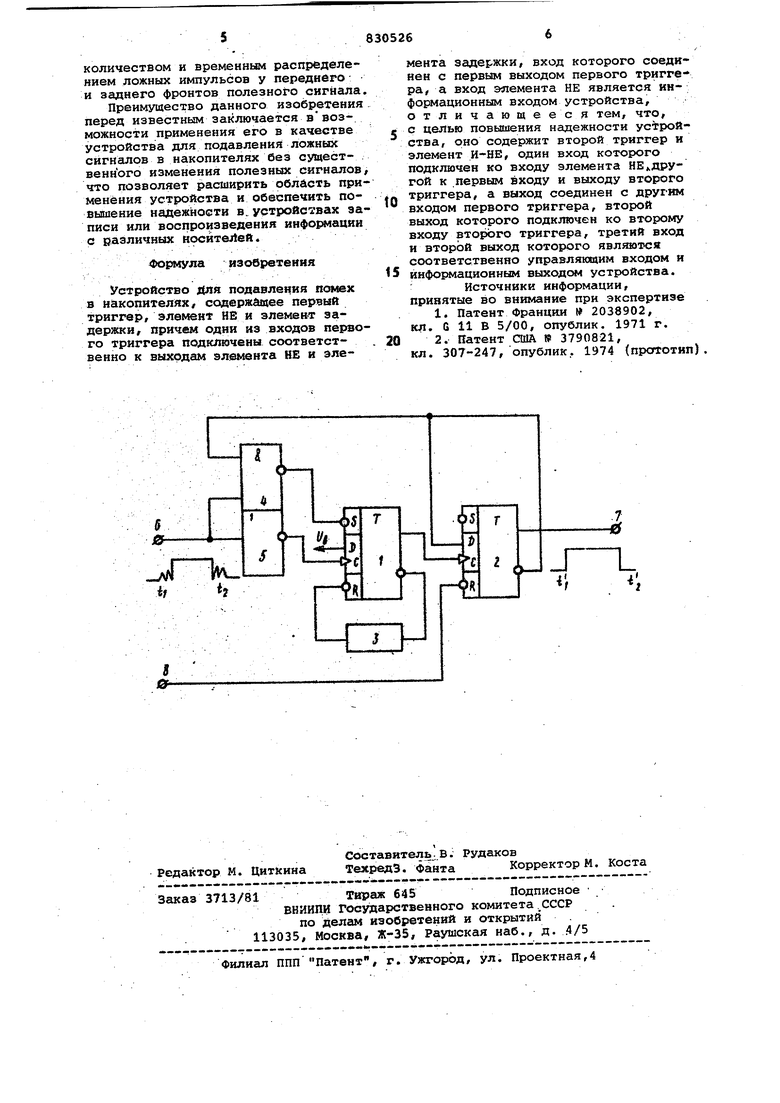

Изобретение относится к запоминаио щим устройствам, основанным на испол зовании относительного перемещения носителя записи и преобра:5ователя, и может быть использовано при записи или воспроизведении информации с магнитных или других накопителей. Известно устройство, содержгипее логические элементы и элемент задерж ки с регулируемой длительностью, которая задается регулятором таким. образом, что ее отношение к длительности периода полезных сигналов оста ется приблизительнопостоянным Недостатком этого устройства явля ется то, что оно изменяет длительность полезных сигналов и обеспечива ет подавление помех только с одной их стороны на определенном участке периода следования полезных сигналов Наиболее близким техническим решением к изобретению является устройство для подавления помех, содержащее D-триггер, элемент НЕ, две лицни задержки, входной и выходной контакты 23. Недостатком этого устройства является то, что длительность выходного полезного импульса определяется параметрами линии задержки, что снижает надежность устройства. Цель изобретения - повьлиение надежности устройства за счет получения на выходе полезных импульсов без существенного изменения их параметров по сравнению с входными. Поставленная цель достигается тем, что в устройство для подавления помех в накопителях, содержащее первый триггер, элемент НЕ и элемент задержки, причем одни из йходов первого триггера подключены соответственно к выходам элемента НЕ и элемента задержки, вход которого соединен с первым выходом первого триггера, а вход элемента НЕ является информацион-, ным входом устройства, введены второй триггер и элемент И-НЕ, один вход которого подключен ко входу элемента НЕ, другой к первым входу и выходу второго триггера, а выход соединен с другим входом первого триггера, второй выход которого подключен ко второму входу второго триггера,третий вход и второй выход которого являются соответственно управляющим входом и информационным выходом устройства. На чертеже приведена функциональ ная схема устройства для подавления помех р накопителях. Устройство содэржит первый i и второй 2 В-триггеры, элемент 3 задержки , элемент И-НЕ 4 и элемент НЕ 5. Одни из входов триггера 1 подключены соответственно к выходам элемента НЕ 5 и элемента 3 за вдержки, вход которого соединен с перв1ым выходом триггера 1, а вход элемента 5 является информационным входом б устройства. Один вход элем та 4 подключен ко входу элемен та ЧЕ 5, другой - к первым входу и выходу триггера 2, а выход соединен с другим входом триггера 1, второй выход которого подключен ко второму входу триггера 2, второй выход и тр тий вход которого являются соответственно информационным выходом 7 и управляющим входом 8 устройства. Устройство для подавления помех в накопителях работает следующим ©©разом.. После включения питания триггер 2 сбрасывается в исходное нулевое состояние импульсом напряжения низкого логического уровня, поотупакяце го по входу 8.На вход 6 подается сигнал (положительный импульс), у переднего, и заднего фронтов которог имеются помехи (ложные сигналы),как это показано на чертеже. Подобное наблюдается при воспроизведении (записи) информации с магнитного носителя, с перфоленты (из-за вор-. систости отверстий) при фотоэлектри ческом способе воспроизведения информации, при дребезге контактов к S ряде других случаев, часто встр чающихся на практике. Входной сигнал поступает на вход элемента И-НЕ 4. Так как на одном из входов данного элемента имеется уровень логической единицы (триггер 2 находится в нулевом состоянии то в результате совпаленйя уровней логической единицы на входах элемента И-НЕ 4 (в момент времени Ц) на его выходе появляется сигнал низкого уровня, и триггер 1 устанавливается в единичное состояние. На втором выходе триггера 1 появляется уровень логической единйщл, передним фронтом которого уста навливается в единичное состояние триггер 2, так как на втором входе этого триггера в данный момент времени имеется уровень логической единицы (триггер 2 находится до. данного момента в нулевом состоянии На втором выходе триггера 2, а следовательно, и на выходе 7 устройства в момент времени t. появляется сигнал логической единицы (время t./ отличается от времени t на время, необходимое для переключе ния эле1 ентов устройства) . После включения триггера 2 на один из входов элемента И-НЕ 4 поступает сигнал логического,нуля, запрещающий установку триггера 1. С момента включения в единичное состояние триггера 1 сигнал нулевого логического уровня поступает на вход элемента i задержки. Устройство находится в таком состоянии несмотря на наличие ложных сигналов до тех пор, пока отрицательный сигнал с первого выхода триггера 1, задержанный элементом 3 задержки, не поступает на вход первого триггера 1. С поступлением отрицательного сигнала на вход триггер 1 сбрасывается в нулевое состояние, и часть устройства, состоящая из триггера 1 и элемента 3 задержки, -начинает восстанавливаться, т.е. ее элементы постепенно возвращаются в исходное состояние (например, разряжаются конденсаторы). Время восстановления элемента задержки не превышает времени его задержки. Выключение триггера 1 не влияет на триггер 2, который продолжает оставаться в единичном состоянии. Приходящий на вход б устройства первый низкий перепад положительного импульса (в момент времени t) инвертируется элементом НЕ 5 и поступает на один из входов триггера 1, который переключается в единичное состояние, так как на его другом входе имеется уровень логической единицы (U0). На втором выходе .триггера 1 появляется уровень логической единицы, который, поступая на один из входов второго триггера 2, положительным фронтом сбрасывает этот триггер в нулевое состояние, так как на его другом входе находится уровень логического нуля (триггер 2 находился в нулевом состоянии). ; На втором выходе триггера 2 и выходе 7 устройства появляется сигнал логического нуля(момент времени t). На входе 6 устройства после рассмотренного выше момента времени t/ еще действуют ложные сигналы, однако на выходе 8 устройства они не появляоотся, так как состояние устройства не может измениться до тех пор, пока, после установления триггера 1 в единичное состояние сигнал логического нуля с первого выхода триггера 1, задержанный элементом 3 задержки, но поступает на вход этого же триггера. С Приходом на вход триггера 1 сигнала логического нуля триггер 1 сбрасывается в нулевое состояние, и устройство начинает восстанавливаться, подготавливаясь таким образом к приему следукядего импульса. Параметры элемента задержки обычно выбираются в соответствии с длительностью входного импульса, а также

количеством и временным распределением ложных импульсов у переднего: и заднего фронтов полезного сигнала. Преимущество данного изобретения перед известным заключается ввозможности применения его в качестве устройства для подавления ложных сигналов в накопителях без существенного изменения полезньк сигналов/ что позволяет расширить область применения устройства и обеспечить повышение надежности в,устройствах записи или воспроизведения инфО Я4ации с различных носителей.

Формула изобретения

Устройство для подавления помех в накопителях, содержащее первый триггер, элемент НВ и элемент задержки, причем одни из входов первого триггера подключены соответственно к выходам элемента НЕ и элемента задержки, вход которого соединен с первым выходом первого триггера/ а вход элемента НЕ является информационным входом устройства, отличающеес я тем, что, с целью повышения надежности устройства, оно содержит второй триггер и элемент И-НЕ, один вход которого подключен ко входу элемента НЕ другой к первым входу и выходу второго триггера, а выход соединен с другим входом первого триггера, второй выход которого подключен ко второму входу второго триггера, третий вход и второй выход которого являются соответственно управляющим входом и 5 информационным выходом устройства.

Источники информации, принятые во внимание при экспертизе

1.Патент Франции 2038902, кл. G 11 В 5/00, опублик. 1971 г.

2.Патент США № 3790821,

кл. 307-247, опублик. 1974 (прототип)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения микроЭВМ с кассетным магнитофоном | 1983 |

|

SU1396136A1 |

| Устройство для обнаружения ошибок при передаче данных по телефонному каналу | 1987 |

|

SU1559415A1 |

| Устройство для воспроизведения цифровой информации с магнитного носителя | 1983 |

|

SU1081654A1 |

| Устройство для оценки фазы периодического импульсного сигнала | 1988 |

|

SU1610601A1 |

| Цифровой асинхронный регенератор дискретных сигналов | 1990 |

|

SU1788582A1 |

| Селектор импульсов по длительности | 1981 |

|

SU978335A1 |

| Устройство для воспроизведения цифровой информации с носителя магнитной записи | 1984 |

|

SU1150649A2 |

| Устройство для коррекции сбойных кодов в кольцевом распределителе | 1979 |

|

SU888125A1 |

| Формирователь дискретных сигналов | 1979 |

|

SU809523A1 |

| Устройство для приема самосинхронизирующейся дискретной информации | 1984 |

|

SU1228296A2 |

Авторы

Даты

1981-05-15—Публикация

1979-08-15—Подача