Изобретение относится к вычислительной технике и может быть использовано в системах .связи устройств ввода-вывода с

Известно устройство сопряжения микроэвм с кассетным накопителем на магнитной ленте, содержащее входную информационную итну, два компаратора, один из которых выполнен на одновибраторе, шесть триггеров, формирователь, два счетчика и два ключа В этом устройстве входной сигнал, считанный с магнитной ленты, поступает на вход компаратора, который на выходе выделяет логический сигнал, поступающий на формирователь, выраба тызаЕСпдий HMiiyjii-сы в моменты переключения сигналов и:з нулевого состояния в едкннчное. Далее снг Налы поступают во второй компаратор,, собранньш на одновибраторе, который формирует по- стоянньш логический уровень в случаа прихода с i .iarii.HToiljoHa ЧМ-сигнала логической едпиитш и короткие импульсы при поступлении логического нуля. Затем запускаются два счетчика и три тригтера, с выхода одног о из которых логический уровень пост упает на. сдви говьой pei ncrp на ;з1Ч.;:оде схемы

К недостаткам даггного устройства относятся большие; затраты оборудова- пгя, 1ал 1чт{е в схемс таких нестабиль {1Ы.Х. элементов, как одновибратор И компаратор, отсутствием возможности коррекщш информации в случае сбоя,,

Наиболее близким к предлагаемом является устройство для сопряжения микроэвм с кассетным магнитофоном, содержащее регистр сдвига, таймер, реверсивный счетчик, коммутатор, первьш вход которого соединен через импульсный формирователь с информационным входом устройства и через элемент задержки с первыми входами: первого триггера и первого счетчика, второй вход и выход которого соединены соответственно с тактовым входом устройства и вторы ч входом первого триггера, выходом подключенного к второму входу ксзммутатора, суммирующий и вычитающий входы реверсивного счетчика соединены соответственно с первым и BTopbiN выходами коммутатора, а выход - с первым входом регистра сдвига, второй вход которого подключен к выходу таймера, а выход является информационным выходом устройства.

O 5 0 5 0

с

о 5

0

5

В устройстве для детектирования информации-использ тотся коммутатор и реверсивный счетчик. Коммутатор разделяет модулирующие импульсы логического нуля или единигуы на два канала, один из которых подключен к суммирующему входу реверсивного счетчика, другой - к вычитающему. При приеме каждого информационного бита в случае появления на входе коммутатора импульсов, частота модуляции которых соответствует логической единице 1, реверсивный счетчик увеличивает свои показания, а при приеме частотно-модулированного нуля - уменьшает« При случайном сбое или помехе модулир тощих импульсов информационного бита данные будут зарегистрированы, без искажения за счет интегрирования на реверсивном счетчике .0 начале передачи блока данных сигнализирует специальный синхронизирующий: бит, передаваемый.перед блоком данных. Первый модулирующий импульс синхронизирующего бита является признаком начала блока данных Принятый синхронизирующий бит не интегрируется на реверсивном счетчике, поэтому возможен ложный прием искаженного в канале передачи синхронизирующего битао Следовательно, недостатками прототипа являются низкая помехозащищенность синхронизирующего бита и недостаточная .достоверность обмена во всей системе в целом.

Целью изобретения является повышение достоверности обмена информацией.

Поставленная цель достигается тем, что в устройство, содержащее регистр сдвига, выход которого является информационным выходом устройства, а информационный и сдвиговый входы подключены соответственно к выходам реверсивного счетчика и таймера, су Ф1Ирующий. и вычитающий входы реверсивного счетчика соединены соответственно с информационным и-управляющим выходами .коммутатора, информа-- ционный вход которого соединен через формирователь импульса с информационным входом устройства, а через элемент задержки - с первьм входом первого триггера и входом сброса первого счетчика, счетным входом и выходом подключенного соответственно к тактовому входу устройства и второму

входу первого триггера, выход которого соединен с управляющим входом коьгмутатора, введены второй счетчик, два триггера, три элемента И, три элемента ИЛИ и элемент НЕ, причем выход первого элемента ИЛИ соединен с устано-. вочным входом реверсивного счетчика и входом таймера, первый вход - с первыми входами второго и третьего триггеров и выходом первого элемента И, первым входом соединенного с выходом второго триггера, выход третьего триггера подключен к первым вхо- дам второго и третьего элементов И, вторые входы которых соединены с выходом таймера и счетным входом второ .го счетчика, третий вход второго элемента И подключен к первым входам второго и третьего элементов ИЛИ и через элемент НЕ к третьему входу третьего элемента И, выход которого подключен к вторым входам первого и третьего элементов ИЛИ, выход второго счетчика соединен с вторым входом второго элемента ИЛИ, вторые входы второго и третьего триггеров подключены соответственно к выходам второго и третьего элементов ИЛИ, третьим входами соединенных с входом начального сброса устройства, второй вход первого элемента И соединен с управляющим выходом коммутатора.

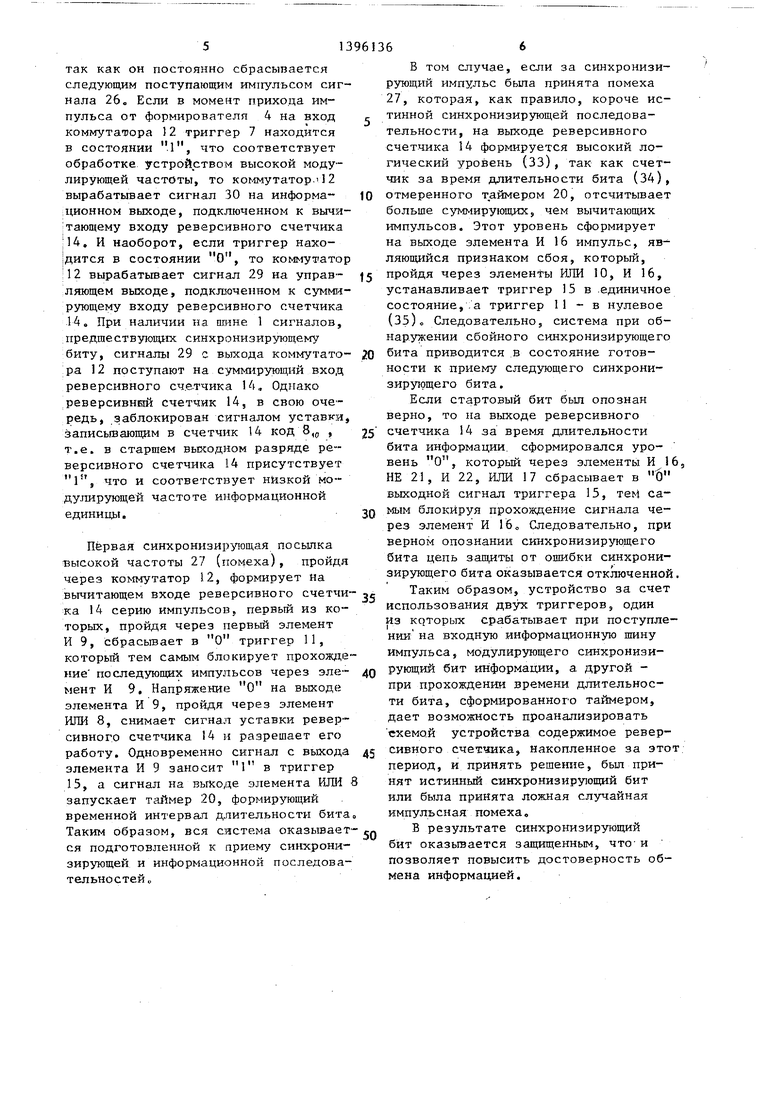

На фигс представлена блок-схема предлагаемого устройства; на фиг.2 - временные диаграммы работы устройст- вао

Устройство (фиг.1) содержит шины 1,2 и .3 информационного и тактового входов и входа начального сброса устройства, формирователь 4 импульса, элемент 5 задержки, первые счетчик 6, триггер 7, элемент ИЛИ 8 и элемент И 9, вторые элемент ИЛИ 10 и триггер 11, коммутатор 12, второй счетчик 13, реверсивный счетчик 14, третий триггер 15, второй элемент И 16, третий элемен т ИЛИ 17 шину 18 информационного выхода устройства, регистр 19 сдвига, таймер 20, элемент НЕ 21 и третий элемент И 22,

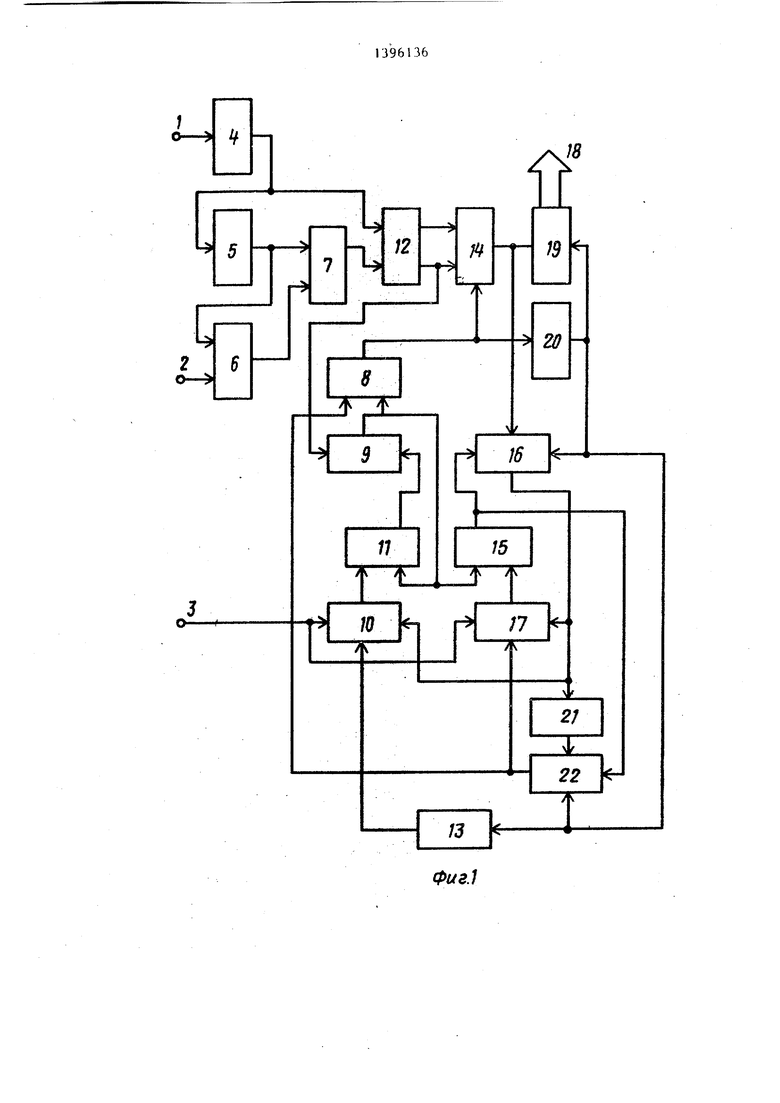

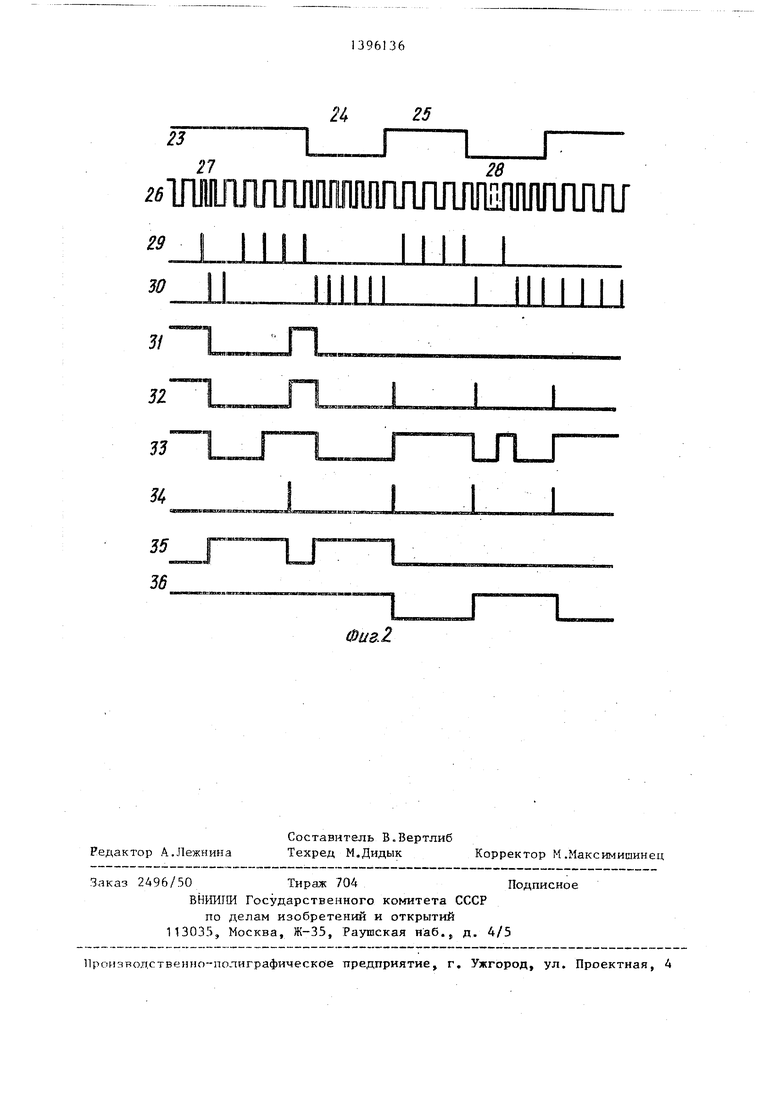

На фиг„2 обозначены: 23 - огибающая информационного сигнала; 24 - синхронизирую1ций бит; 25 - информационные биты; 26 - промодулированный информационный сигнал на шине 1; 27 - помеха в виде ложного импульса;

28 - помеха в виде выпадения импульса; 29 - сигнал на суммирующем входе реверсивного счетчика 14; 30 - сигнал на вычитающем входе реверсивного счетчика 14; 31 - сигнал на выходе триггера 11; 32 - сигнал записи уставки 8,0 в реверсивный счетчик 14; 33 - сигнал на выходе реверсивного счетчика; 34 - выходной сигнал таймера 20; 35 - выходной сигнал триггера 15; 36 - информация, побитно принимаемая в сдвиговый регистр 19

Уе-тройство работает следующим образом.

Перед началом приема данных по шине 3 подается кратковременньгй импульс, устанавливающий триггер 15 в единичное состояние, а триггер 11 - в нулевое. Эти состояния триггеров 15 и 11 являются признаком готонное ти системы к приему первого синхронизирующего бита 24„ По шине 1 поступает частотно-модулированньй информационный сигнал 26 (высокая частота модулирует информационньп нуль, низкая - единицу ) на вход формирова-

теля 4, на выходе которого образуется серия узких импульсов, сформированных по переднему фронту входного сигнала С выхода формирователя 4 сигналы поступают на входы коммутатора 12 и элемента 5 задержки С выхода элемента 5 задержки задержан- ньй импульс поступает на входы триггера 7 и счетчика 6. С приходом фронта входного сигнала на шину 1

триггер 7 устанавливается в единичное состояние, а счетчик 6 приводится в исходное состояние, соответствующее началу его счета. Коэффициент пересчета счетчика 6 выбран

так, чтобы время его перевыполнения было равно среднему арифметическому между периодом высокой и низкой частот, используемых для кодировки информационных нуля и единицы. При

этом импульс переноса на выходе счетчика 6, соединенного с входом сброса триггера 7, возникает до прихода следующего модулирующего сигнала 26 на шину 1 в случае низкой

частоты сигнала, соответствующей инормационной единице..„ Если частота игнала. 26 соответствует инфор та- ционному нулю, то импульс переноса на выходе счетчика 5 не возникает.

так как он постоянно сбрасывается следующим поступающим им гульсом сигнала 26. Если в момент прихода импульса от формирователя 4 на вход коммутатора 12 триггер 7 находится в состоянии л, что соответствует обработке устройством высокой модулирующей частоты, то ког-мутатор. 2 вырабатывает сигнал 30 на информа- ;ционном выходе, подключенном к вычи- тающему входу реверсивного счетчика |14. И наоборот, если триггер нахо- 1дится в состоянии О, то коммутатор |12 вырабатывает сигнал 29 на управ- ляющем выходе, подкл-юченном к рующему входу реверсивного счетчика

14.При наличии на шине 1 сигналов, .предшествующих синхронизирующему

биту, сигналы 29 с выхода коммутато- ра 12 поступают на сумш1рующий вход реверсивного счетчика 14, Однако реверсивннй счетчик 14, в свою очередь, заблокирован сигналом уставки, записьшающим в счетчик 14 код 8,;, , т.е. в старшем выходном разряде реверсивного счетчика 14 присутствует 1, что и соответствует низкой модулирующей частоте информационной единицы.

Первая синхронизирующая посьтка тзысокой частоты 27 (помеха) , пройдя через коммутатор 12, формирует На вычитающем входе реверсивного счетчи ка 14 серию импульсов, первый из которых, пройдя через первый элемент И 9, сбрасьгоает в О триггер 11, который тем самым блокирует прохождение последующих импульсов через эле- мент И 9, Напряжение О на выходе элемента И 9, пройдя через элемент ИЛИ 8, снимает сигнал уставки реверсивного счетчика 14 и разрешает его работу. Одновременно сигнал с вьасода элемента И 9 заносит 1 в триггер

15,а сигнал на выводе элемента ИЛИ запускает таймер 20, формирующий временной интервал длительности бита Таким образом, вся система оказывает ся подготовленной к приему синхронизирующей и информационной последовательностей „

В том случае, если за синхронизирующий импульс бьша принята помеха 27, которая, как правило, короче истинной синхронизирующей последовательности, на выходе реверсивного счетчика 14 формируется высокий логический уровень (ЗЗ), так как счетчик за время длительности бита (34), отмеренного т аймером 20, отсчитывает больше суммируюшкх, чем вычитающих импульсов. Этот уровень сформирует на выходе элемента И 16 импульс, яв ляющийся признаком сбоя, который, пройдя через элементы ИЛИ 10, И 16, устанавливает триггер 15 в .единичное состояние,:а триггер I1 - в нулевое (35)о Следовательно, система при обнаружении сбойного синхронизирующего бита приводится в состояние готовности к приему следующего синхронизирующего бита.

Если стартовый бит был опознан верно, то па вихоце реверсивного счетчика 14 за время длительности бита информации, сформировался уровень О, который через элементы И 1 НЕ 21, И 22, ИЛИ 17 сбрасывает в б выходной сигнал триггера 15, тем самым блокируя прохождение сигнала через элемент И 1бо Следовательно, при верном опознании синхронизирующего бита цепь защиты от ошибки синхронизирующего бита оказывается отключенной

Таким образом, устройство за счет использования двух триггеров, один из KQTopbrx срабатывает при поступлении на входную информационную шину импульса, модулирующего синхронизирующий бит информации, а другой - при прохождении времени длительности бита, сформированного таймером, дает возможность проанализировать схемой устройства содержимое реверсивного счетчика, накопленное за это период, и принять решение, был принят истинный синхронизирующий бит или была принята ложная случайная импульсная помеха,

В результате синхронизирующий бит оказьтается защищенным, что- и позволяет повысить достоверность обмена информацией.

О

-

W

19

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения микроЭВМ с кассетным магнитофоном | 1982 |

|

SU1345185A1 |

| Датчик испытательных текстов | 1988 |

|

SU1571786A1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ | 2011 |

|

RU2450447C1 |

| ГЕНЕРАТОР ЗАДЕРЖАННЫХ ИМПУЛЬСОВ | 2006 |

|

RU2328819C2 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Устройство для считывания информации с металлических жетонов | 1987 |

|

SU1562944A1 |

| Устройство для определения моментов экстремумов гармонических сигналов | 1981 |

|

SU1004899A1 |

| Многоканальное устройство для измерения электрической энергии | 1990 |

|

SU1762253A1 |

| Формирователь последовательности прямоугольных импульсов | 1986 |

|

SU1624678A1 |

| Частотный модулятор | 1984 |

|

SU1145473A1 |

J4i

В

Zff

п

15

Ю

17

J3

иЛ

Фиг.1

Д25

2728

б тт ттттттт I IIII IIII I

0 IIIIII I тип

31

J .L™J

б дяюи||ЦЮ1Кдая;еиа1 аиЕа 1НОт.тгц ; Ж ададаии1дааяжд|авдспмвва «1.1а1и|1и1 А1 и

36

01/8.2

| Захаров Д.С | |||

| и др | |||

| Сопряжение кассетного магнитофона с микропро- | |||

| цессорной системой | |||

| - Вопросы атомной науки и техники | |||

| Сер.Ядерное приборостроение | |||

| Вып | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для сопряжения микроЭВМ с кассетным магнитофоном | 1982 |

|

SU1345185A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-05-15—Публикация

1983-03-15—Подача