(54) УСТРОЙСТВО СИНХРОНИЗАЦИИ ЦИФРОЫЛХ СИГНАЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи служебныхСигНАлОВ для ТЕлЕфОННОй СТАНцииС ВРЕМЕННыМ уплОТНЕНиЕМ цифРОВыХСигНАлОВ | 1977 |

|

SU831093A3 |

| Устройство для преобразования виртуального адреса в реальный адрес | 1979 |

|

SU1162377A3 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1986 |

|

SU1411809A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для преобразования малокадрового телевизионного стандарта | 1985 |

|

SU1256245A1 |

| Устройство для регистрации цифровой информации | 1986 |

|

SU1386915A2 |

| Многоканальное измерительно-регистрирующее устройство (его варианты) | 1982 |

|

SU1038807A1 |

| Запоминающее устройство | 1985 |

|

SU1259336A2 |

| Устройство для ввода информации | 1988 |

|

SU1536368A1 |

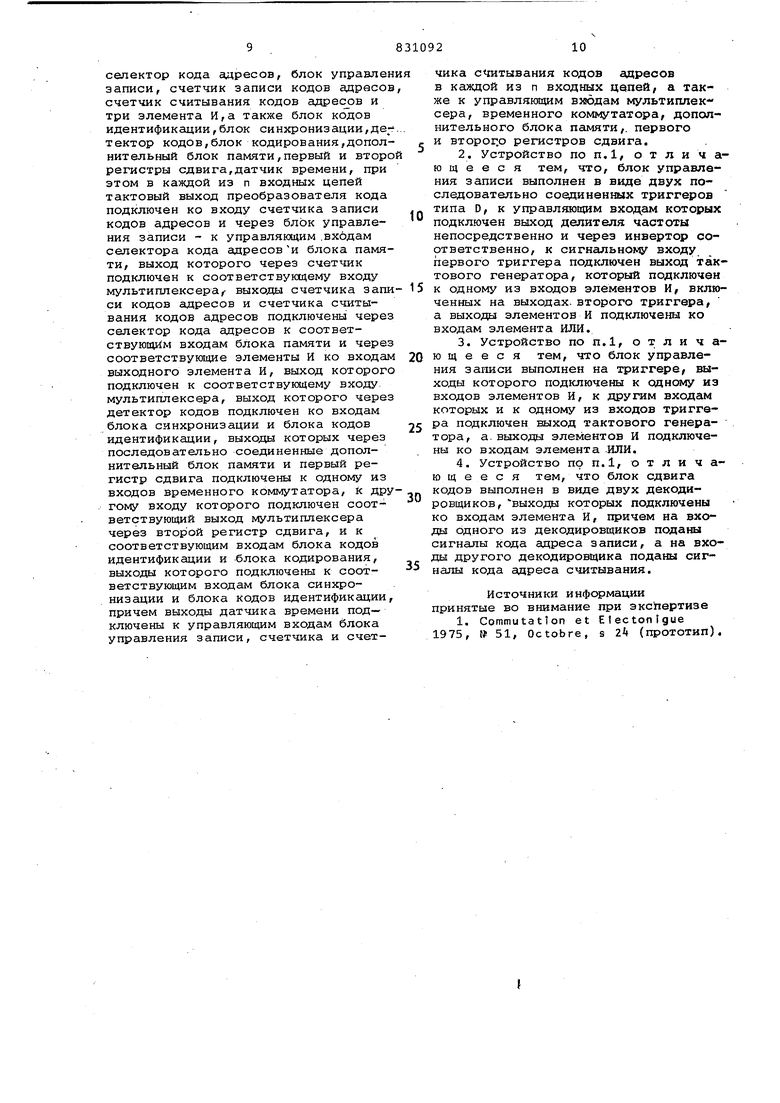

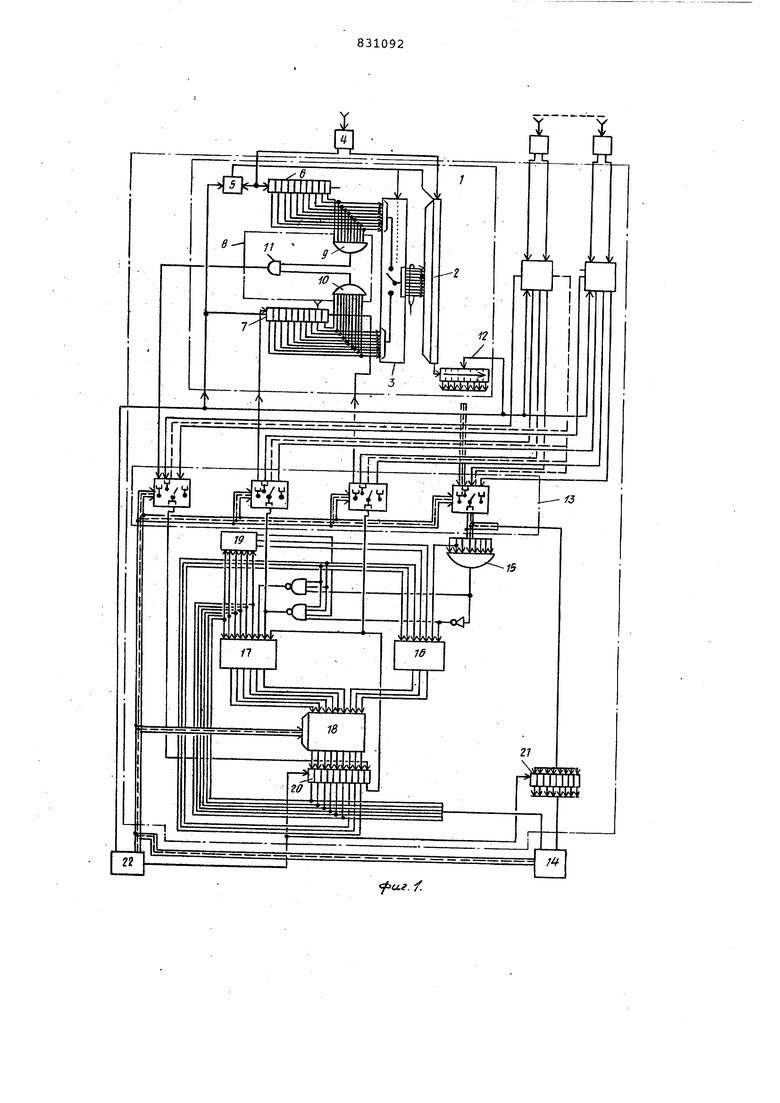

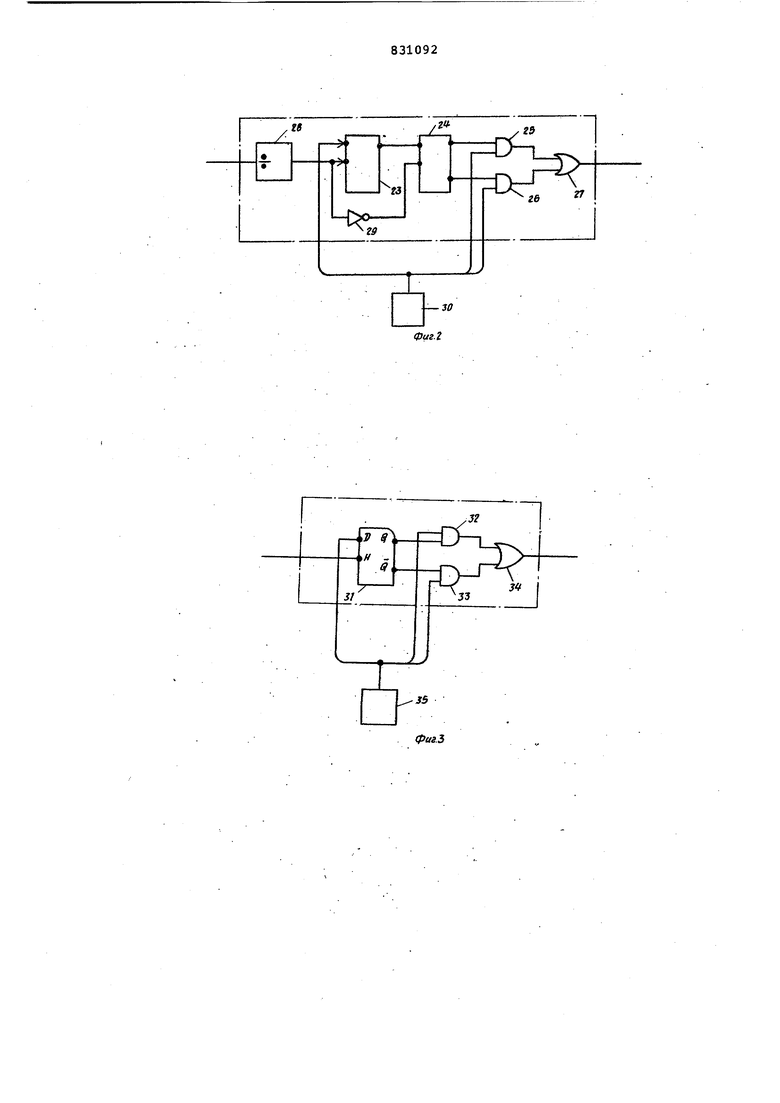

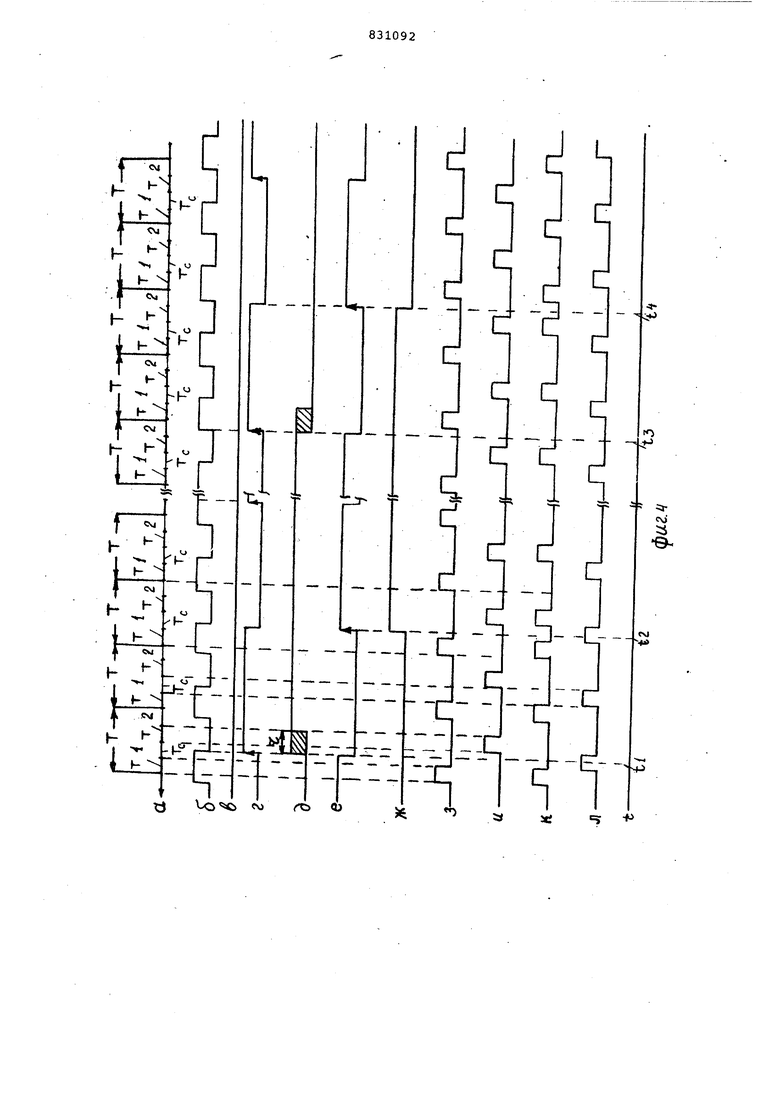

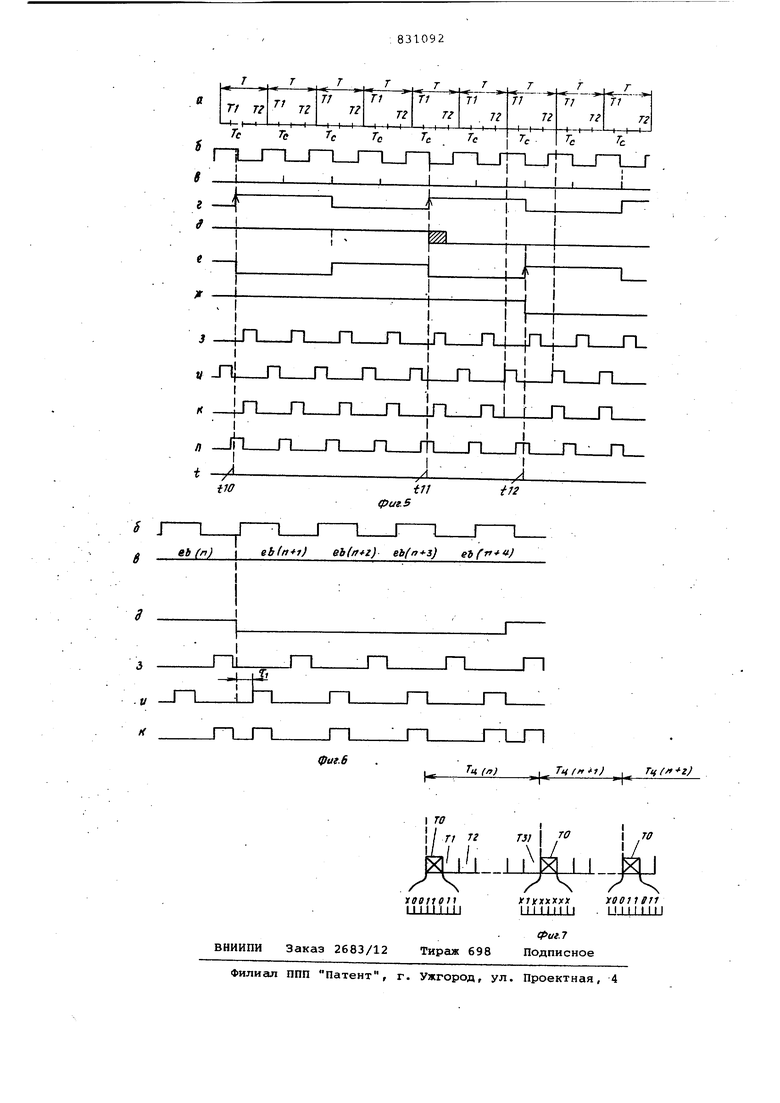

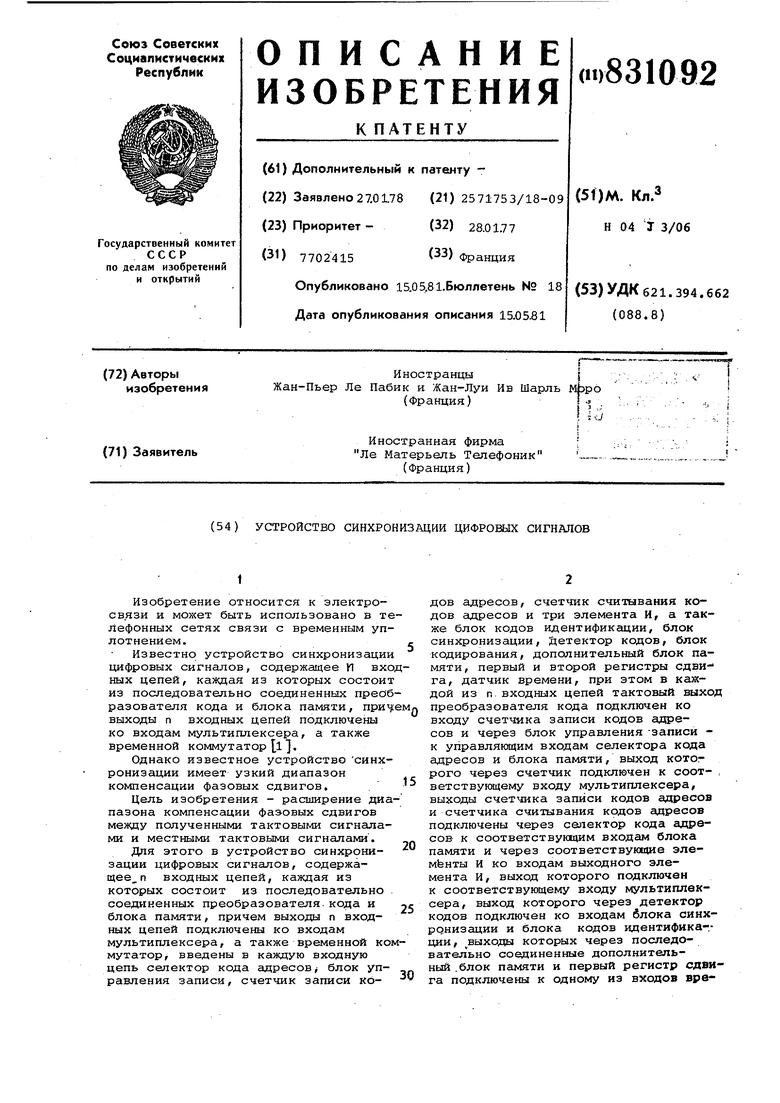

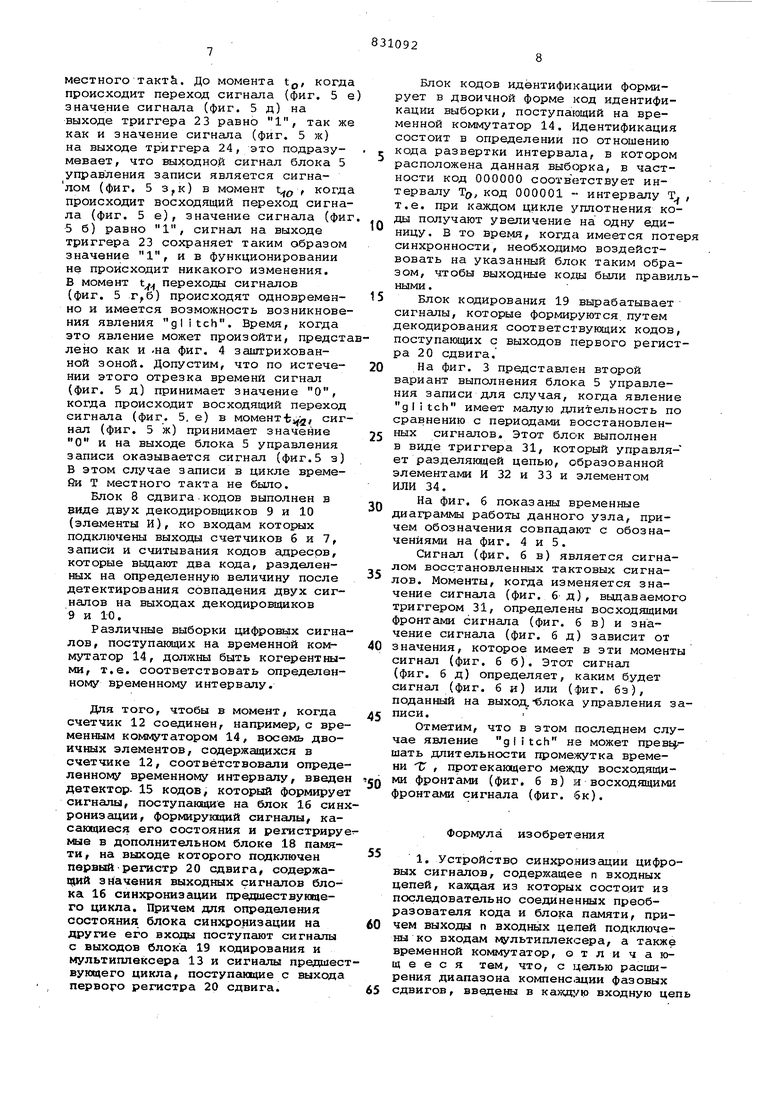

Изобретение относится к электросвязи и может быть использовано в т лефонных сетях связи с временным уп лотнением, Известно устройство синхронизаци цифровых сигналов, содержащее И вх ных цепей, каждая из которых состои из последовательно соединенных прео разователя кода и блока памяти, при выходы п входных цепей подключены ко входам мультиплексера, а также временной коммутатор {l. Однако известное устройство синхронизации имеет узкий диапазон компенсации фазовых сдвигов, . Цель изобретения - расширение диа пазона компенсации фаэовых сдвигов между полученными тактовыми сигнгшагли и местными тактовыми сигналами. Для этого в устройство синхронизации цифровых сигналов, содержа цее п входных цепей, каждая из которых состоит из последовательно соединенных преобразователя.кода и блока памяти, причем выходы п входных цепей подключены ко входам мультиплексера, а также временной ко мутатор, введены в каждую входную цепь селектор кода адресовj блок управления записи, счетчик записи кодон адресов, счетчик считывания кодов адресов и три элемента И, а также блок кодов идентификации, блок синхронизации, Детектор кодов, блок кодирования, дополнительный блок памяти, первый и второй регистры сдвига, датчик времени, при этом в каждой из п. входных цепей тактовый выход преобразователя кода подключен ко входу счетчика записи кодов адресов и через блок управления -записи к управляющим входам селектора кода адресов и блока памяти, выход котог рого через счетчик подключен к соот- , ветствующему входу мультиплексера, выходы счетчика записи кодов адресов и счетчика считывания кодов адресов подключены через селектор кода адресов к соответствующим входам блока памяти и через соответствуквдие элементы И ко входам выходного элемента И, выход которого подключен к соответствующему входу мультиплексера, выход которого через детектор кодов подключен ко входам блока синхронизации и блока кодов идентифика-.ции, выходы которых через последовател ьно соединенные дополнительный .блок памяти и первый регистр сдвига подключены к одному из входов временного коммутатора, к другому входу которого подключен соответствующий выход мультиплексера через второй регистр сдвига, и к соответствующим входам блока кодов идентификации и блока кодирования, выходы которого подключены к соответствукяцим входам блока синхронизации и блока кодов идентификации, причем выходы датчика времени подключены к управляющим входам блока управления записи, сче чика, счетчика считывания кодов адресов в каждой из п входных цепей, а также к управляющим вхсдам мульти плексера, временного коммутатора, дополнительного блока памяти, первого и второго регистров сдвига. Кроме того, блок управления запи си выполнен в виде двух последовате но соединенных триггеров типа О, к управляющим входам которых подключе выход делителя частоты непосредстве но и через инвертор соответственно, к сигнальному входу первого триггера подключен выход тактового генера ра, который подключен к одному из в дов элементов И, включенных на выхо дах второго триггера, а выходы элем тов И подключены ко входам элемента ИЛИ. Блок управления записи выполнен ояа. триггере, выходы которого подклю чены к одному из вхсдов элементов И к другим входам которых и к одному из входов триггера подключен выход тактового генератора, а выходы элементов И подключены ко входам элемента ИЛИ. Блок сдвига кодов выполнен в вид двух декодировщиков, выходы которых подключены ко входам элемента И, причем на входы одного из декодировщиков поданы сигналы кода адреса записи, а на входа другого - сиг налы кода адреса считывания. На фиг. 1 представлена структурная электрическая схема предложенного устройства; на фиг. 2 и 3 варианты выполнения блока управления записи; на фиг. 4-6 - временные диаграммы, поясняющие работу блока управления записи/ на фиг.7 временная диаграмма распределения кодов разверток в цикле входных сиг налов. Устройство синхронизации содержит п входных цепей 1, из ко торых состоит из блока 2 памяти, селектора 3 кода адресов, преобразователя 4 кода, блока 5 управления записи, счетчика 6 записи кодов адресов, счетчика 7 считывания кодов адресов, блока 8 сдвига кодов, состоящего из Элементов И 9 и 10 (могу быть выполнены в виде декодировщиков 9 и 10), выходного элемента И и счетчика 12, а также мультиплексора 13, временной коммутатор 14, д тектор 15 кодов, блок 16 синхрониации, блок 17 кодов идентификации, ополнительный блок 18 памяти, блок 9 кодирования, первый регистр 20 двига и второй регистр 21 сдвига, атчик 22 времени. Блок управления записи (фиг.2) состоит из триггеров 23 и 24 типа D, элементов И 25 и 26, элемента ИЛИ 27,, делителя 28 частоты, инвертора 29 и тактового генератора 30. Блок управления записи (фиг.З) состоит из триггера 31, элементов И 32 и 33, элемента ИЛИ 34 и тактового генератора 35. Устройство работает следующим образом. На вход казкдой из п входных цепей, выполнение которых идентично, поступают импульсно-кодовые сигналы, содержащие как это показано на фиг.7, в каждом Тц цикле тридцать два временных интервала TQ, Т , ......Т, причем длительность каждого из них такова, что они передают восемь последовательных двоичных элементов, причем временной интервал Т в каждом цикле используется для того, чтобы передать код одной из двух разверток. Код одной развертки образован последовательностью двоичных элементов xOOllOll, где двоичный элемент ( х) означает, что его величину не следует принимать во внимание, а в коде другой развертки, образованной последовательностью xlxxxxxx только один второй двоичный элемент является значащим. Каждый временной интервал, занимагаций в кодах разверток одно и то же место, определяет канал. Входшле сигналы поступают на вход преобразователя 4 каждой из п входных цепей, который бсущетсвляет перекодирование принятых сигналов, причем на первом выходе формируются сигналы, перекодированные в двоичшлй код, а на втором выходе выделяются восстановленные тактовые сигналы, т.е сигнсшы, синхронные с входными сигналами. . Преобразованные в двоичный код сигналы (фиг.4 в, 5 в) регистрируются в блоке 2 памяти, причем для записи сигналов в блок 2 памяти предусмотрен счетчик 6 записи кодов адресов, на вход которого поступают восстановленные тактовые сигналы с преобразователя 4 кода, а для считывания - счетчик считывания кодов 7 адресов, на вход которого поступает последовательность с выхода датчика 22 времени. Кроме того, с блоком 2 памяти соединен блок 5 управления записи, обеспечивающий возможность записи сигналов, по крайней мере, на двух тактах 5, и Т2(фиг.4 а, фиг.З а) цикла, длительность которог го Т, и вход селектора 3 кода адресов, который исходя из кодов, формируемлх счетчиками 6 и 7 записи и считывания кодов адресов , выдает соответствующий код на входы кодов адресов блока 2 памяти. Кроме того, между выходами счет чиков 6 и 7 записи и считывания ко дов адресов включен блок 8 сдвига кодов, выполненный в виде двух элементов И 9 и 10, выходы которых подключены ко входам выходного элем та И 11, обеспечиваквдий сближение или разделение кодов, вырабатываемых счетчиками 6 и 7. записи и считывания кодов адресов, чтобы между ними оставался определенный промежу ток- времени. Выход, блока 2 памяти соединен со входом счетчика 12, который обе чивает считывание на другом такте Т цикла (фиг.4 а, фиг . 5 а), причем сигналы сдвига поступают на счетчик 12 с выхода датчику.времени в момент TC, (фиг. 4 л, фиг.5 л).С выхода счетчика 12 преобразованный в параллельный код сигнал через после довательно соединенные мультиплексер 13 и второй регистр 21 сдвига поступает на вход временного коммутатора 14. На управлякяцие входы мул типлексера 13 и временного коммутатора 14 поступают сигналы с датчика 22 времени. Во время цикла уплот нения вход мультиплексора 13 поочередно подключается к различным выхо дам счетчика 12 каждой из п входны цепей. Мультйплексер М/3 подкэтючен ко входу детектора 15 кодов, выход которого подключен к блоку 16 синхр низации я к блоку 17 кодов йдентифи кации, выход которого подключен к дополнительному блоку 18 памяти, сигналы с выхода которого через пер вый регистр 20 сдвига поданы -на временной коммутатор 14. Блок управления записи (фиг.2) состоит -из последовательно соединен ных триггеров 23 и 24, которые под Действием сигнала, поступакадего на вход Н (фиг. 4 г, фиг. 5 г) передают на выход сигнал, имеющий на вх де D (фиг. 4 б, фиг. 5 б). Выход Qi триггера 23 соединен со входом О триггера 24, выходы Qj. Q котсфого соединены соответственно с первыми входами элементов И 25 и 26, выходы которых соединены, со входами элемента ИЛИ 27. На вторые входа элементов Vi 25 и 26 поступают соответственно сигналы с выхода тактового генератора 30 (фиг. 4 з, и, фиг. 5 3, и), каиодый из которых соответствует моменту записи Т и Т2. Вход Н триггера 23 соединен с выходом делителя частоты 28 на четыре, а вход Н триггера 4 соединён с выходом инвертора 29, вход которо подключен к выходу делителя 28 часторы. На вход делителя 28 частоты поступают восстановленные тактовые сигналы, а на вход D триггера 23 поступают сигналы с датчика 22 времени (фиг. 4 б, фиг. 56.). На фиг. 4 изображены временные диаграммы, поясняющие работу блока управления записи для случая, когда ритм полученных сигналов является более быстрым, чем ритм местных тактовых сигналов. На фиг. 4 а показано распределение моментов записи Т и Тд и моментов считывания Т внутри цикла, длительность которого равна Т, В момент одновременно имеют место переход Ьигнала (фиг. 46), который подан на вход D триггера 23, и переход сигнала (фиг.4 г), поданного на вход Н. В течение времени Т сигнал (фиг. 4 д) на выходе триггера является неопределенным (заштрихованная зона), и после этого сигнал принимает какое-либо значение 1 или О. В случае, представленном на фиг. 4 д,он принимает значение 1. В момент tg происходит возрастание перехода сигнала (фиг. 4 е) таким образом, что на выходе триггера 24 сигнал принимает значение сигнала (фиг. 4 д), а именно 1,. причем возрастание перехода сигнала (фиг. 4е) происходит значительно позднее того момента, когда происходит явление gfitch. В случае, представленном на фиг.4, сигнал (фиг. 4 ж) до момента 1л имел значение О, элемент И 25 (фиг. 2) был открыт, а элемент И 26 закрыт и на выходе блока управления записи 5 имелся сигнал (фиг. 4 к), который был ничем иным, как сигналом (фиг. 4 з), в момент t/j происходит изменение значения сигнала (фиг. 4 ж) так, что за один цикл такта происходит запись в блок 2 памяти в момент времени Т и Т, Поскольку ритм полученных сигналов является более быстрым, чем ритм местных тактовых сигналов, возрастающий фронт сигнала (фиг. 4 г), который в момент времени t соответствует нисходящему фронту сигнала (фиг. 4 б), в момент tg соответствует восходящему фронту этого сигнала, в этот момент опять имеет место явление glitch, что указано заштрихованной зоной. Если допуСтить, что в конечном итоге сигнал (фиг. 4 д) принимает значение О, то в момент t, когда происходит восходящий переход сигнала (фиг. 4 е), сигнал (фиг. 4 ж) принимает значение О, в результате чего на выходе блока управления записи прявляются импульсы сигнала (фиг. 4 з), причем каждый из импульсов этого сигнала соответствует двоичнОму элементу входного сигнала. Фиг. 5 относится к случс1Ю, когда длительность двоичных элементов превышает длительность одного цикла

местного тактЬ. До момента t, когда происходит переход сигнала (фиг. 5 е значение сигнала (фиг. 5 д) на выходе триггера 23 равно 1, так же как и значение сигнала (фиг. 5 ж) на выходе триггера 24, это подразумевает, что выходной сигнал блока 5 управления записи является сигналом (фиг. 5 з,к) в момент когда происходит восходящий переход сигнала (фиг. 5 е), значение сигнала (фиг 5 б) равно 1, сигнал на выходе триггера 23 сохраняет таким образом значение 1, и в функционировании не происходит никакого изменения. В момент t переходы сигналов (фиг. 5 г,б) происходят одновременно и имеется возможность возникновения явления glitch. Время, когда это явление может произойти, предсталено как и .на фиг. 4 заштрихованной зоной. Допустим, что по истечении этого отрезка времени сигнал (фиг. 5 д) принимает значение О, когда происходит восходящий переход сигнала (фиг. 5. е) в MOMeHT-bj ;2, сигнал (фиг. 5 ж) принимает значейие О и на выходе блока 5 управления записи оказывается сигнал (фиг.5 з)

8этом случае записи в цикле времейи Т местного такта не было.

Блок 8 сдвига кодов выполнен в риде двух декодировщиков 9 и 10 (элементы И), ко входам которых подключены выходы счетчиков б и 7, записи и считывания кодов адресрв, которые вБщают два кода, разделенных на определенную величину после детектирования совпадения двух сигналов на выходах декодировщиков

9и 10.

Различные выборки цифровых сигналов, поступающих на временной коммутатор 14, должны быть когерентными, т.е. соответствовать определенному временному интервалу.

Для того, чтобы в момент, когда счетчик 12 соединен, например, с временным коммутатором 14, восемь двоичных элементов, содержащихся в счетчике 12, соответствовали определенному временному интервалу, введен детектор. 15 кодов, который формирует сигналы, поступающие на блок 16 синхронизации, формирукадий сигналы, касающиеся его состояния и регистрируе мые в дополнительном блоке 18 памяти, на выходе которого подключен первыйрегистр 20 сдвига, содержащий значения выходных сигналов блока 16 синхронизации предшествующего цикла. Причем для определения состояния блока синхронизации на другие его входы поступают сигналы с выходов блока 19 кодирования и мультиплексера 13 и сигналы предшесвующего цикла, поступагацие с выхода первого регистра 20 сдвига.

Блок кодов идентификации формирует в двоичной форме код идентификации выборки, поступающий на временной коммутатор 14. Идентификация состоит в определении по отношению кода развертки интервала, в котором расположена данная выборка, в частности код 000000 соответствует интервалу Tj, код 000001 - интервалу Т т.е. при каждом цикле уплотнения коды получают увеличение на одну единицу, в то время, когда имеется поте синхронности, необходимо воздействовать на указанный блок таким образом, чтобы выходные кодцл были правилHHivai.

Блок кодирования 19 вырабатывает сигналы, которые формируются, путем декодирования соответствугацих кодов, поступающих с выходов первого регистра 20 сдвига.

На фиг. 3 представл€;н второй вариант выполнения блока 5 управления записи для случая, когда явление glitch имеет малую длительность по сравнению с периодами восстановленных сигналов. Этот блок выполнен в виде триггера 31, который управляет разделяквдей цепью, образованной элементами И 32 и 33 и элементом ИЛИ 34.

На фиг. 6 показаны временные диаграммы работы данного узла, причем обозначения совпадают с обозначениями на фиг. 4 и 5.

Сигнал (фиг. 6 в) является сигналом восстановленных тактовых сигналов. Моменты, когда изменяется значение сигнала (фиг. 6 д), выдаваемог триггером 31, определены восходящими фронтами сигнала (фиг. б в) и значение сигнала (фиг. б д) зависит от значения, которое имеет в эти момент сигнал (фиг. 6 б). Этот сигнал (фиг. б д) определяет, каким будет сигнал (фиг. б и) или (фиг. 6з), поданный на выход.блока управления зписи.

Отметим, что в этом последнем случае явление glitch не может превцшать длительности проме:«утка времени ТГ , протекающего восходящими фронтами (фиг. б в) и восходящими фронтами сигнала (фиг. бк).

Фор1иула изобретения

ffug.-f. ) M «

Авторы

Даты

1981-05-15—Публикация

1978-01-27—Подача