(54) УСТРОЙСТВО ДЛЯ ОРГАНИЗАЦИИ ОЧЕРЕДИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для организации очереди | 1982 |

|

SU1070554A1 |

| Устройство для организации очередности приема информации | 1983 |

|

SU1128255A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ПРИОРИТЕТА | 1992 |

|

RU2108618C1 |

| Коммутатор каналов для телеметрической системы | 1979 |

|

SU855714A1 |

| Устройство для моделирования систем массового обслуживания | 1986 |

|

SU1325501A1 |

| Устройство для обслуживания сообщений | 1983 |

|

SU1128256A1 |

| Адаптивная система обработки данных | 1984 |

|

SU1267429A1 |

| Устройство для обслуживания запросов | 1986 |

|

SU1383354A1 |

| Устройство приоритета | 1986 |

|

SU1365084A1 |

| Электронная вычислительная машина для ускоренной обработки запросов прерываний | 1988 |

|

SU1621029A1 |

I

Изобретение относится к вычислительной технике и может быть использовано в системах группового управления.

Известно устройство для организации очереди заявок, содержащее триггеры, элементы И, ИЛИ, регистр сдвига 1.

Такое устройство не позволяет организовать равноприоритетное обслуживание заявок.

Наиболее близким к предлагаемому по технической сущности и достигаемому результату является многоканальное устройство для управления очередностью обработки запросов, содержащее регистры, счетчики, узел сравнения, элементы И, НЕ, элемент задержки, триггеры 2.

Это устройство сложно из-за больщого количества оборудования.

Цель изобретения - повыщениё быстродействия устройства,

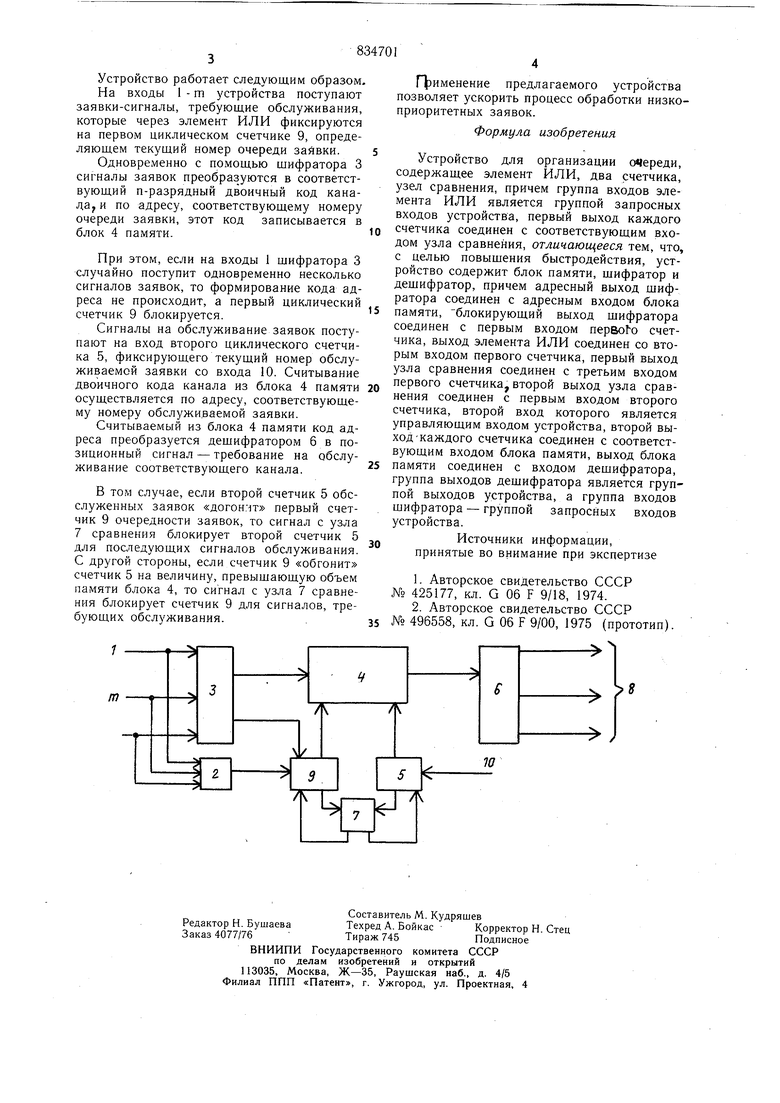

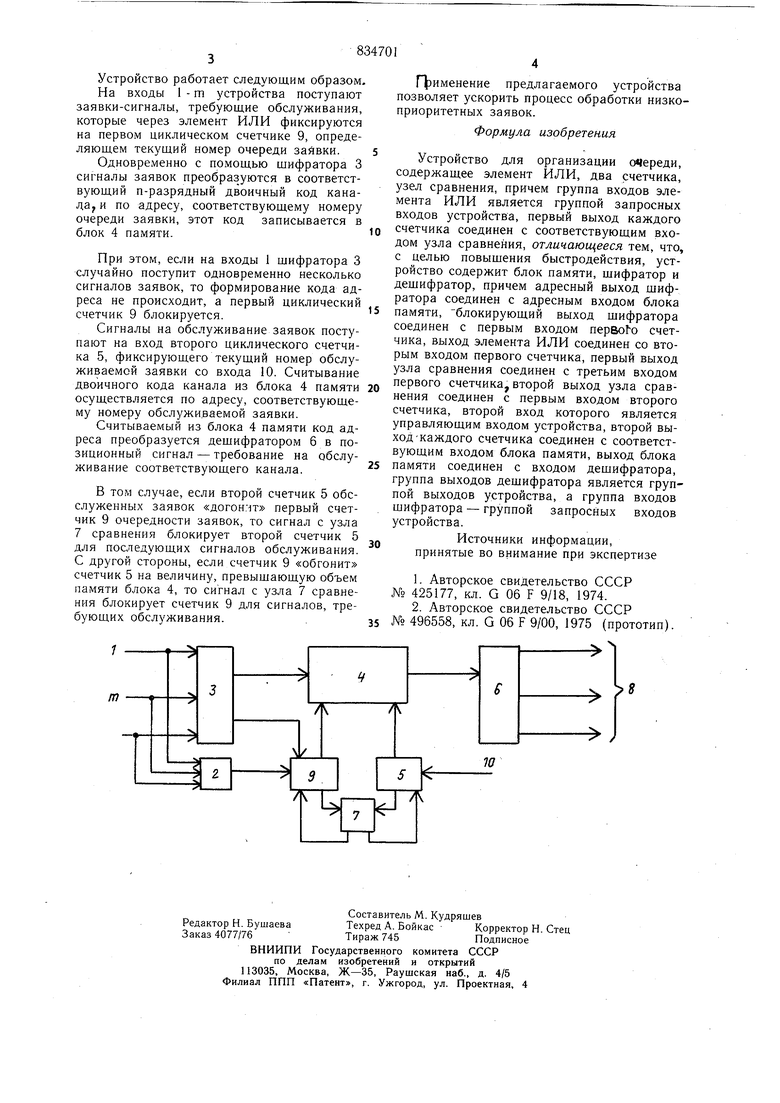

Роставленная цель достигается тем, что в устройство для организации очереди, содержащее элемент ИЛИ, два счетчика, узел сравнения, причем группа входов элемента ИЛИ является группой запросных входов устройства, первый выход каждого счетчика

соединен с соответствующим входом узла сравнения, введены блок памяти, шифратор и дешифратор, адресный выход шифратора соединен с адресным входом блока памяти, блокирующий выход шифратора соединен с первым входом первого счетчика, выход элемента ИЛИ соединен со вторым входом первого счетчика, первый выход узла сравнения соединен с третьим входом первого счетчика, второй выход узла сравнения соединен с первым входом второго счетчика,

второй вход которого является управляющим входом устройства, второй выход каждого счетчика соединен с соответствующим входом блока памяти, выход блока памяти соединен с входом дешифратора, группа выходов дешифратора является группой выходов устройства, группа входов шифратора - группой запросных входов устройства.

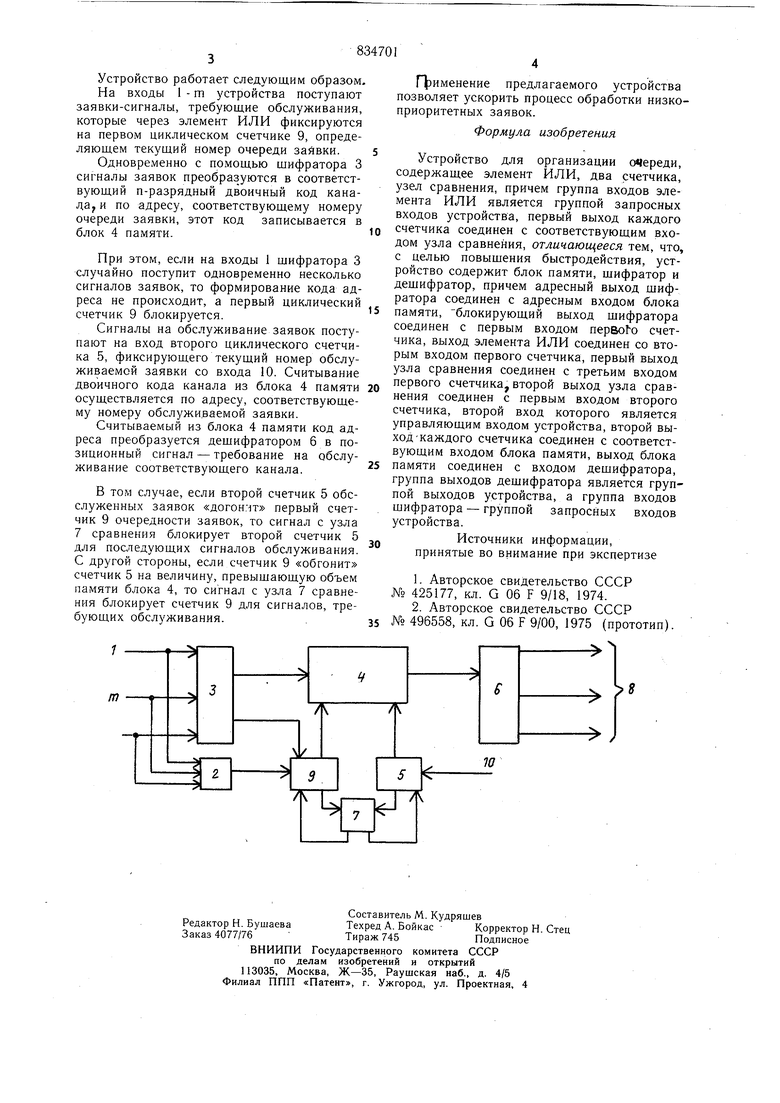

Блок-схема устройства приведена на чертеже.

Устройство содержит запросные входы 1-т устройства, элемент ИЛИ 2, шифратор 3, блок 4 памяти, второй счетчик 5, дешифратор 6, узел 7 сравнения, выходы 8 устройства, первый счетчик 9. Устройство работает следующим образом. На входы 1 - m устройства поступают заявки-сигналы, требующие обслуживания, которые через элемент ИЛИ фиксируются на первом циклическом счетчике 9, определяющем текущий номер очереди заявки. Одновременно с помощью шифратора 3 сигналы заявок преобразуются в соответствующий п-разрядный двоичный код канада,и по адресу, соответствующему номеру очереди заявки, этот код записывается в блок 4 памяти. При этом, если на входы 1 щифратора 3 случайно поступит одновременно несколько сигналов заявок, то формирование кода адреса не происходит, а первый циклический счетчик 9 блокируется. Сигналы на обслуживание заявок поступают на вход второго циклического счетчика 5, фиксирующего текущий номер обслуживаемой заявки со входа 10. Считывание двоичного кода канала из блока 4 памяти осуществляется по адресу, соответствующему номеру обслуживаемой заявки. Считываемый из блока 4 памяти код адреса преобразуется дещифратором б в позиционный сигнал - требование на обслуживание соответствующего канала. В том случае, если второй счетчик 5 обсслуженных заявок «догонит первый счетчик 9 очередности заявок, то сигнал с узла 7 сравнения блокирует второй счетчик 5 для последующих сигналов обслуживания. С другой стороны, если счетчик 9 «обгонит счетчик 5 на величину, превыщающую объем памяти блока 4, то сигнал с узла 7 сравнения блокирует счетчик 9 для сигналов, требующих обслуживания. Г именение предлагаемого устройства позволяет ускорить процесс обработки низкоприоритетных заявок. Формула изобретения Устройство для организации очереди, содержащее элемент ИЛИ, два счетчика, узел сравнения, причем группа входов элемента ИЛИ является группой запросных входов устройства, первый выход каждого счетчика соединен с соответствующим входом узла сравнения, отличающееся тем, что, с целью повыщения быстродействия, устройство содержит блок памяти, щифратор и дешифратор, причем адресный выход шифратора соединен с адресным входом блока памяти, блокирующий выход шифратора соединен с первым входом пep8o o счетчика, выход элемента ИЛИ соединен со вторым входом первого счетчика, первый выход узла сравнения соединен с третьим входом первого счетчика второй выход узла сравнения соединен с первым входом второго счетчика, второй вход которого является управляющим входом устройства, второй выход-каждого счетчика соединен с соответствующим входом блока памяти, выход блока памяти соединен с входом дещифратора, группа выходов дешифратора является группой выходов устройства, а группа входов шифратора - группой запросных входов устройства. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 425177, кл. G 06 F 9/18, 1974. 2.Авторское свидетельство СССР № 496558, кл. G 06 F 9/00, 1975 (прототип).

Авторы

Даты

1981-05-30—Публикация

1979-09-06—Подача