1

(21)4473434/24

(22)12,07.88

(46) 15,01.91. Бюл, N 2

(72) В-В. Голицын, В.П Швырев

и В,Б. Парфенов

(53)681.325(088.8)

(56)Авторское свидетельство СССР № 1126957, кл. G 06 F 9/46, 1984

Центральный процессор ЭВМ типа СМ 1800.2201. Техническое описание и инструкция по -эксплуатации 3 055 , ООЗТО, Си 9,

(54)ЭЛЕКТРОННАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА /ШЯ УСКОРЕННОЙ ОБРАБОТКИ ЗАПРОСОВ ПРЕРЫВАНИЯ

(57)Изобретение относится к вычислительной технике и предназначено для управления в реальном масштабе времени исполнительными органами технологического оборудования с большим количеством источников прерываний Цель изобретения - расширение области применения за счет возможности

обслуживания произвольно о числа источников прерываний, ТВМ содержит операционный бпок, блоки тюгтониной, оперативной и внешней памяти, узел организации цикла прерывании, племент И-НЕ, шифратор, счетчик, in смен г И11, узел Инфмироиания номера страницы иамя 1 и, члемет И, узел захвата, два шинных формирователя, К (К - число источников прерываний) Стоков инициализации прерывании, При обнаружении запроса прерывания OCVIUOCTI-тяечся занесение в (Ьпкгировпнт ю область блока оперативной памяти алреса подпрограммы обглум иания прерывания из блока внешней памяти. Чтение инЛоо- мации из блока внешней памяти производится по адресу, соответс гв 7юшему коду номера источника прерывания Затем микропроцессор переходит в р ежим прерывания, испоиьзуя информацию из Ьиксированной области лока оперативной памяти как адрес подпро-i граммы обслуживания прерывания, 7 ил

&

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с объектами управления | 1986 |

|

SU1401469A1 |

| Устройство для сопряжения датчиков с ЭВМ | 1985 |

|

SU1282108A1 |

| Устройство для управления обменом данными между ЭВМ и абонентами по общей шине | 1988 |

|

SU1543412A1 |

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

| Устройство для сопряжения датчиков с электронной вычислительной машиной | 1984 |

|

SU1208557A2 |

| Устройство для отладки программно-аппаратных блоков | 1985 |

|

SU1315984A1 |

| Система обмена данными в вычислительной сети | 1991 |

|

SU1807493A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1753474A1 |

| Устройство для сопряжения абонентов с каналом связи | 1987 |

|

SU1432537A1 |

Изобретение относится к вычислительной технике и предназначено для управления в реальном масштабе времени исполнительными органами технологического оборудования с большим количеством источников прерываний,

Цепью изобретения является расширение области применения за счет возможности обслуживания произвольного числа источников прерывания.

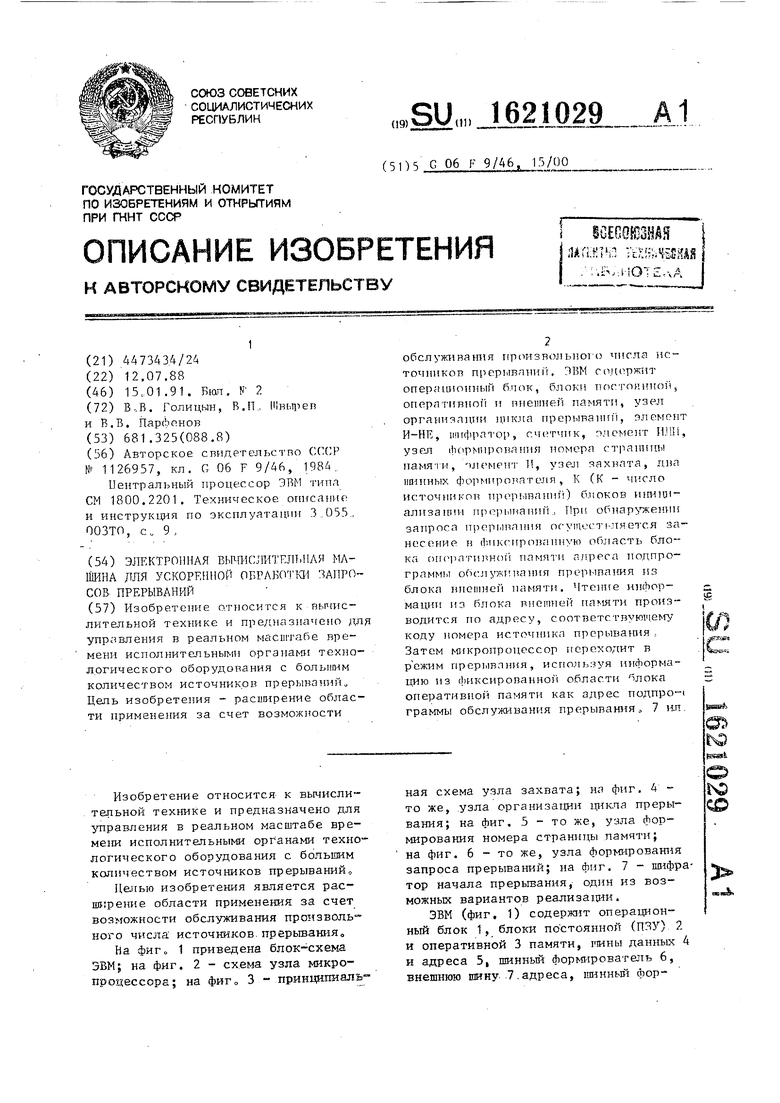

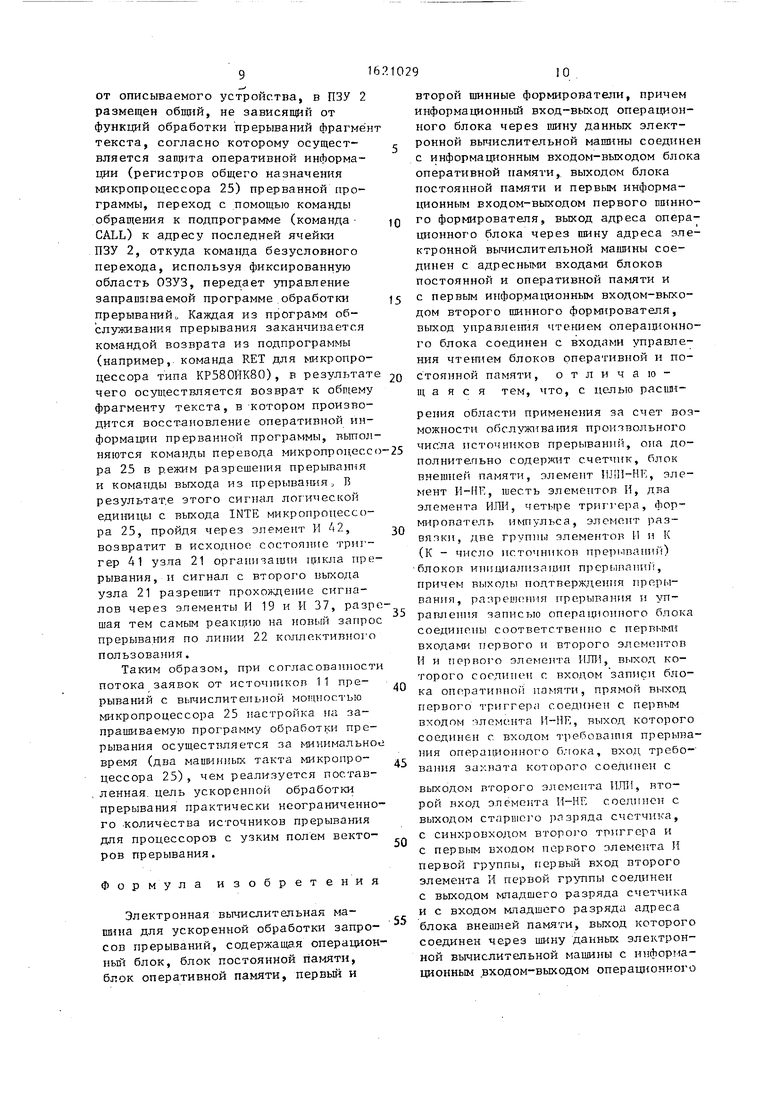

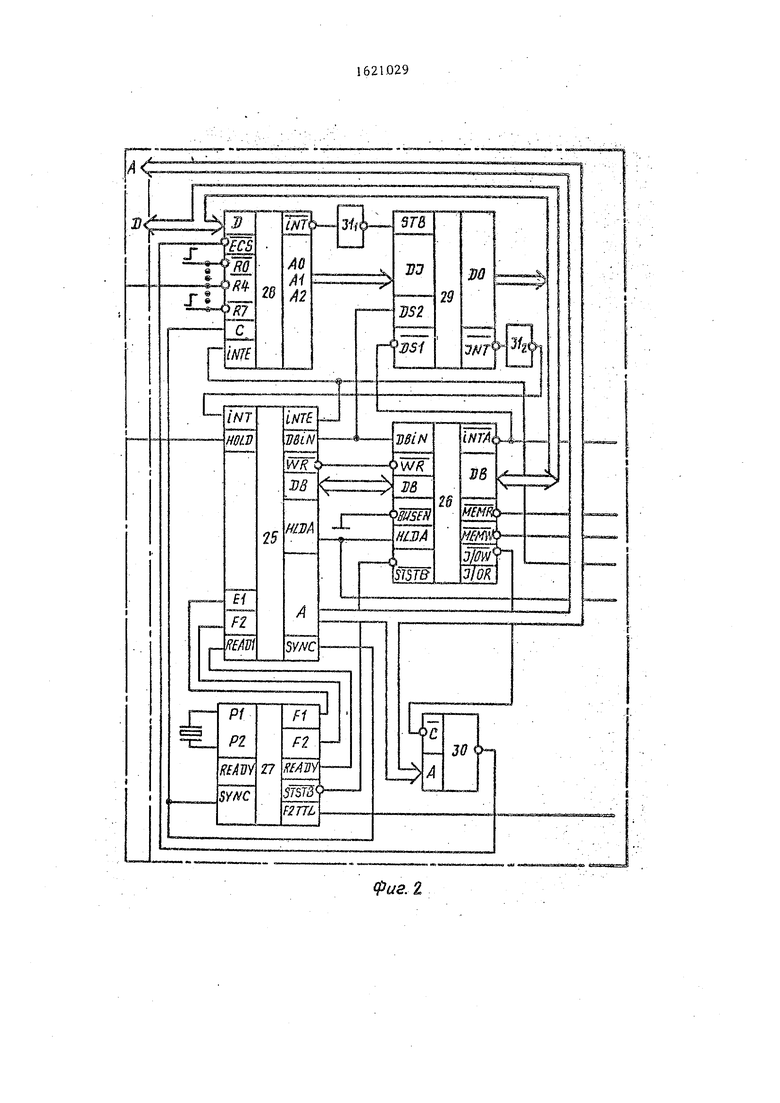

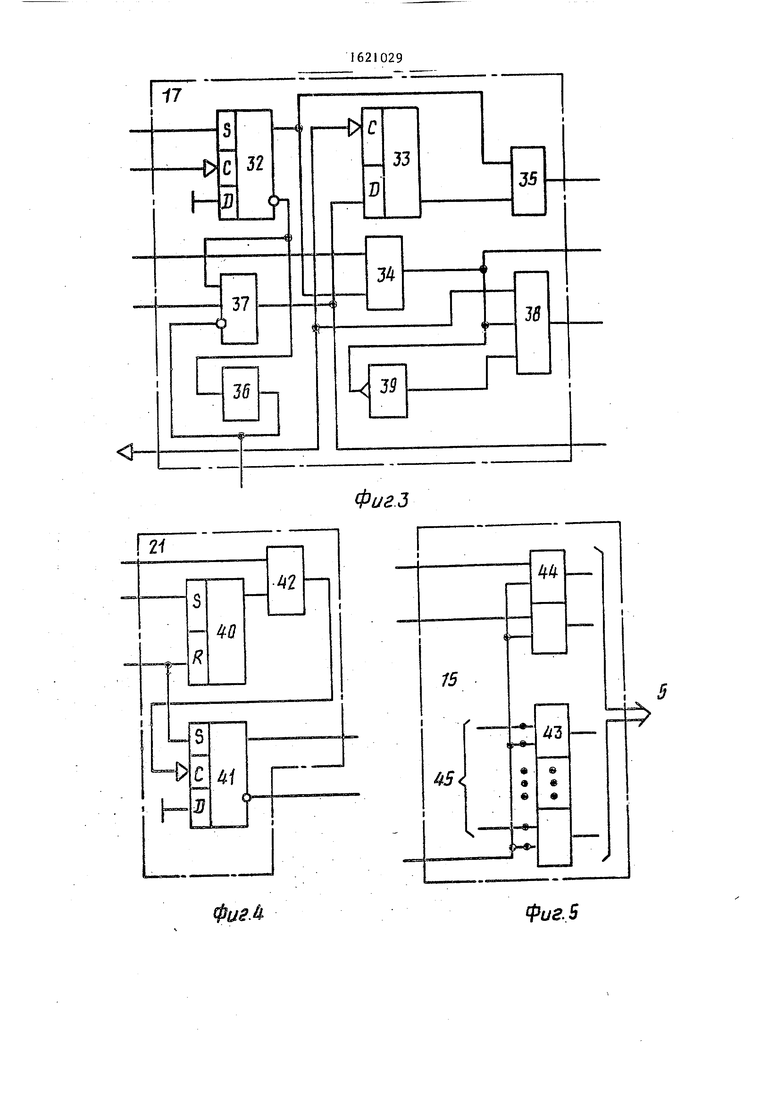

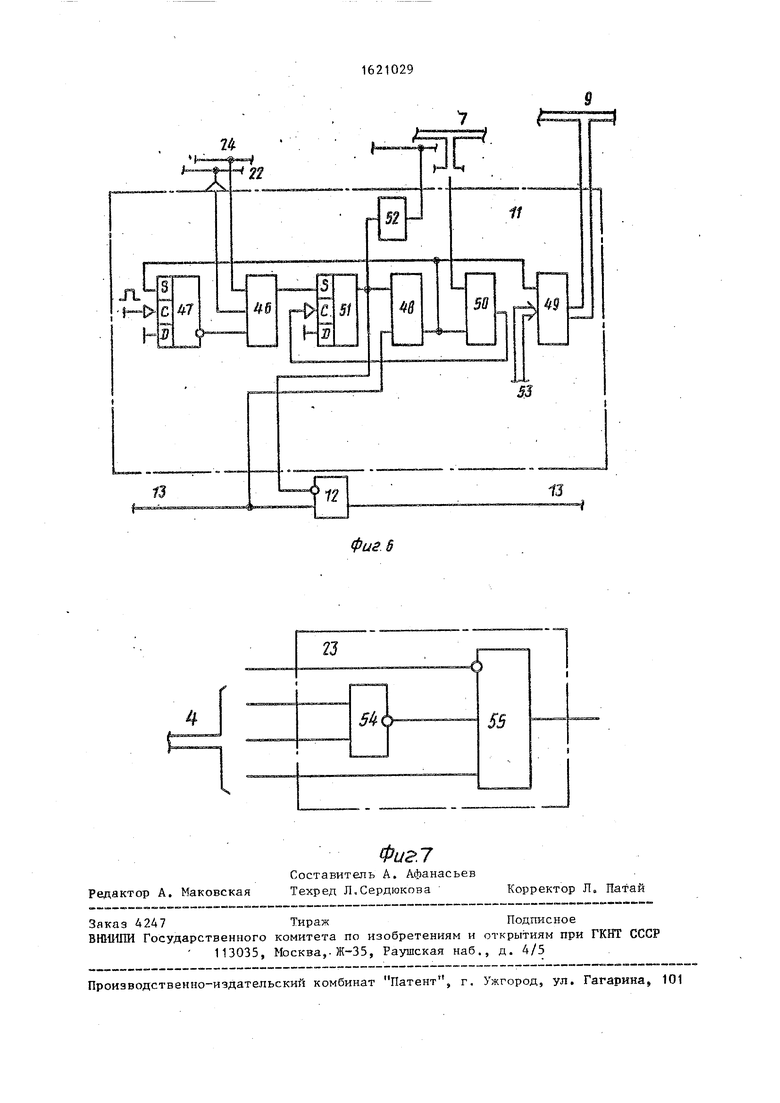

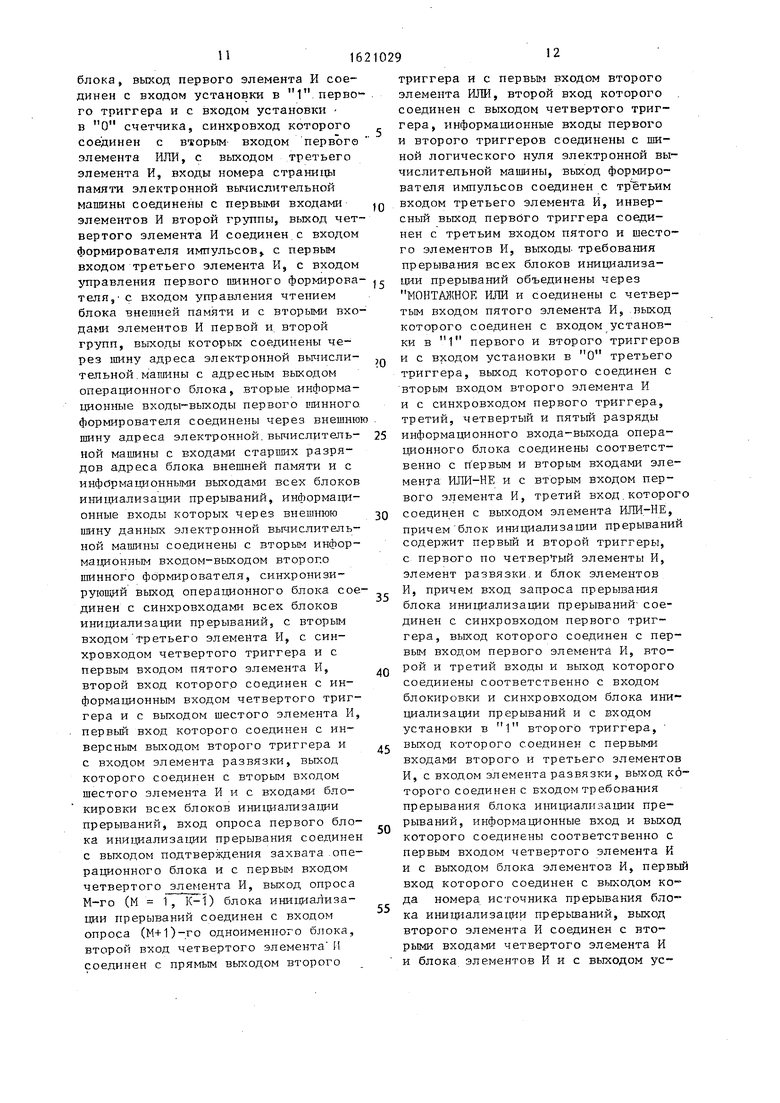

На фиг о 1 приведена блок-схема ЭВМ; на фиг. 2 - схема узла микропроцессора; на фиг о 3 - принципиаль™

ная схема узла захвата; на фиг. 4 - то же, узла организации цикпа прерывания; на фиг, 5 - то же, узла формирования номера страницы памяти; на фиг. 6 - то же, узла формирования запроса прерываний; на фиг. 7 - шифратор начала прерывания, один из возможных вариантов реализации.

ЭВМ (фиг. 1) содержит операционный блок 1, блоки постоянной (ПЗУ) 2 и оперативной 3 памяти, пины данных 4 и адреса 5, шинный формирователь 6, внешнюю шину 7 адреса, шинный форьз

мирователь 8, кяеюнюю шину 9 данных, блоки tO инициализации прерывания, узел 11 формирования запросов прерываний, элемент И 12,. шину 13 под-г тве рждения захвата, блок 14 внешней памяти (ПЗУ), узел Сформирования номера страницы памяти, счетчик 16, узел 17 захвата, элемент ИЛИ 18, элемент И 19, элемент И-НЕ 20, узел ю

21организации цикла прерываний, шину

22синхронизации, шифратор 23, шину 24 захвата.

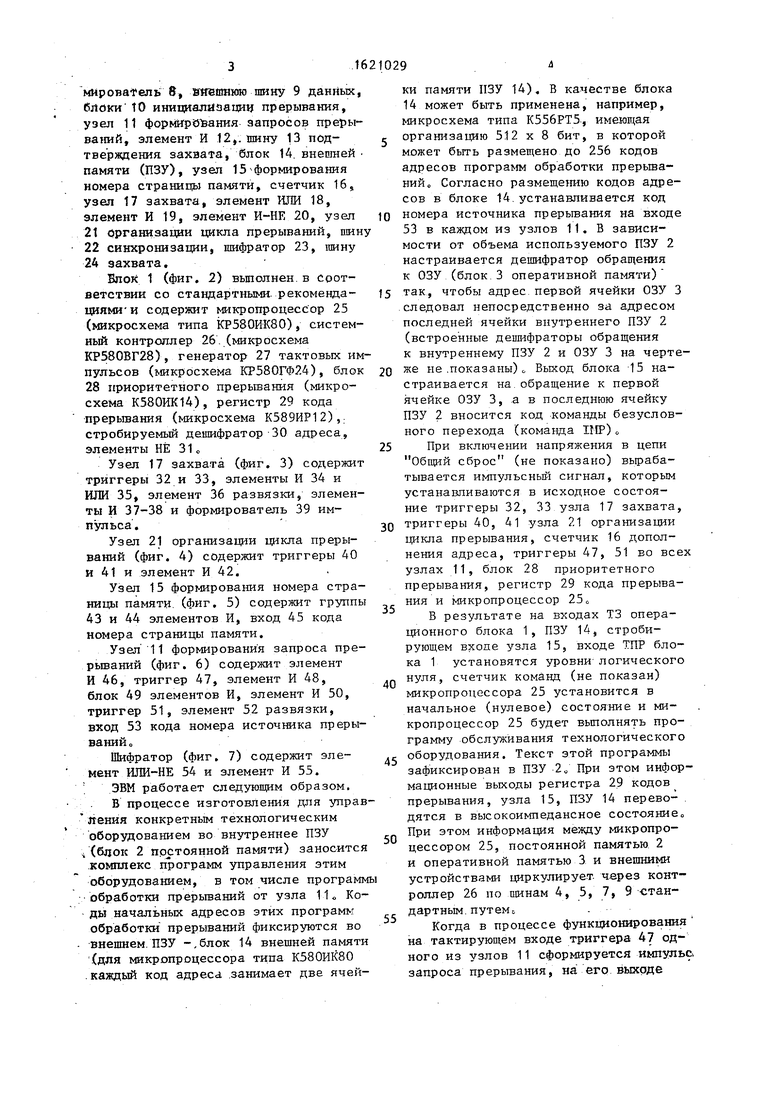

Блок 1 (фиг. 2) выполнен в соответствии со стандартными рекоменда- 15 циями И содержит микропроцессор 25 (микросхема типа КР580ИК80), системный контроллер 26 (микросхема КР580ВГ28), генератор 27 тактовых импульсов (микросхема КР580ГФ24), блок 20 28 приоритетного прерывания (микросхема К580ИК14), регистр 29 кода прерывания (микросхема К589ИР12), стробируемый дешифратор 30 адреса, элементы НЕ 31025

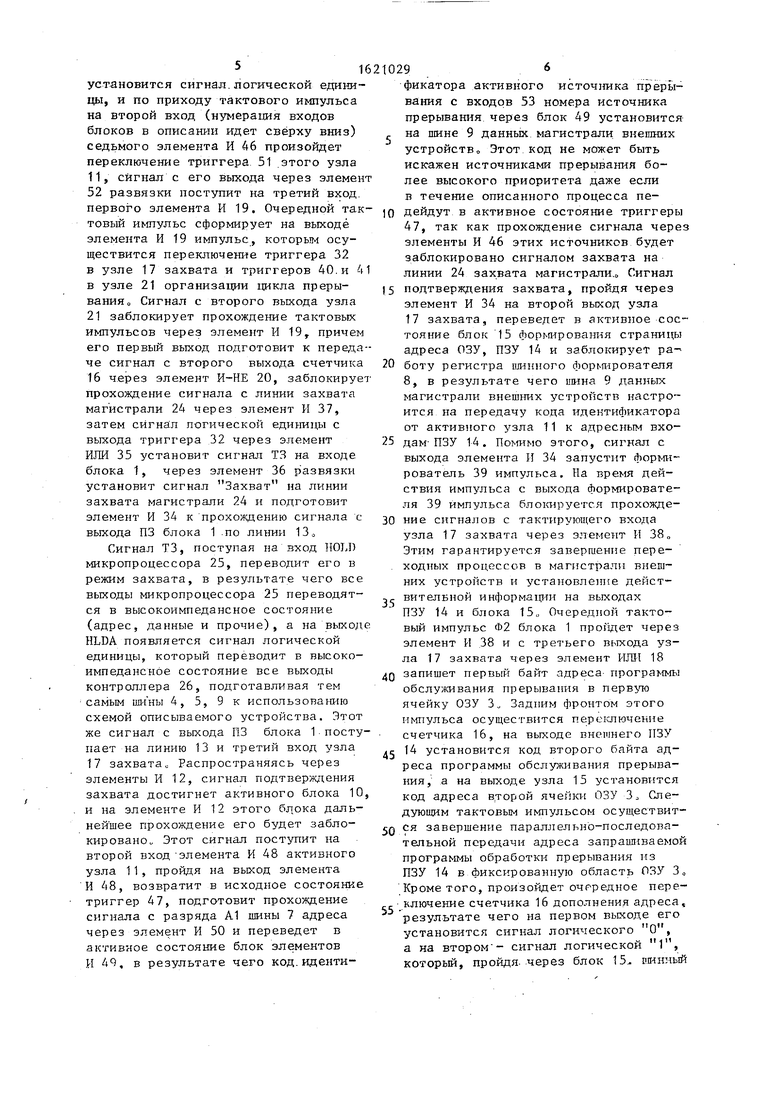

Узел 17 захвата (фиг. 3) содержит триггеры 32 и 33, элементы И 34 и ИЛИ 35, элемент 36 развязки, элементы И 37-38 и формирователь 39 импульса. зо

Узел 21 организации цикла прерываний (фиг. 4) содержит триггеры 40 и 41 и элемент И 42.

Узел 15 формирования номера страницы памяти (фиг, 5) содержит группы 43 и 44 элементов И, вход 45 кода номера страницы памяти.

Узел 11 формирования запроса прерываний (фиг. 6) содержит элемент И 46, триггер 47, элемент И 48,.„

блок 49 элементов И, элемент И 50, триггер 51, элемент 52 развязки, вход 53 кода номера источника прерываний,.

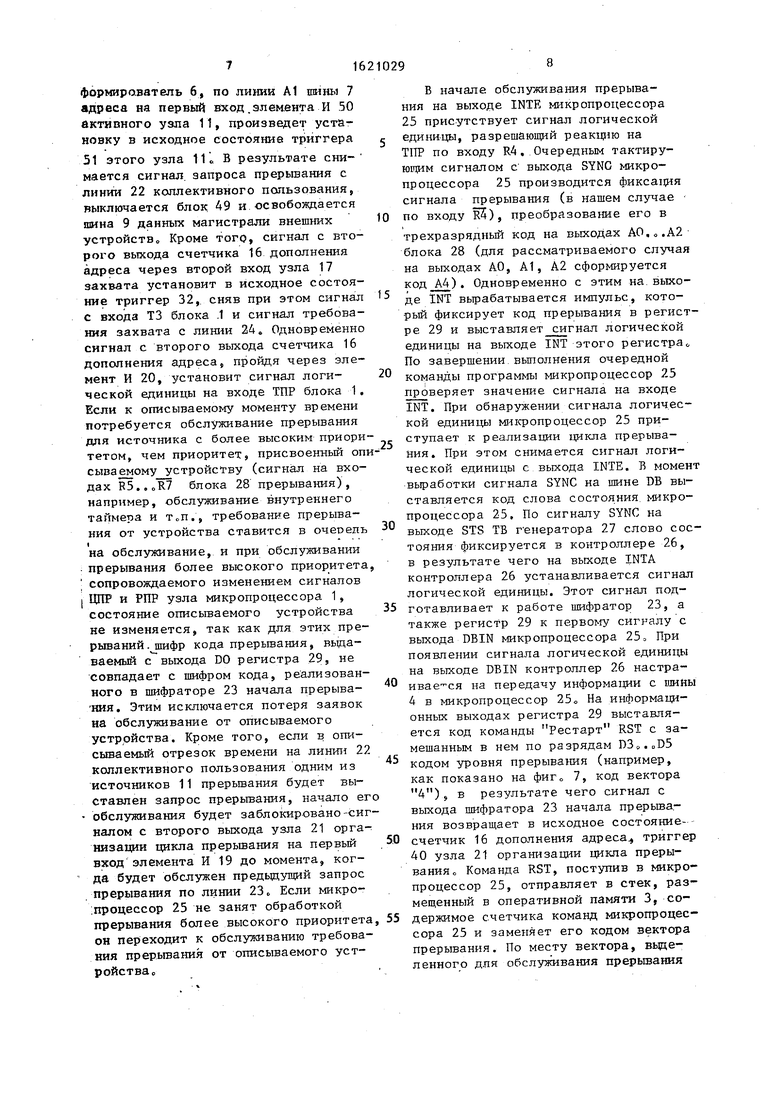

Шифратор (фиг. 7) содержит элемент ИЛИ-НЕ 54 и элемент И 55.

ЭВМ работает следующим образом.

В процессе изготовления для управ- ления конкретным технологическим оборудованием во внутреннее ПЗУ5Q

(блок 2 постоянной памяти) заносится комплекс программ управления этим оборудованием, в том числе программы обработки прерываний от узла 11 , Коды начальных адресов этих программ обработки прерываний фиксируются во внешнем ПЗУ -,блок 14 внешней памяти (для микропроцессора типа К580ИК80 каждый код адреса занимает две ячей35

45

55

5 0 5

о

„

Q

5

5

5

ки памяти ПЗУ 14). В качестве блока 14 может быть применена, например,

микросхема типа К556РТ5, имеющая организацию 512 х 8 бит, в которой может быть размещено до 256 кодов адресов программ обработки прерыва- ний0 Согласно размещению кодов адресов в блоке 14 устанавливается код номера источника прерывания на входе 53 в каждом из узлов 11. В зависимости от объема используемого ПЗУ 2 настраивается дешифратор обращения к ОЗУ (блок 3 оперативной памяти) так, чтобы адрес первой ячейки ОЗУ 3 следовал непосредственно за адресом последней ячейки внутреннего ПЗУ 2 (встроенные дешифраторы обращения к внутреннему ПЗУ 2 и ОЗУ 3 на чертеже не показаны)о Выход блока 15 настраивается на обращение к первой ячейке ОЗУ 3, а в последнюю ячейку ПЗУ 2 вносится код команды безусловного перехода (команда ItIP) 0

При включении напряжения в цепи Общий сброс (не показано) вырабатывается импульсный сигнал, которым устанавливаются в исходное состояние триггеры 32, 33 узла 17 захвата, триггеры 40, 41 узла 21 организации цикла прерывания, счетчик 16 дополнения адреса, триггеры 47, 51 во всех узлах 11, блок 28 приоритетного прерывания, регистр 29 кода прерывания и микропроцессор 250

В результате на входах ТЗ операционного блока 1, ПЗУ 14, строби- рующем входе узла 15, входе ТПР блока 1 установятся уровни логического нуля, счетчик команд (не показан) микропроцессора 25 установится в начальное (нулевое) состояние и микропроцессор 25 будет выполнять программу обслуживания технологического оборудования. Текст этой программы зафиксирован в ПЗУ 2U При этом информационные выходы регистра 29 кодов прерывания, узла 15, ПЗУ 14 переводятся в высокоимпедансное состояние,, При этом информация между микропроцессором 25, постоянной памятью 2 и оперативной памятью 3 и внешними устройствами циркулирует через контроллер 26 по щинам 4, 5, 7, 9 стандартным путемс

Когда в процессе функционирования на тактирующем входе триггера 47 одного из узлов 11 сформируется импульс, запроса прерывания, на его выходе

установится сигнал логической единицы, и по приходу тактового импульса на второй вход (нумерация входов блоков в описании идет сверху вниз) седьмого элемента И 46 произойдет переключение триггера 51 этого узла 11, сигнал с его выхода через элемент 52 развязки поступит на третий вход

фикатора активного источника прерывания с входов 53 номера источника прерывания через блок 49 установится на шине 9 данных магистрали внешних устройство Этот код не может быть искажен источниками прерывания более высокого приоритета даже если в течение описанного процесса пепервого элемента И 19. Очередной так- 0 дейдут в активное состояние триггеры товый импульс сформирует на выходе 47, так как прохождение сигнала через элемента И 19 импульс, которым осу- элементы И 46 этих источников будет

заблокировано сигналом захвата на линии 24 захвата магистрали а Сигнал 15 подтверждения захвата, пройдя через элемент И 34 на второй выход узла

ществится переключение триггера 32 в узле 17 захвата и триггеров 40 и 41 в узле 21 организации цикла прерывания 0 Сигнал с второго выхода узла 21 заблокирует прохождение тактовых импульсов через элемент И 19, причем его первый выход подготовит к передаче сигнал с второго выхода счетчика

16через элемент И-НЕ 20, заблокирует прохождение сигнала с линии захвата магистрали 24 через элемент И 37, затем сигнал логической единицы с выхода триггера 32 через элемент

ИЛИ 35 установит сигнал ТЗ на входе блока 1, через элемент 36 развязки установит сигнал Захват на линии захвата магистрали 24 и подготовит элемент И 34 к прохождению сигнала с выхода ПЗ блока 1 по линии 13„

Сигнал ТЗ, поступая на вход HOLD микропроцессора 25, переводит его в режим захвата, в результате чего все выходы микропроцессора 25 переводятся в высокоимпедансное состояние (адрес, данные и прочие), а на выходе HLDA появляется сигнал логической единицы, который переводит в высокоимпедансное состояние все выходы контроллера 26, подготавливая тем самым шины 4, 5, 9 к использованию схемой описываемого устройства. Этот же сигнал с выхода ПЗ блока 1 поступает на линию 13 и третий вход узла

17захвата,. Распространяясь через элементы И 12, сигнал подтверждения захвата достигнет активного блока 10, и на элементе И 12 этого бл.ока дальнейшее прохождение его будет заблокировано „ Этот сигнал поступит на второй вход элемента И 48 активного узла 11, пройдя на выход элемента

И 48, возвратит в исходное состояние триггер 47, подготовит прохождение сигнала с разряда А1 шины 7 адреса через элемент И 50 и переведет в активное состояние блок элементов И 49, в результате чего код иденти17 захвата, переведет в активное состояние блок 15 формирования страницы адреса ОЗУ, ПЗУ 14 и заблокирует ра-

20 боту регистра шинного формирователя 8, в результате чего шина 9 данных магистрали внешних устройств настроится на передачу кода идентификатора от активного узла 11 к адресным вхо25 дам ПЗУ 14. Помимо этого, сигнал с выхода элемента И 34 запустит формирователь 39 импульса. На время действия импульса с выхода Формирователя 39 импульса блокируется прохожде30 ние сигналов с тактирующего входа узла 17 захвата через элемент И 38„ Этим гарантируется завершение переходных процессов в магистрали внешних устройств и установление дейст с вителъной информации на выходах

ПЗУ 14 и блока 15„ Очередной тактовый импульс Ф2 блока 1 пройдет через элемент И 38 и с третьего выхода узла 17 захвата через элемент ИЛИ 18

4Q запишет первый байт адреса программы обслуживания прерывания в первую ячейку ОЗУ 30 Задним фронтом этого импульса осуществится переключение счетчика 16, на выходе внешнего ПЗУ 14 установится код второго байта адреса программы обслуживания прерывания, а на выходе узла 15 установится код адреса второй ячейки ОЗУ 3 Следующим тактовым импульсом осуществитзд ся завершение параллельно-последовательной передачи адреса запрашиваемой программы обработки прерывания из ПЗУ 14 в фиксированную область ОЗУ 3„ Кроме того, произойдет очередное переключение счетчика 16 дополнения адреса,

45

55

результате чего на первом выходе его установится сигнал логического О, а на втором - сигнал логической Г1, который, пройдя через блок 15.- шинный

фикатора активного источника прерывания с входов 53 номера источника прерывания через блок 49 установится на шине 9 данных магистрали внешних устройство Этот код не может быть искажен источниками прерывания более высокого приоритета даже если в течение описанного процесса педейдут в активное состояние триггеры 47, так как прохождение сигнала чере элементы И 46 этих источников будет

17 захвата, переведет в активное состояние блок 15 формирования страницы адреса ОЗУ, ПЗУ 14 и заблокирует ра-

боту регистра шинного формирователя 8, в результате чего шина 9 данных магистрали внешних устройств настроится на передачу кода идентификатора от активного узла 11 к адресным входам ПЗУ 14. Помимо этого, сигнал с выхода элемента И 34 запустит формирователь 39 импульса. На время действия импульса с выхода Формирователя 39 импульса блокируется прохождение сигналов с тактирующего входа узла 17 захвата через элемент И 38„ Этим гарантируется завершение переходных процессов в магистрали внешних устройств и установление действителъной информации на выходах

ПЗУ 14 и блока 15„ Очередной тактовый импульс Ф2 блока 1 пройдет через элемент И 38 и с третьего выхода узла 17 захвата через элемент ИЛИ 18

запишет первый байт адреса программы обслуживания прерывания в первую ячейку ОЗУ 30 Задним фронтом этого импульса осуществится переключение счетчика 16, на выходе внешнего ПЗУ 14 установится код второго байта адреса программы обслуживания прерывания, а на выходе узла 15 установится код адреса второй ячейки ОЗУ 3 Следующим тактовым импульсом осуществится завершение параллельно-последовательной передачи адреса запрашиваемой программы обработки прерывания из ПЗУ 14 в фиксированную область ОЗУ 3„ Кроме того, произойдет очередное переключение счетчика 16 дополнения адреса,

результате чего на первом выходе его установится сигнал логического О, а на втором - сигнал логической Г1, который, пройдя через блок 15.- шинный

формирователь 6, по пинии А1 шины 7 адреса на первый вход.элемента И 50 активного узла 11, произведет установку в исходное состояние триггера

51 этого узла 111 В результате снимается сигнал запроса прерывания с линии 22 коллективного пользования, выключается блок 49 и освобождается шина 9 данных магистрали внешних устройств Кроме того, сигнал с второго выхода счетчика 16 дополнения адреса через второй вход узла 17 захвата установит в исходное состояние триггер 32, сняв при этом сигнал с входа ТЗ блока 1 и сигнал требования захвата с линии 24. Одновременно сигнал с второго выхода счетчика 16 дополнения адреса, пройдя через элемент И 20, установит сигнал логической единицы на входе ТПР блока 1. Если к описываемому моменту времени потребуется обслуживание прерывания для источника с более высоким приоритетом, чем приоритет, присвоенный опсываемому устройству (сигнал на входах R5.,R7 блока 28 прерывания), например, обслуживание внутреннего таймера и ., требование прерывания от устройства ставится в очеоепъ i на обслуживание, и при обслуживании

прерывания более высокого приоритета сопровождаемого изменением сигналов ЦПР и РПР узла микропроцессора 1, состояние описываемого устройства не изменяется, так как для этих прерываний .пифр кода прерывания, выдаваемый с выхода DO регистра 29, не совпадает с шифром кода, реализованного в шифраторе 23 начала прерывания. Этим исключается потеря заявок на обслуживание от описываемого устройства. Кроме того, если в описываемый отрезок времени на линии 22 коллективного пользования одним из источников 11 прерывания будет выставлен запрос прерывания, начало ег обслуживания будет заблокировано сигналом с второго выхода узла 21 организации цикла прерывания на первый вход элемента И 19 до момента, когда будет обслужен предыдущий запрос прерывания по линии 23 Если микропроцессор 25 не занят обработкой прерывания более высокого приоритета он переходит к обслуживанию требования прерывания от описываемого устройства о

0

5

5

5

0

5

0

5

0

В начале обслуживания прерывания на выходе INTR микропроцессора 25 присутствует сигнал логической единицы, разрешающий реакцию на ТПР по входу R4. Очередным тактирующим сигналом с выхода SYNC микропроцессора 25 производится фиксация сигнала прерывания (в нашем случае по входу R4), преобразование его в

трехразрядный код на выходах АО,0.А2 блока 28 (для рассматриваемого случая на выходах АО, А1, А2 сформируется код А4). Одновременно с этим на выходе INT вырабатывается импульс, который фиксирует код прерывания в регистре 29 и выставляет сигнал логической единицы на выходе INT этого регистра„ По завершении выполнения очередной команды программы микропроцессор 25 проверяет значение сигнала на входе INT. При обнаружении сигнала логической единицы микропроцессор 25 приступает к реализации цикла прерывания. При этом снимается сигнал логической единицы с выхода INTE. В момент выработки сигнала SYNC на шине DB выставляется код слова состояния микропроцессора 25, По сигналу SYNC на выходе STS ТВ генератора 27 слово состояния фиксируется в контроллере 26, в результате чего на выходе INTA контроллера 26 устанавливается сигнал логической единицы. Этот сигнал подготавливает к работе шифратор 23, а также регистр 29 к первому сигналу с выхода DBIN микропроцессора 25, При появлении сигнала логической единицы на выходе DBIN контроллер 26 настра- ивае- ся на передачу информации с шины 4 в микропроцессор 25„ На информационных выходах регистра 29 выставляется код команды Рестарт RST с замешанным в нем по разрядам D30.0D5 кодом уровня прерывания (например, как показано на фиг0 7, код вектора 4), в результате чего сигнал с выхода шифратора 23 начала прерывания возвращает в исходное состояние- счетчик 16 дополнения адреса., триггер 40 узла 21 организации цикла прерывания Команда RST, поступив в микропроцессор 25, отправляет в стек, размещенный в оперативной памяти 3, содержимое счетчика команд микропроцессора 25 и заменяет его кодом вектора прерывания. По месту вектора, выделенного дпя обслуживания прерывания

от описываемого устройства, в ПЗУ 2 размещен общий, не зависящий от функций обработки прерываний фрагме текста, согласно которому осуществляется защита оперативной информации (регистров общего назначения микропроцессора 25) прерванной программы, переход с помощью команды обращения к подпрограмме (команда CALL) к адресу последней ячейки ПЗУ 2, откуда команда безусловного перехода, используя фиксированную область ОЗУЗ, передает управление запрашиваемой программе обработки прерываний„ Каждая из программ обслуживания прерывания заканчивается командой возврата из подпрограммы (например, команда RET для микропроцессора типа КР580ИК80), в результате 2о стоянкой памяти, отличаю 30

чего осуществляется возврат к общему фрагменту текста, в котором производится восстановление оперативной информации прерванной программы, выполняются команды перевода микропроцессо-25 ра 25 в режим разрешения прерывания и команды выхода из прерывания, В результате этого сигнал логической единицы с выхода INTE микропроцессора 25, пройдя через элемент И 42, возвратит в исходное состояние триггер 41 узпа 21 организации цикла прерывания, и сигнал с второго выхода узла 21 разрешит прохождение сигналов через элементы И 19 и И 37, разрешая тем самым реакцию на новый запрос прерывания по линии 22 коллективного пользования.

Таким образом, при согласованности потока заявок от источников 11 прерываний с вычислительной мощностью микропроцессора 25 настройка на запрашиваемую программу обработки прерывания осуществляется за минимальное время (два машинных такта микропроцессора 25), чем реализуется поставленная цель ускоренной обработки прерывания практически неограниченного количества источников прерывания для процессоров с узким полем векторов прерывания.

35

40

45

50

щ а я с я тем, что, с целью расши рения области применения за счет в можности обслуживания произвольног числа источников прерываний, она д полнитепьно содержит счетчик, блок внешней памяти, элемент 1ШП-НК, эл мент И-НК, шесть элементов И, два элемента ИЛИ, четыре триггера, фор мирователь импульса, элемент раз- втки, две группы элементов И и К (К - число источников прерываний) блоков инициализации прсрЕ.шашш, причем выходы подтверждения прерывания, разрешения прерывания и управления записью операционного бло соединены соответственно с первыми входами первого и второго элементо И и первого элемента ИЛИ, выход ко торого соединен с входом записи бл ка оперативной памяти, прямой выхо первого триггера соединен с первым входом элемента И-НЕ, выход которо соединен с входом требования преры ния операционного блока, вход треб вания захвата которого соединен с

выходом второго элемента ИЛИ, второй вход элемента И-НЕ соединен с выходом старшего разряда счетчика, с синхрОБХОДОМ второго триггера и с первым входом первого элемента И первой группы, первый вход второго элемента И первой группы соединен с выходом младшего разряда счетчик и с входом младшего разряда адреса блока внешней памяти, выход которо соединен через шину данных электро ной вычислительной машины с информа ционным входом-выходом операционног

Формула изобретения

Электронная вычислительная машина для ускоренной обработки запросов прерываний, содержащая операционный блок, блок постоянной памяти, блок оперативной памяти, первый и

второй шинные формирователи, причем информационный вход-выход операционного блока через шину данных элект- ронной вычислительной машины соединен с информационным входом-выходом блока оперативной памяти, выходом блока постоянной памяти и первым информационным входом-выходом первого шинного формирователя, выход адреса операционного блока через шину адреса электронной вычислительной машины соединен с адресными входами блоков постоянной и оперативной памяти и

с первым информационным входом-выходом второго шинного формирователя, выход управления чтением операционного блока соединен с входами управления чтением блоков оперативной и по0

5

5

0

5

0

5

щ а я с я тем, что, с целью расширения области применения за счет возможности обслуживания произвольного числа источников прерываний, она до- полнитепьно содержит счетчик, блок внешней памяти, элемент 1ШП-НК, элемент И-НК, шесть элементов И, два элемента ИЛИ, четыре триггера, формирователь импульса, элемент раз- втки, две группы элементов И и К (К - число источников прерываний) блоков инициализации прсрЕ.шашш, причем выходы подтверждения прерывания, разрешения прерывания и управления записью операционного блока соединены соответственно с первыми входами первого и второго элементов И и первого элемента ИЛИ, выход которого соединен с входом записи блока оперативной памяти, прямой выход первого триггера соединен с первым входом элемента И-НЕ, выход которого соединен с входом требования прерывания операционного блока, вход требования захвата которого соединен с

выходом второго элемента ИЛИ, второй вход элемента И-НЕ соединен с выходом старшего разряда счетчика, с синхрОБХОДОМ второго триггера и с первым входом первого элемента И первой группы, первый вход второго элемента И первой группы соединен с выходом младшего разряда счетчика и с входом младшего разряда адреса блока внешней памяти, выход которого соединен через шину данных электронной вычислительной машины с информационным входом-выходом операционного

111621029

блока, выход первого элемента И соединен с входом установки в 1 первого триггера и с входом установки в О счетчика, синхровход которого соединен с вторым входом первого элемента ИЛИ, с выходом третьего

элемента И, входы номера страницы памяти электронной вычислительной машины соединены с первыми входами элементов И второй группы, выход четвертого элемента И соединен с входом формирователя импульсов, с первым входом третьего элемента И, с входом

управления первого шинного формирова- ции прерываний объединены через

МОНТАЖНОЕ ИЛИ и соединены с чет тым входом пятого элемента И, вы которого соединен с входом устан ки в 1 первого и второго тригг и с входом установки в О треть триггера, выход которого соедине вторым входом второго элемента И и с синхровходом первого триггер третий, четвертый и пятый разряд информационного входа-выхода опе ционного блока соединены соответ венно с первым и вторым входами мента ИЛИ-НЕ и с вторым входом п вого элемента И, третий вход кот соединен с выходом элемента ИЛИпричем блок инициализации прерыв содержит первый и второй триггер с первого по четвертый элементы элемент развязки и блок элементо И, причем вход запроса прерывани блока инициализации прерываний с динен с синхровходом первого три гера, выход которого соединен с вым входом первого элемента И, в рой и третий входы и выход котор соединены соответственно с входо блокировки и синхровходом блока циализации прерываний и с входом установки в 1 второго триггера выход которого соединен с первым входами второго и третьего элеме И, с входом элемента развязки, выхо торого соединен с входом требовани прерывания блока инициализации п рываний, информационные вход и в которого соединены соответственн первым входом четвертого элемент и с выходом блока элементов И, п вход которого соединен с выходом да номера источника прерывания ка инициализации прерываний, вых второго элемента И соединен с вт рыми входами четвертого элемента и блока элементов И и с выходом

теля, с входом управления чтением блока внешней памяти и с вторыми входами элементов И первой и второй групп, выходы которых соединены через шину адреса электронной вычислительной машины с адресным выходом операционного блока, вторые информационные входы-выходы первого шинного формирователя соединены через внешню шину адреса электронной вычислительной машины с входами старших разрядов адреса блока внешней памяти и с информационными выходами всех блоков инициализации прерываний, информационные входы которых через внешнюю шину данных электронной вычислительной машины соединены с вторым информационным входом-выходом второго шинного формирователя, синхронизирующий выход операционного блока соединен с синхровходами всех блоков инициализации прерываний, с вторым входом третьего элемента И, с син- хровходом четвертого триггера и с первым входом пятого элемента И, второй вход которого соединен с информационным входом четвертого триггера и с выходом шестого элемента И, первый вход которого соединен с инверсным выходом второго триггера и с входом элемента развязки, выход которого соединен с вторым входом шестого элемента И и с входами блокировки всех блоков инициализации прерываний, вход опроса первого блока инициализации прерывания соединен с выходом подтверждения захвата операционного блока и с первым входом четвертого элемента И, выход опроса М-го (М 1, К-1) блока инициализации прерываний соединен с входом опроса (М+1)-го одноименного блока, второй вход четвертого элемента И соединен с прямым выходом второго

12

триггера и с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом четвертого триггера, информационные входы первого и второго триггеров соединены с шиной логического нуля электронной вычислительной машины, выход формирователя импульсов соединен с третьим входом третьего элемента И, инверсный выход первого триггера соединен с третьим входом пятого и шестого элементов И, выходы требования прерывания всех блоков инициализации прерываний объединены через

5

0

5

0

5

0

5

МОНТАЖНОЕ ИЛИ и соединены с четвертым входом пятого элемента И, выход которого соединен с входом установки в 1 первого и второго триггеров и с входом установки в О третьего триггера, выход которого соединен с вторым входом второго элемента И и с синхровходом первого триггера, третий, четвертый и пятый разряды информационного входа-выхода операционного блока соединены соответственно с первым и вторым входами элемента ИЛИ-НЕ и с вторым входом первого элемента И, третий вход которого соединен с выходом элемента ИЛИНЕ, причем блок инициализации прерываний содержит первый и второй триггеры, с первого по четвертый элементы И, элемент развязки и блок элементов И, причем вход запроса прерывания блока инициализации прерываний соединен с синхровходом первого триггера, выход которого соединен с первым входом первого элемента И, второй и третий входы и выход которого соединены соответственно с входом блокировки и синхровходом блока инициализации прерываний и с входом установки в 1 второго триггера, выход которого соединен с первыми входами второго и третьего элементов И, с входом элемента развязки, выход которого соединен с входом требования прерывания блока инициализации прерываний, информационные вход и выход которого соединены соответственно с первым входом четвертого элемента И и с выходом блока элементов И, первый вход которого соединен с выходом кода номера источника прерывания блока инициализации прерываний, выход второго элемента И соединен с вторыми входами четвертого элемента И и блока элементов И и с выходом установки в 1 первого триггера, выход четвертого элемента И соединен с синхровходом второго триггера, вход опроса блока инициализации прерываний соединен с вторыми входами второго и третьего элементов И, выход третьего элемента И соединен с выходом опроса блока инициализации прерываний, шина логического нуля которого соединена с информационными входами первого и второго триггеров

Ч}0Ј

Ё

-гпш

сш

eeotzgi

I1

ч

Д.

НЛ

32

37

LJ

42

С

H

j

33

D

35

38

Фиг.З

44

15

, S

45

«

fu8.5

23

4

Редактор А. Маковская

Составитель А. Афанасьев Техред Л,Сердюкова

Фиг §

i

5kb

55

Фиг

Корректор Л, Патай

Авторы

Даты

1991-01-15—Публикация

1988-07-12—Подача