(54) ЛОГАРИФМИЧЕСКИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Логарифмический аналого-цифровой преобразователь | 1977 |

|

SU752370A1 |

| Логарифмический преобразователь | 1983 |

|

SU1167625A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2007 |

|

RU2359403C1 |

| Логарифмический аналого-цифровой преобразователь | 1982 |

|

SU1101848A1 |

| ФУНКЦИОНАЛЬНЫЙ АНАЛОГОВО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2013 |

|

RU2549114C2 |

| Логарифмический аналого-цифровой преобразователь | 1990 |

|

SU1725397A1 |

| СПОСОБ ДВУХТАКТНОГО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ ИНТЕГРИРУЮЩЕГО ТИПА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2014 |

|

RU2564909C1 |

| Устройство для определения логарифма отношения двух напряжений | 1982 |

|

SU1103249A1 |

| Логарифмический аналого-цифровой преобразователь | 1982 |

|

SU1042036A1 |

| СОСТАВНОЙ БЫСТРОДЕЙСТВУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2006 |

|

RU2311731C1 |

1

Изобретение относится к преобразователям электрических сигналов по логарифмическому закону и может быть использовано в аналоговых вычислительных машинах.

Известно устройство, предназначенное для логарифмического аналогоцифрового преобразования сигналов, содержащее генератор экспоненциального напряжения-, компаратор, триггер и схему цифрового преобразования С1

Это устройство обладает низкой точностью преобразования сигналов.

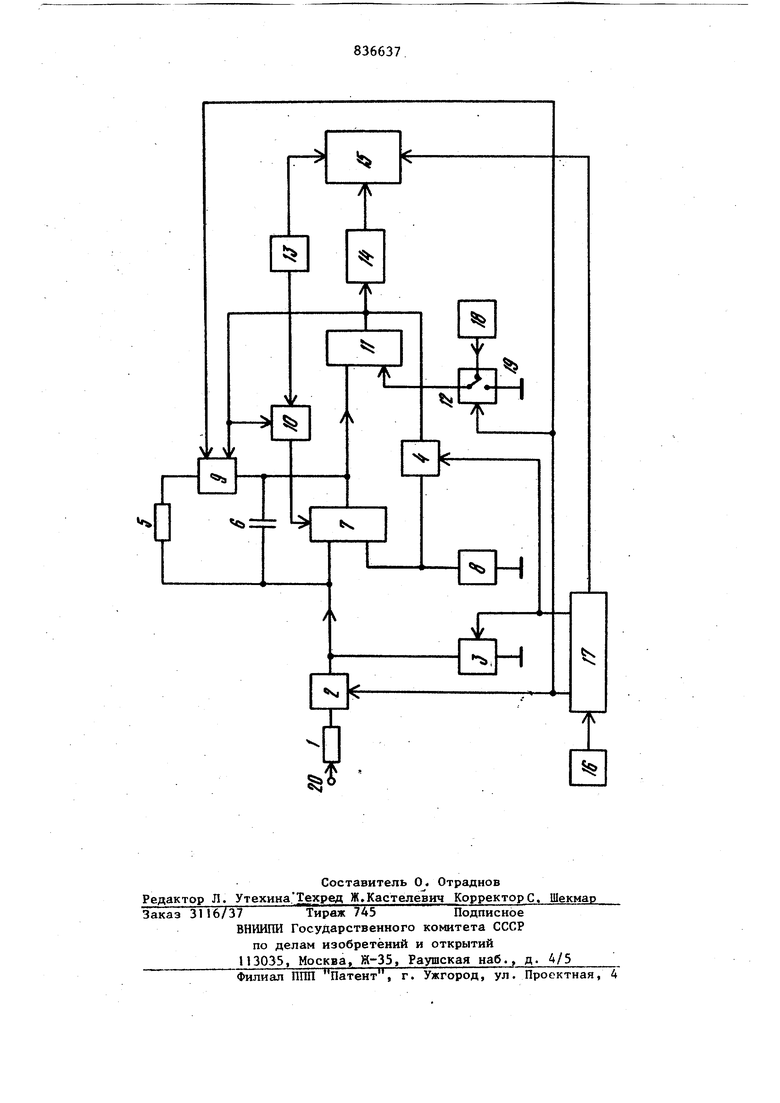

Из известных устройств аналогичного назначения наиболее близким к изобретению является логарифмический аналого-цифровой преобразователь, (АЦП), содержащий соединенные последовательно усилитель, компаратор, одновибратор и блок цифровой индикации, между инвертирующим входом и выходом усилителя включен интегрируюпщй конденсатор, инвертирующий вход уси,лителя через соединенные последова тельно первый ключ и масштабный резистор подключен ко входу логарифмического АЦП, между инвертирующим входом и выходом усилителя включены соединенные последовательно разрядный резистор и разрядный ключевой элемент, инвертирующий вход усилителя через второй ключ подключен к шине нулевого потенциала, неинвертирующий вход через запоминающий элемент - к шине нулевого потенциала, выход компаратора через третий ключ соединен с неинвертирующим входом усилителя, генератор опорной частоты, первый выход которого через модулятор подключен к дополнительному входу усилителя, второй выход - ко второму входу блока цифровой индикации, выход компаратора подключен к управляющим входам модулятора и разрядного ключевого элемента, выход генератора тактовых :импульсов соединен со входом блока (Синхронизации, первый выход которого подключен к управляющему входу первого ключа и к дополнительному управляющему входу разрядного ключевого элемента, второй выход блока синхронизации присоединен к управляющим входам второго и третьего ключей, тре тий выход блока синхронизации соединен с третьим входом блока цифровой индикации, источник опорного напряжения 2 . Это устройство характеризуется малой линейностью преобразования и ограниченной чувствительностью. Целью изобретения является повышение чувствительности и увеличение линейности преобразования. Предложенный логарифмический АЦП отличается от известного тем, что в него введен коммутатор, выход которого соединен со вторым входом компа ратора, первый информационный вход с источником опорного напряжения, а второй информационный вход -с шиной ну левого потенциала,а управляюсдай вход коммутатора - с первым выходом блока синхронизации. Функциональная схема предложенног логарифмического АЦП изображена на чертеже. Он содержит масштабный резистор 1 первый, второй и третий ключи 2,3 и 4, разрядный резистор 5, интегрирующий конденсатор 6, усилитель 7, запоминающий элемент 8, разрядный ключ вой элемент 9, модулятор 10, компара тор 11, коммутатор 12, генератор опо ной частоты 13, одновибратор 14, бло цифровой индикации I5, генератор так товых импульсов 16, блок синхронизации 17, источник опорного напряжения 18 и шину нулевого потенциала 19. АЦП работаетследующим образом. Цикл работы АЦП состоит из трех равных по времени тактов. В первом такте преобразования сиг налами с блока синхронизации 17 разомкнуты второй и третий ключи 3 и 4 замкнут первый ключ 2, а коммутатор 12 установлен в положение, при котором выход источника опорного напряже ния 18 подключен ко второму входу ко паратора 11. Входной сигнал с входа 20 через резистор 1 поступает на вход усилителя 7 и интегрируется на конденсато ре 6. Последний заряжается до напряжения источника опорного напряжения 18, причем прямо пропорционально величине входного сигнала и обратно пропорционально постоянной времени интегрирующей цепи, образованной резистором I и конденсатором 6. При этом разрядный ключевой элемент 9 разомкнут. В момент когда напряжение на конденсаторе 6 (соответственно, на выходе усилителя 7) превысит величину потенциала источника опорного напряжения 18, компаратор 11 своим выходным сигналом одновременно замкнет разрядный ключевой элемент 9, разрещит прохождение сигнала от генератора 13 через модулятор 10 и установит одновибратор 14 в состояние начала преобразования. ПОСКОЛЬКУ разрядный ключевой элемент 9 замкнут, то на выходе усилителя 7 формируется убывающее напряжение экспоненциальной формы, определяемое временем разрядка конденсатора 6 через резистор 5 и ключевой элемент 9. В момент когда убывающее напряжение на выходе усилителя 7 будет равно или меньше величины потенциала источника опорного напряжения 18, компаратор 11 своим выходным сигналом одновременно разомкнет ключевой элемент 9 и запретит прохождение сигнала через модулятор 10. Поскольку ключевой элемент 9 разомкнут, то снова будет заряжаться конденсатор 6, и все процессы повторятся. Поэтому; на выходе компаратора .11 будет частотная последовательность импульсов, продолжающаяся на протяжении времени первого такта. Частота этой. последовательности прямо пропорциональна логарифму преобразуемого входного сигнала и обратно пропорциональна разрядной времени цепи, образованной конденсатором 6 и резистором 5. Одновибратор 14 возвратится в исходное состояние, отмечая конец преобразования в каждый момент повторного замыкания ключевого элемента 9. Время от начала до конца преобразования будет заполнено частотой от генератора 13. Блок цифровой индикации 15 зафиксирует результат преобразования (возможна запись в этом блоке частоты на протяжении всего первого такта). Во втором такте индикации осуществляется индикация результатов в блоке цифровой индикации 15. Влок синхронизации 17 формирует сигналы, которые размыкают ключ 2, ключевой элемент 9, а коммутатор I2 устанавливают в положение, при котором второй вход компаратора 11 оказывается подключенным к шине нулевого потенциала 1 Кроме того, замыкаются ключи 3 и 4. На запоминающем элементе 8 происходит запоминание напряжения дрейфа н ля усилителя 7 и компаратора 1I с точностью до произведения их коэффициентов передачи. В такте преобразования из общего напряжения (измеряемое напряжение плюс напряжение дрейфа) вычитается напряжение дрейфа нуля. В подготовительном такте (третий такт) устанавливается в исходное.со стояние блок цифровой индикации 5. Таким образом, предложенный лога рифмический АЦП приобретает повышен ную чувствительность и линейность преобразования. Формула изобретения Логарифмический аналого-цифровой преобразователь, содержащий соединенные последовательно усилитель, компаратор, одновибратор и блок цифровой индикации, между инвертирующим входом и выходом усилителя включен интегрирующий конденсатор, инвертирующий вход усилителя через соеда нен ные последовательно первый ключ и масщтабный резистор подключен ко входу логарифмического аналого-цифро вого преобразователя, между инвертирующим входом и выходом усилителя включены соединенные последовательно разрядный резистор и разрядный ключевой элемент, инвертирующий вход усилителя через второй ключ подключен к шине нулевого потенциала, неин вертирующий вход усилителя через запоминающий элемент присоединен к яи не нулевого потенциала, выход кокпйратора через третий ключ срединси с неинвертирующим входом усилителя, re нератор опорной частоты, первый йыход которого через модулятор поДкЛ чен к дополнительному входу усилиТйля, второй В1ЛХОД генератора опорной частоты присоединен ко второму входу блока цифровой индикации, выход компаратора подключен к упраЬляЮ1ф1М входам модулятора и разрядного ключевого элемента, выход генератора тактовых импульсов соединен со входом блока синхронизации, первый выход Которого подключен к управляющему входу первого ключа и к дополнительному управляющему входу разрядного ключ вого элемента, второй выход блока синхронизации присоединен к управляющим входам второго и третьего кличей, третий выход блока синхронизации сое динен с третьим входом блока цифро вой индикации, источник опорного йапряжения, отличающийся тем, что, с целью повышения чувствительности и увеличения линейности рб образования, в него введен коммутатор, причем выход коммутатора соединен со вторым входом компаратора, первый информационный вход подключен к источнику опорного напряжения, второй информационный вход - к шине ну левого потенциала, а управляющий вход первому выходу блока синхронизации. Источники информации, принятые во внимание при экспертизе 1.Смолов В.Б. и др. Полупроводиковые кодирующие и декодиру|Ьщие реобразователи напряжений. М., Эмё1 ия, 1967, с.283-285, рис. 3-5. 2.Авторское свидетельство по заяве № 2683267/18-24,кл. G 06Q 7/24, 1978(прототип).

Авторы

Даты

1981-06-07—Публикация

1979-07-04—Подача