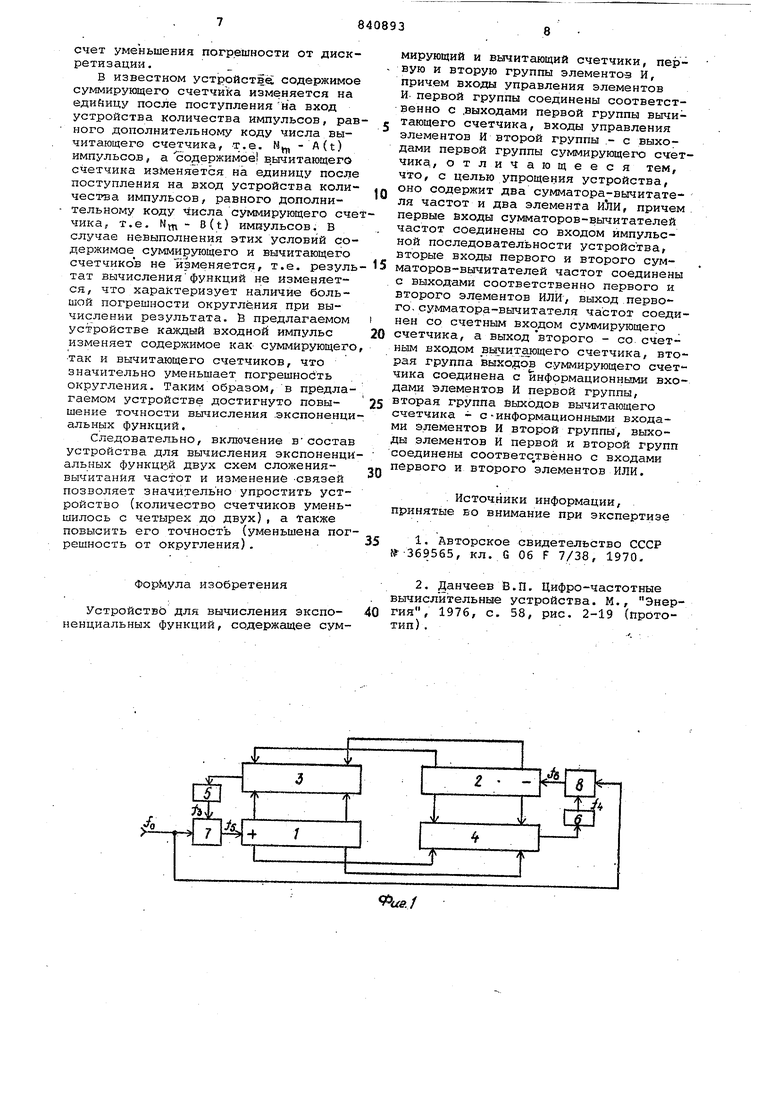

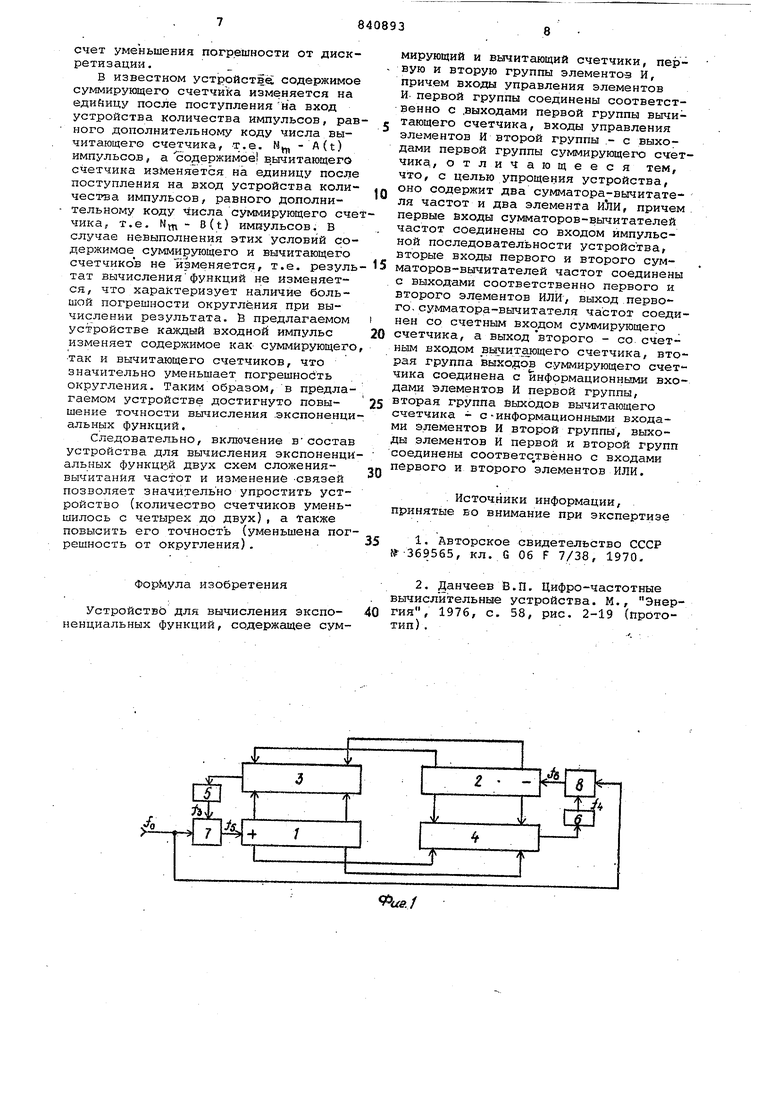

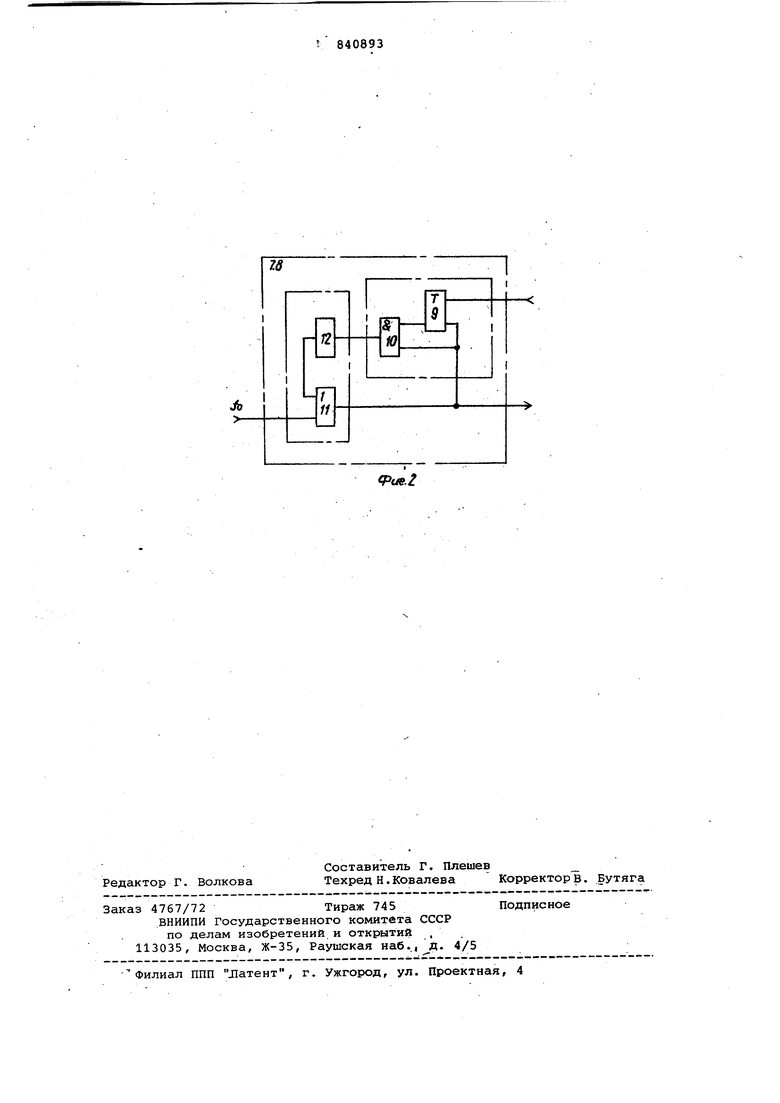

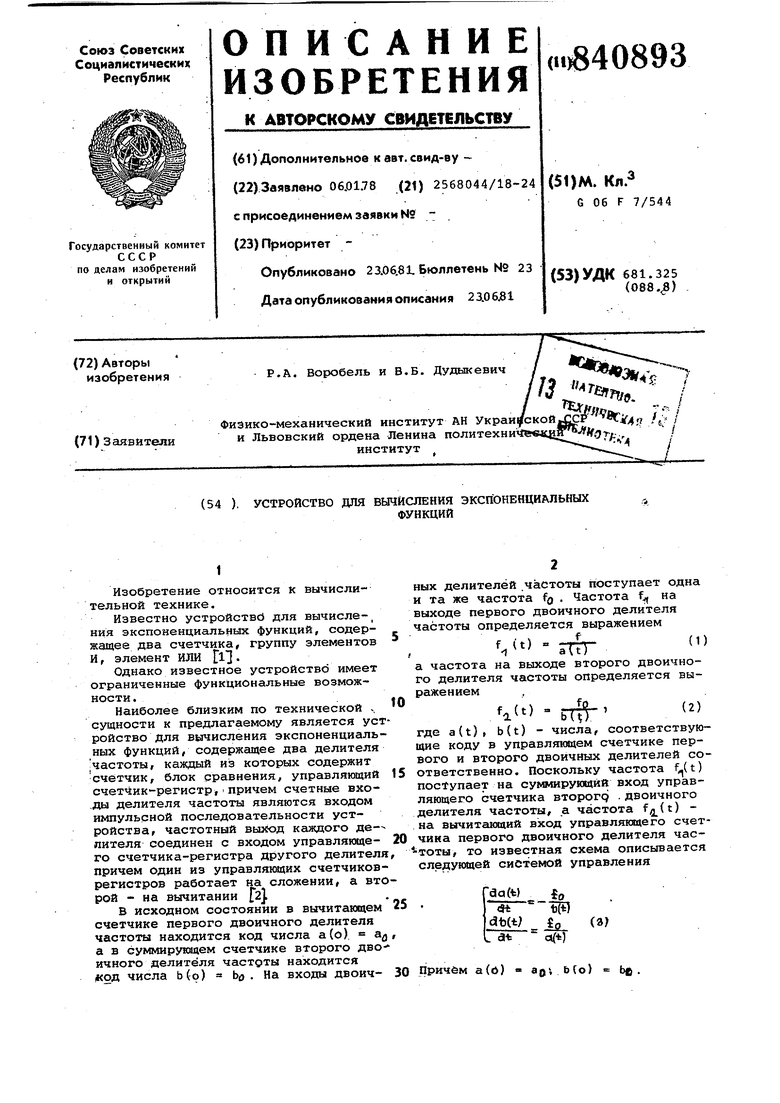

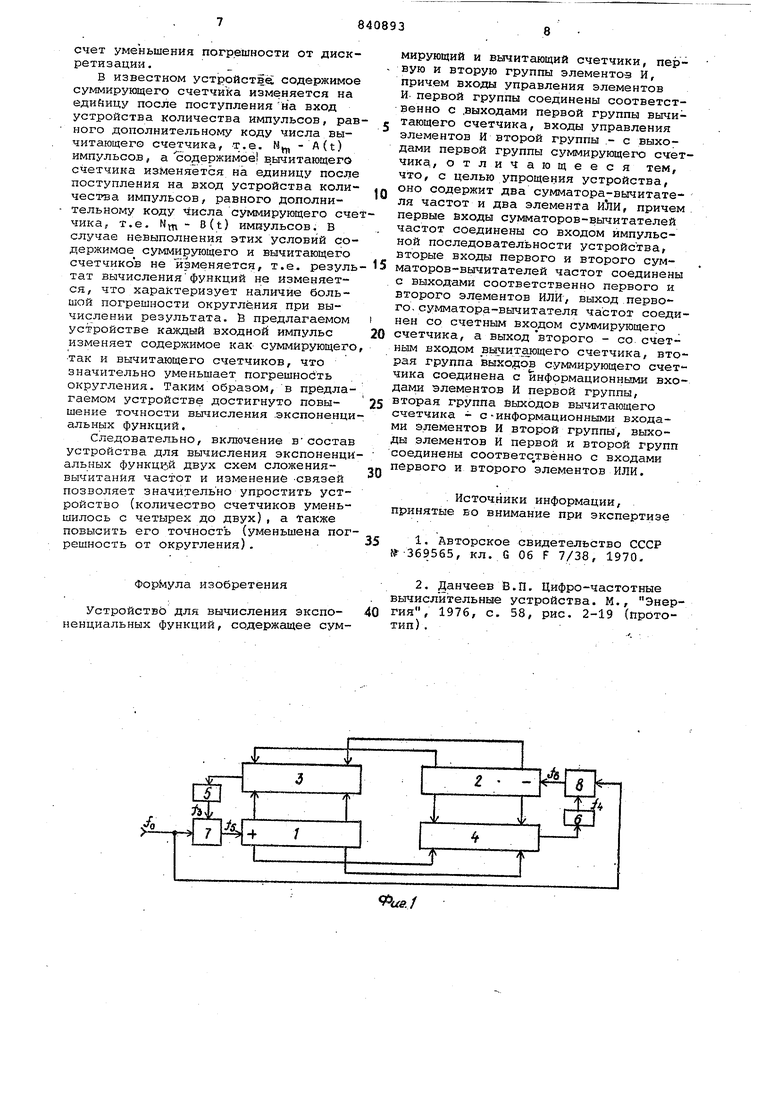

Изобретение относится к вычислительной технике. Известно устройстве для вычисле-, НИН экспоненциальных функций, содержащее два счетчика, группу элементов И, элемент ИЛИ 1. Однако известное устройство имеет ограниченные функциональные возможности. Наиболее близким по технической ., сущности к предлагаемому является уст ройство для вычисления экспоненциаль ных функций, содержащее два делителя ;частоты, каждый из которых содержит счетчик, блок сравнения, управлякнций счетчик-регистр,iпричем счетные вхо.ды делителя частоты являются входом импульсной последовательности устройства, частотный выход каждого делителя соединен с входом управляющего счетчика-регистра другого делителя причем один из управляющих счетчиковрегистров работает на сложении, а вто рой - на вычитании 2} В исходном состоянии в вычитающем счетчике первого двоичного делителя частоты находится код числа а(о) а а в суммирующем счетчике второго дво ичного делителя частоты находится (КОД числа Ь(о) bfl . На входы двоичных делителей частоты поступает одна и та же частота fo . Частота f,, на выходе первого двоичного делителя частоты определяется выражением ) гггг а частота на выходе второго двоичного делителя частоты определяется выражениемbllV где a{t), b{t) - числа, соответствующие коду в управляпощем счетчике первого и второго двоичных делителей соответственно. Поскольку частота f,(t) поступает на суммирующий вход управляющего счетчика второгр . двоичного делителя частоты, а частота f(t) на вычитающий вход управляющего счетчика первого двоичного делителя частоты, то известная схема описывается следующей системой управления JQ(t) f о ) (а L at ф Причём а(о) - ао, Ь(о) bft . Преобраздвав (З),. получаем Г, ,. aci(t) U(t). Ц,.-., Сложив уравнения в системе (4) получаем ,«w.bw.ii«- , С5) a(ciib) откуда следует, что или d(t)) C,on3t .(6} Определив из Чб) b(t) и подст вив в (4), получаем c3a(i) aobo Щ оРешив (7) методом разделения ременных, получаем о Поступив аналогично -со вторым уравнением системы (4), получаем i- Таким образом, при поступлении вход устройства тактовой частоты за время t t , т.е. при поступ нии Ny импульсов частоты f I Nv в управляющих счетчика двоичных делителей частоты формир ются, в соответствии с (8) и (9J, коды чисел ()Ur«oE 4-V o Однако известное устройство рб дает чрезмерной сложностью и недо точной точностью, обусловленной б шой погрешностью округления из-за применения двоичного делителя час ты с постоянной времени системы равной, как следует из (8) и (9) , .. (,,) Цель изобретения - упрощение у ройства и повышение его точности Поставленная цель достигается тем, что.устройство, содержащее суммр рующий и вычитающий счетчики nepB3 Jo и вторую группы элементов при этом входы управления первой пы элементов И соединены соответс венно с выходами первой группы вы тающего счетчика, а входы управле второй труппы элементов И - с вых дами первой группы суммирующего с чика, дополнительно содержит два рационных блока и два элемента ИЛ причем первые входы рперационных блоков, соединены со входом импул ной последовательности устройства, вторые входы первого и второго операционных блоков соединены с выходами соответственно первого и второго элементов ИЛИ, выход первого операционного блока соединен со счетным входом суммирующего счетчика, а выход второго - со счетным входом вычитающего счетчика, вторая группа выходов суммирующего счетчика соединена с. информационными входами первой группы элементов И, вторая группа выходов вычитающего счетчика с информационными входами второй группы элементов И, выходы первой и второй групп элементов И соединены соответственно с входами первого и второго элементов ИЛИ. На фиг. 1 схематично изображено предлагаемое устройство; на фиг. 2 операционный блок, Устройствб содержит суммирующий счетчик -1, вычитающий счетчик 2, группы элементов И 3 и 4, элементы ИЛИ 5 и б, операционные блоки 7 и 8. Каждый операционный блок содержит триггер 9, элемент И 10, элемент ИЛИ 11, элемент задержки 12. При этом первый вход элемента ИЛИ является первым входом операционного блока, второй вход элемента ИЛИ соединен с выходом элемента задержки, а выход элемента ИЛИ соединен с первь1ми входами элемента И и триггера и является выходом операционного блока, второй вход триггера является вторым входом операционного блока, выход триггера соединен со вторым входом элемента И, выход которого соединен с выходом элемента задержки. Устройство работает следующим образом. В исходном состоянии в вычитающем счетчике 2 находится код числаА /tx О а а в суммирующем счетчике 1 находится код числа 3 /t о/ Ь. На первые входы операционных блоков 7 и 8 поступает тактовая частота fp. С выхода блока 7 частота fj поступает на вход суммирующего счетчика 1. Счетчик 1 с группой 3 схем совпадения представляет собой двоичный умножитель частоты, управляемый кодом числа А (t) вычитающего счетчика 2, поэтому частота f на выходе элемента ИЛИ 5 определяется выражением fs-AW где N .„ 2 - коэффициент пересчета счетчиков 1 и 2; п - количество двоичных разрядов счетчиков 1 и 2; А (t) - код числа вычитающего счетчика 2. Вычитающий счетчик 2 с группой 4 схем совпадения представляет собой двоичный умножитель частоты, управляемый кодом числа В (t) суммирующего счетчика 1, Поэтому частота | на выходе элемента ИЛИ 6 определяет ся выражением о п/4. -tt, Dtt) где f, - частота на выходе блока 8. Так как частота fg поступает на , второй вход блока 7, то в соответствии с фиг. 2,.частота f на ее выходе определяется выражением или, с учётом (12),

. i, С15)

N

m

(Откуда

(16)

Аналогичным образом, так как частота f поступает на второй вход блока 8, то, в соответствии с фиг.2, частота f, на ее выходе определяется выражением

(

или, с учетом (13),

ib-bC-t)

-±ь

fn

IV

откуда

o-Nm

(-(9)

f

ftCtl

Так как частота f поступает на вход вычитающего счетчика 2, а частота fj - на вход суммируквдего счетчика 1, то числа А (t) и В (t), соответствующие кодам вычитающего счечика 2 и суммирующего счетчика 1/ соответственно равны t

A(t) N

(20)

dt

fc B(t) f

(1-0

dt

где t - текущее время.

Для определения A(t) и B(t) необходимо решить уравнения (20) и (21), Продифференцировав (20) и (21), .получаем следующую систему уравнений d Ла)

-V

a-fc

Саа) d SCfc)

«5

dt

в (22)I пои (19)

Подставив (16) лучаем

o-Hni

. B(-t)

{1г1

o-Nm

л{)

или

|6W.Ai -foN«

(а4)

8408 5 10

или

aA(t)

,ЩГ

Проинтегрировав (27) . получаем .ЧпЛ.,(ав)

где С - постоянная, интегрирования. При t О, A(t) а-, поэтому С еп зд и

enA(t)-%4p -bendo,

откуда

30

. loNm

Att)aoe (аэ)

Решив аналогичным, методом второе 35 уравнение системы (24) уравнений, получаем

-М«т .

8(t)b,,e

(30)

Таким образом, в течение времени t t , при поступлении на вход устройства Ny импульсов частоты fp Ny( fл. , в соответствии с (29) и (30), в вычитающем счетчике 2 и суммирующем счетчике 1 формируются соответственно коды чисел

А A(t)J. адЕ

aotoo

.

(31).

и В

Как следует из (29) и.(ЗО) постоянная времени t системы в предлагаемои устройстве для вычисления экспонейциальных функций равна

., )o

Сравнивая выражения (11): и (12) Ёидим, что в предлагаемом устройстве для вычисления экспоненциальных функций постоянная времени t системы уменьшена, что позволяет повысить

точность высисления функций (31) за 36 Сложив уравнения в системе (24), получаем M«.,SU,-, откуда следует, что d(A-,6) д аГ или A{t) B(t) Const ао bp где а, A(t) J b B(t) Определив из (25) B(t) и подставив в первое уравнение системы уравнений (24) , получаем счет уменьшения погрешности от дискретизации. В известном устройства содержимое суммирующего счетчика изменяется на едийицу после поступления на вход устройства количества импульсов, рав ного дополнительному коду числа выт.е. N.. - A(t) читающего счетчика. импульсов, а содержимое в.ычитающего счетчика изменяется на единицу после поступления на вход устройства количества импульсов, равного дополнительному коду числа суммирующего сче чика, т.е. - B(t) импульсов. В случае невыполнения этих условий содержимое суммирующего и вычитающего счетчиков не изменяется, т.е. резуль тат вычисленияфункций не изменяется, что характеризует наличие большой погрешности округления при вычислении результата. В предлагаемом устройстве каждый входной импульс изменяет содержимое как суммирующего так и вычитающего счетчиков, что значительно уменьшает погрешность округления. Таким образом, в предлагаемом устройстве достигнуто повышение точности вычисления .экспоненци альных функций. Следовательно, включение всостав устройства для вычисления экспоненци альных функций двух схем сложениявычитания частот и изменение -связей позволяет значительно упростить устройство (количество счетчиков уменьшилось с четырех до двух), а Также повысить его точность (уменьшена пог решность от округления). Формула изобретения УстройствЬ для вычисления экспо- 40 ненциальных функций, содержащее суммирующий и вычитающий счетчики, первую и вторую группы элементов И, причем входы управления элементов И- первой группы соединены соответственно с .выходами первой группы вычитающего счетчика, входы управления элементов И второй группы .- с выходами первой группы суммирующего счетчика, отличающееся тем, что, с целью упрощения устройства, оно содержит два сумматора-вычитателя частот и два элемента И51И, причем первые входы сумматоров-вычитателей частот соединены со входом импульсной последовательности устройства, вторые входы первого и второго сумматоров-вычитателей частот соединены с выходами соответственно первого и второго элементов ИЛИ, выход первого, сумматора-вычитателя частот соединен со счетным входом суммирующего счетчика, а выход второго - со счетным входом вь1}штающего счетчика, вторая группа выходов суммирующего счетчика соединена с информационными входами элементов И первой группы, вторая группа Выходов вычитающего счетчика - с-информационными входами элементов И второй группы, выходы элементов И первой и второй групп соединены соответственно с входами первого и второго элементов ИЛИ. . Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР №369565, кл. G Об F 7/38, 1970. 2. Данчеев В.П. Цифро-частотные вычислительные устройства. М., Энергия, 1976, с. 58, рис. 2-19 (прототип), , .

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразовательчиСлА иМпульСОВ B цифРОВОй КОд | 1979 |

|

SU807285A1 |

| Цифровой функциональный генератор | 1978 |

|

SU734644A1 |

| Устройство для возведения в степень | 1984 |

|

SU1282119A1 |

| Функциональный преобразователь | 1980 |

|

SU955040A1 |

| Устройство для вычисления элементарных функций | 1981 |

|

SU970380A1 |

| Устройство для вычисления логарифмов чисел | 1977 |

|

SU741263A1 |

| Преобразователь угловых перемещений в код | 1982 |

|

SU1035627A1 |

| Вычислительное устройство | 1978 |

|

SU840902A1 |

| Устройство для деления | 1986 |

|

SU1429110A1 |

| Устройство для деления | 1986 |

|

SU1425657A1 |

./а

J

1 11

Jb

W ю

Авторы

Даты

1981-06-23—Публикация

1978-01-06—Подача