... 1 Изобретение относится к вычислительной технике. Известно устройство, содержащее преобразователь код-частота, счетчики импульсов, блок сравнения кодов, регистр сомножителя, элементы И Щ. Недостатками известного устройст.ва являются ограниченные функциональ ные возможности и сложность. Наиболее близким по технической сущнрсти к предлагаемому является вы числительное устройство, содержащее два двоичных делителя частоты, каждый из которых состоит из регистра, блока сравнения кодов и счетчика, два счетчика, элемент И и элемент запрета, соединены со счетньтми входами первого и третьего счетчиков 12 Для выполнения операции сложения двух чисел X и У в счетчик результата записывается число X, а в счетчик-регистр вносится число У в допол нительном коде. Счетчики первого и второго двоичных делителей частоты устанавливаются в нулевое состояние, а в регистры первого и второго двоич ных делителей частоты заносился единица в млсщшие разряды. Тактовые импульсы проходят через двоичные делигели на счетчик результата и счетчик регистр до тех пор, пока на счетчикрегистр не будет передано число У, переводящее его в нулевое состояние. В этот момент срабатывает дешифратор нулевого состояния, закрывает элемент запрета и тем самым прекращает поступление тактовой частоты на входы двоичных делителей. В счетчике результата при этом формируется число X + У, за время,равное tt/v Т(,«Х,,,. (О где Тд - период частоты F Работа устройства в режиме вычитания отличается от режима сложения занесением в счетчик-регистр прямого кода числа У. Тогда, вмомент запирания элемента запрета по1;енциалом эле- мента И, в счетчике результата формируется число N X + NTH У X - У, где N 2 - коэффициент пересчета счетчика-регистра и счетчика результата. Этот результат формируется за время, равное Чык T(,..( Y) (2) Для умножения двух чисел X и У перед началом операции сомножитель X записывается в регистр первого двоичного делителЯ, а дополнительный код числа У - в счетчик-регистр; счетчики двоичных делителей и счетчик результата устанавливаются в нулевое состояние, а в регистр второго двоичного делителя частоты заносится едница. Тогда на выходе счетчика-регистра формируется последовательност импульсов с периодом Tjj, X. После пос.тупления У импульсов в счетчик-регистр за время

Ьми Y fo- X (3) в счетчике результата формируется число

N FP . Tj, X - Y X Y С) При выполнении операции деления в исходном сос±ояний счетчики двоичных делителей исчетчик результата находятся в нулевом состоянии. В регистр первого двоичного делителя заносится единица, в регистр второго двоичного Делителя - код числа У, а в счетчик-регистр - дополнительный код числа X. Тогда после поступления X импульсов в счетчик-регистр с выхода первого двоичного делителя частоты, за время

tAgA Т. X ,. (5) в счетчике результата формируется код числа

ГЬ-НЗ-Х-Т (6}

Недостатками известного устройства являются чрезмерная сложность и низкое быстродействие.

Цель изобретения - повышение быстродействия и упрощение устройства.

Поставленная цель достигается тем, что в устройство, содержащее дв регистра операндов, два счетчика, элемент И, элемент запрета, причем выходы первой группы первого счетчика соединены соответственно с входами элемента И, выход которого соединен с входом, управления элемента запрета, информационный вход которого является входом импульсной последовательности устройства, дополни.тельно введены две группы элементов И, два операционных блока, два элемента ИЛИ, при этом первые входы операционных блоков соединены с выходом элемента запрета, вторые входы,, первого и второго.операционных блоков - с выходами соответственно первого и второго элементов ИЛИ, выходы операционных блоков соединены со счетными входами соответственно первго и второго счетчиков, выходы второй гЬуппы первого счетчика и выходы второго счетчика соединены соответственно с информационными входами первой и второй групп элементов И, входы управле,ния которых соединены соответственно с выходами первого и второго регистров операндов, а выходы - со входами соответствующих элементов ИЛИ.

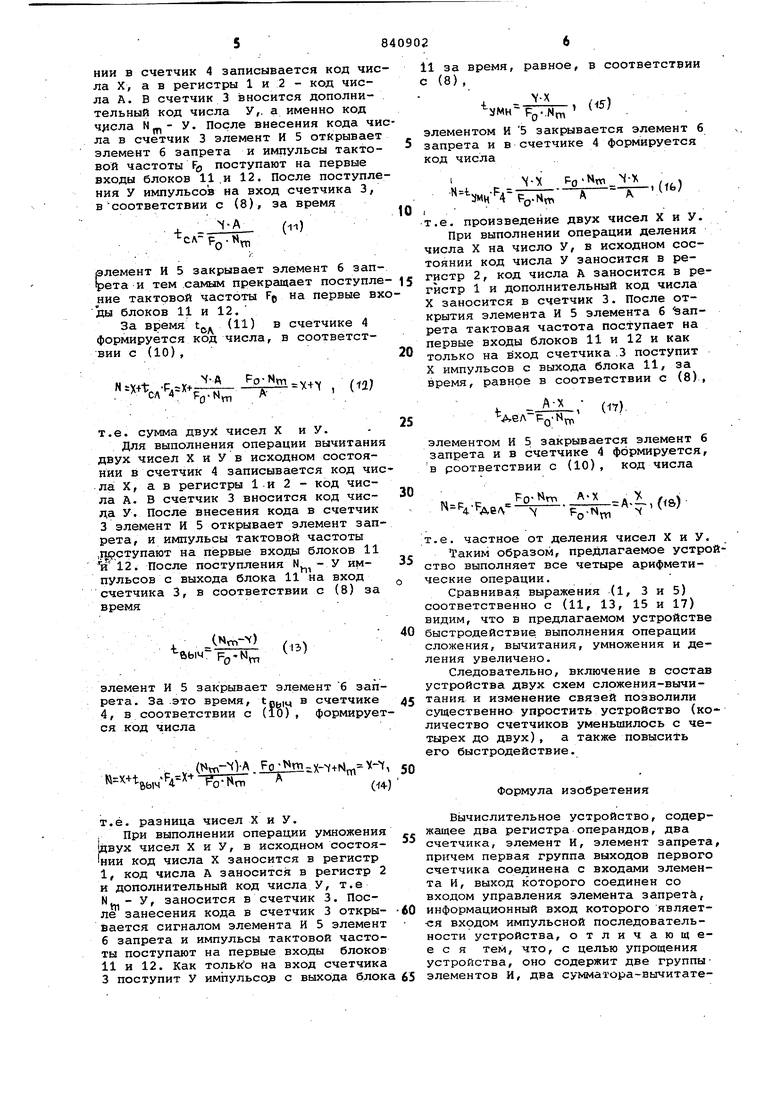

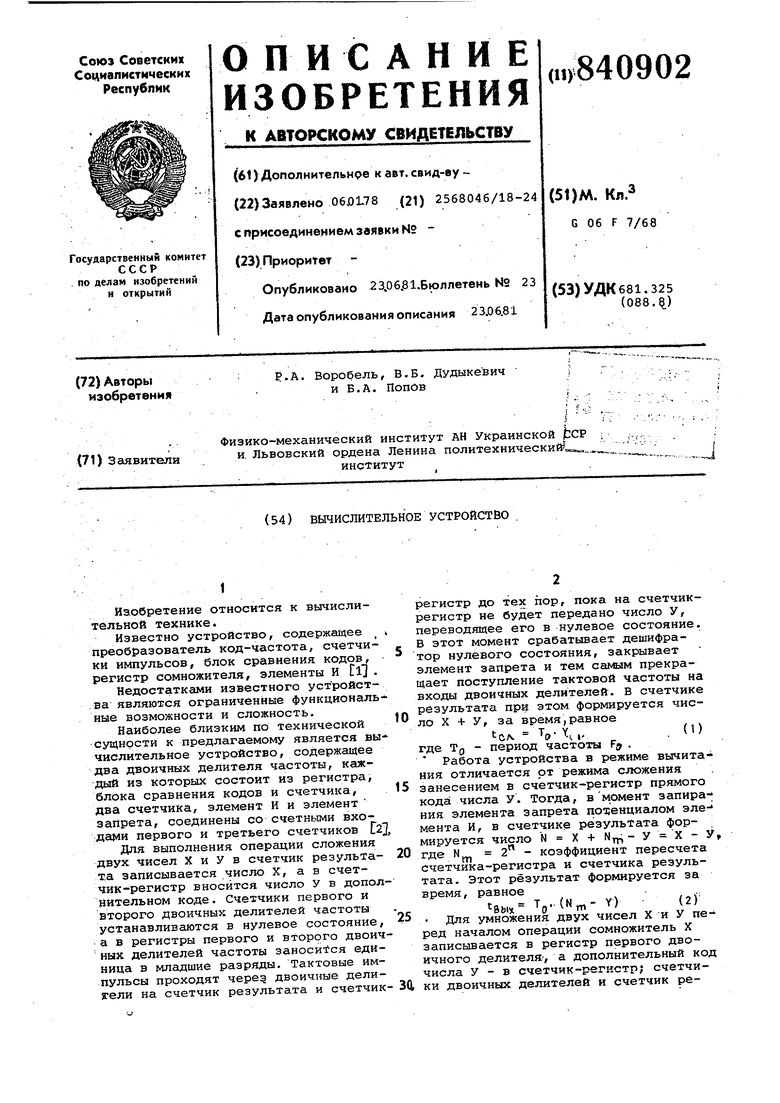

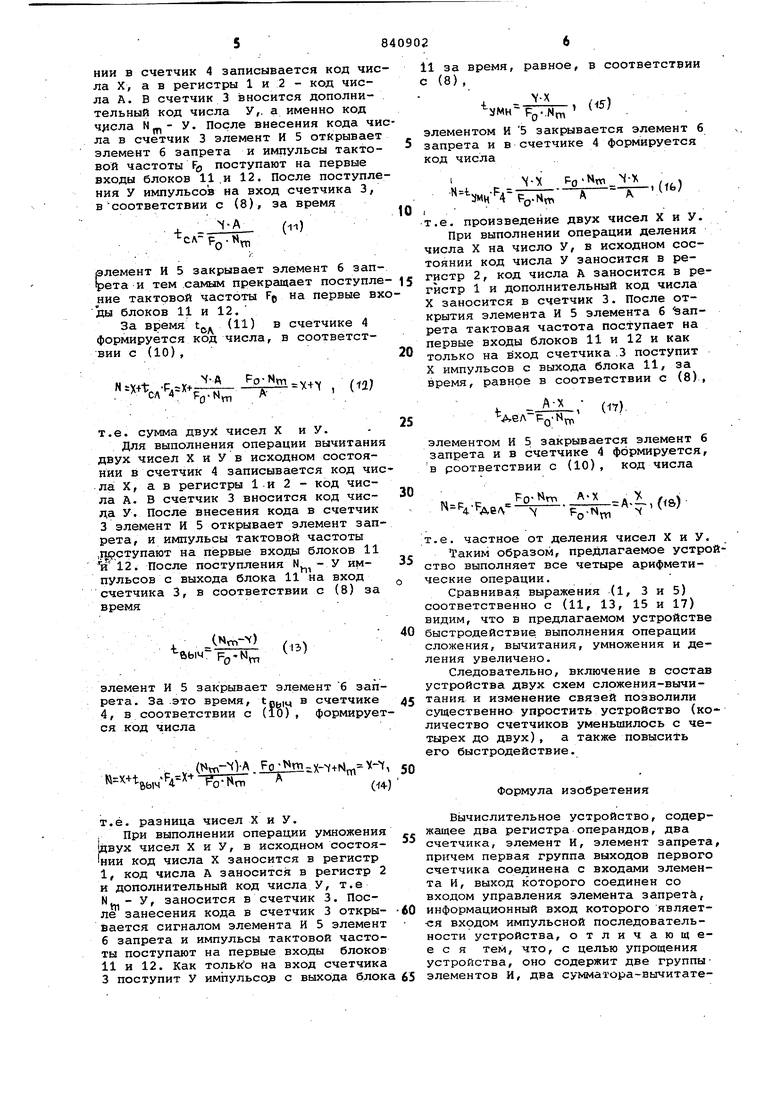

На фиг. 1 приведена схема устройства, на фиг. 2 - схема операционного блока.

Устройство содержит регистры 1 и 2 операндов, счетчики 3 и 4, элемент И 5, элемент б запрета, группы элементов И 7 и 8; элементы ИЛИ 9 и 10; операционные блоки 11 и 12, Каждый операционный блок включает триггер 13, элемент И 14, элемент ИЛИ 15, элемент 16 задержки. При этом первый вход элемента ИЛИ являетс первым входом операционного блока, второй вход элемента ИЛИ соединен с выходом элемента задержки,-а выход элемента ИЛИ соединен с первыми входами элемента И и триггера и является выходом операционного блока., второй вход триггера является вторым входом операционного блока, выход триггера соединен со вторым входом элемента И, выход которого соединен с входом элемента задержки.

Устройство работает, следуняцим образом.

На первые входы операционных блоков 11 и.12 при открытом элементе 6 запрета поступает тактовая частота fj,

Регистр 1 операнда с группой 7 элементов И, элементом ИЛИ 9 и счетчиком 3 представляет собой двоичный умножитель частоты, управляемый ко-.

дом числа 2 регистра 1, поэтому часна выходе элемента ИЛИ 9 оптота F. ределяется выражением 2.

(7)

- -1 Frn

где F - частота на выходе блока 11; Z - число, соответствующее коду в регистре 1; N 2 - коэффициент пересчета счетчика 3; п - количество разрядов регистра 1 и счетчика 3.

Так как частота F., поступает на второй вход блока 11, то, в соответствии с фиг. 2, частота F- на его выходе определяется выражением

- 11откуда, с учетом (7/1

Nn,

.()

Регистр 2 с группой элементов И 8, элементом ИЛИ 10 и счетчиком 4 представляет собой двоичный умножитель частоты, управляемый кодом числа Z регистра 2. Поэтому частота F.J на выходе элемента ИЛИ 10 определяется выражением

г Й

где F4- и частота на выходе блока 12 Nj 2 - коэффициент пересчета счетчика 4; п-количество двоичных разрядов регистра 2 и счетчика 4.

С выхода элемента ИЛИ 10 частота FJ поступает на второй вход блока 12, поэтому, в соответствии с фиг. 2, частота Fyj, на его выходе определяется вырс1жением Рд F +. F - F« , откуда, с учетом (9),

ffiNm , (,о)

-1

Для выполнения операции сложения двух чисел X и У, в исходном состояНИИ в счетчик 4 записывается код чис ла X, а в регистры 1 и 2 - код числа А. В счетчик 3 вносится дополнительный код числа У,, а именно код У. После внесения кода чи ла в счетчик 3 элемент И 5 открывает элемент б запрета и импульсы тактовой частоты FO поступают на первые входы блоков 11 .и 12. После поступле ния У импульсов на вход счетчика 3, всоответствии с (8), за время элемент И 5 закрывает элемент 6 запрета и тем .самым прекращает поступле ние тактовой частоты Fp на первые вх ды блоков 11 и 12. За время t,. (11) в счетчике 4 формируется код числа, в соответствии с (10) , Fo-Ntn y (12) ).е. сумма двух чисел X и У. Для выполнения операции вычитания двух чисел X и У в исходном состоянии в счетчик 4 записывается код чис ла X, а в регистры 1 и 2 - код числа А. В счетчик 3 вносится код чисда У. После внесения кода в счетчик 3 элемент И 5 открывает элемент запрета, и импульсы тактовой частоты .прступают на первые входы блоков 11 if 12. После поступления N - У импульсов с выхода блока 11 на вход счетчика 3, в соответствии с (8) за время (Nm-) -6ЫЧ-F -N элемент И 5 закрывает элемент 6 запрета. За .это время, в счетчике 4, в соотве.тствии с (10), формирует ся код числа « -wv-« - -- - ; т.е. разница чисел X и У. . При выполнении операции умножения двух чисел X и У, в исходном состоя нии код числа X заносится в регистр 1, код числа А заносится в регистр 2 и дополнительный код числа У, т.е N.- У, заносится в счетчик 3. После занесения кода в счетчик 3 открыбается сигналом элемента И 5 элемент б запрета и импульсы тактовой частоты поступают на первые входы блоков 11 и 12. Как на вход счетчика 3 поступит У импульсов с выхода блок 11 за время, равное, в соответствии с (8) , элементом И 5 закрывается элемент 6 запрета и в счетчике 4 формируется код числа -Х N-X Л WH-4 Р„.КГГ т.е. произведение двух чисел X и У. При выполнении операции деления числа X на число У, в исходном состоянии код числа У заносится в регистр 2, код числа А заносится в регистр 1 и дополнительный код числа X заносится в счетчик 3. После открытия элемента И 5 элемента б Запрета тактовая частота поступает на первые входы блоков 11 и 12 и как только на ёход счетчика .3 поступит X импульсов с выхода блока 11, за время, равное в соответствии с (8) , Д-Х ASA-PQ-N элементом И 5 закрывается элемент 6 запрета и в счетчике 4 формируется, з роответствии с (10), код числа Fo-Nn А.Х ,. У , V. N P4PAeV V с .м т.е. частное от деления чисел X и У. Таким образом, предлагаемое устройство выполняет все четыре арифметические операции. Сравнивая выражения (1, 3 и 5) соответственно с (11, 13, 15 и 17) видим, что в предлагаемом устройстве быстродействие выполнения операции сложения, вычитания, умножения и деления увеличено. Следовательно, включение в состав устройства двух схем сложения-вычитания и изменение связей позволили существенно упростить устройство (количество счетчиков уменьшилось с четирех до двух), а также повысить его быстродействие. Формула изобретения Вычислительное устройство, содержащее два регистра операндов, два счетчика, элемент И, элемент запрета, причем первая группа выходов первого счетчика соединена с входами элемента И, выход которого соединен со входом управления элемента запрети, информационный вход которого является вхрдом импульсной последовательности устройства, отличающееся тем, что, с целью упрощения устройства, оно содержит две группыэлементов И, два сумматора-вычитателя частот, два элемента ИЛИ, при этом первые входы сумматоров-вычитателей частот соединены с выходом элемента запрета, вторые входы первого и вто- , рого сумматоров-вычитателей частот с выходами соответственно первого и второго элементов ИЛИ, выходы сумматоров-вычитателей частот, соединены со счетными входами соответственно первого и второго счетчиков, вторая группа выходов первого счетчика и выхЬды второго счетчика соединены .соответственно с информационными входами элементов И первой и второй

групп, входы управления которых соединены соответственно с выходами первого и второго регистров операндов, а выходы - со входами соответствующих элементов ИЛИ.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 310257, кл. G 06 G 7/16, 1970.

2.Денчеев В.П. Цифрочастотные вычислительные устройства.М., Энергия, 1976, с. 69-70, рис. 2-31 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления экспоненциальныхфуНКций | 1978 |

|

SU840893A1 |

| Устройство для деления | 1989 |

|

SU1619255A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Устройство для сложения и вычитания чисел по модулю | 1988 |

|

SU1599857A1 |

| Устройство для формирования спектров с постоянным относительным разрешением по направлениям | 1984 |

|

SU1229775A1 |

| Устройство для поворота вектора | 1983 |

|

SU1132285A1 |

| Устройство для деления | 1985 |

|

SU1283752A1 |

| Устройство для деления | 1984 |

|

SU1249551A1 |

| Двоичное устройство деления | 1975 |

|

SU541171A2 |

| Генератор функций Уолша | 1985 |

|

SU1262470A1 |

гС

Л .

Авторы

Даты

1981-06-23—Публикация

1978-01-06—Подача