4

СО

Изобретение относится к вычислительной технике и может быть применено в быстродействующих вычислительных устройствах для выполнения операции деления чисел.

Цель изобретения - повышение быстродействия устройства за счет сокращения длительности такта формирования k цифр частного.

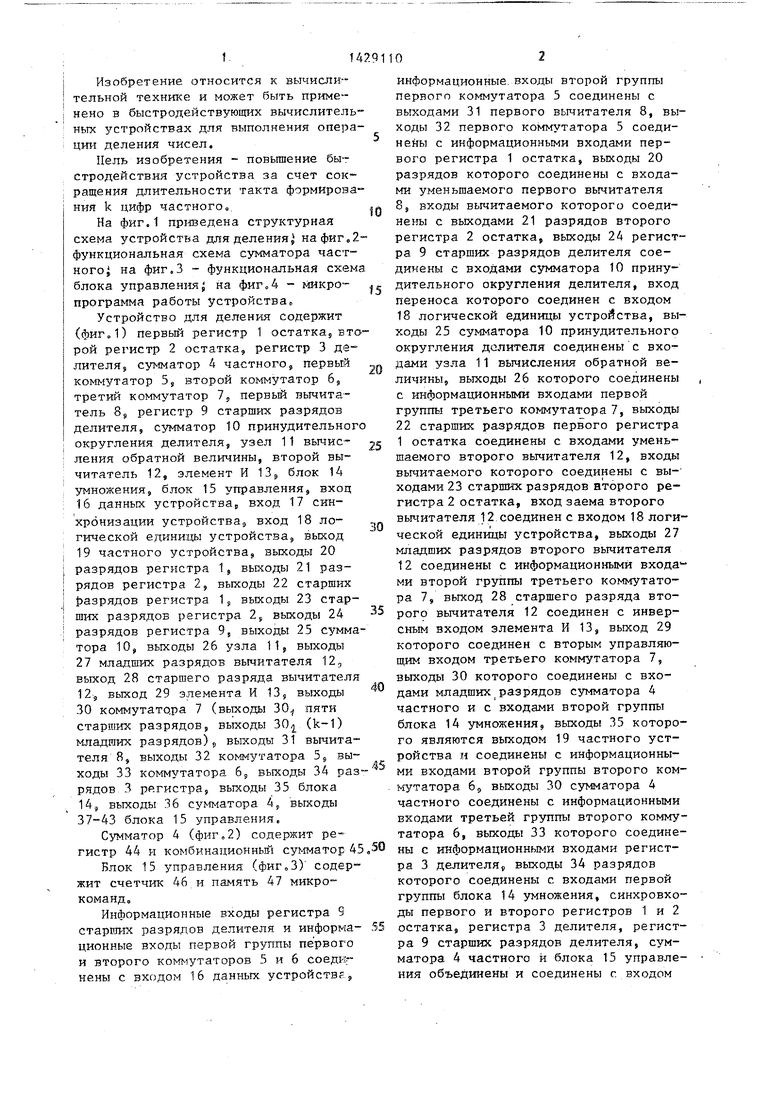

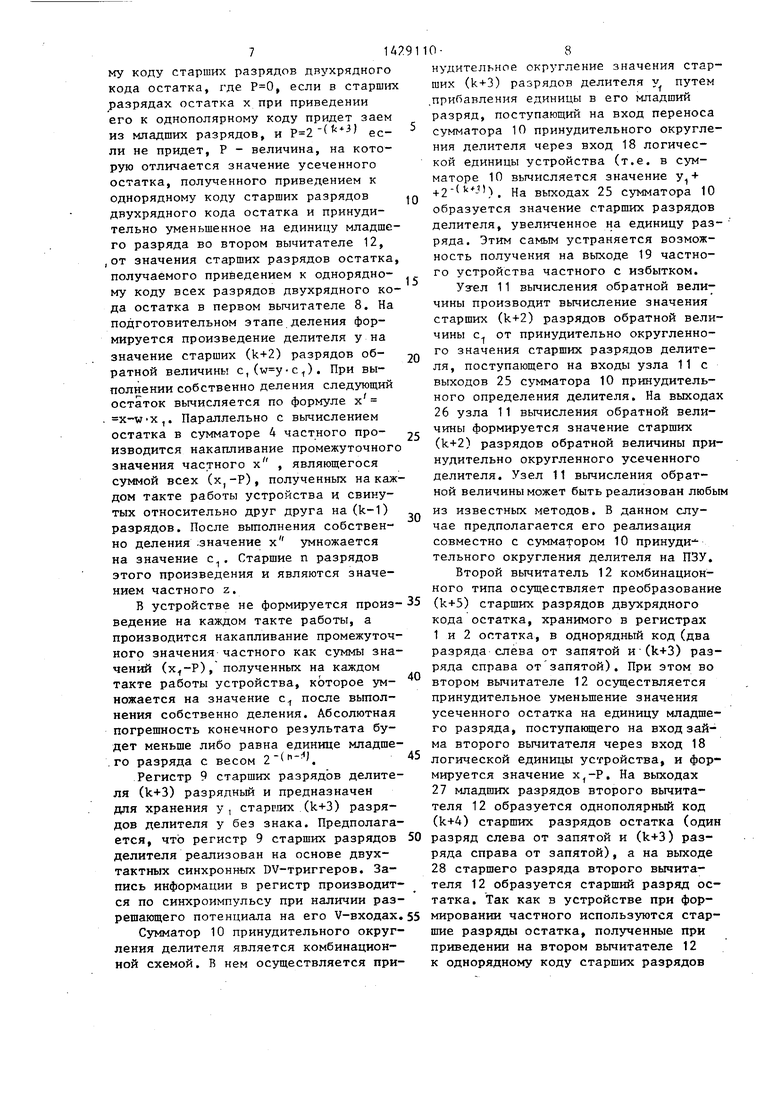

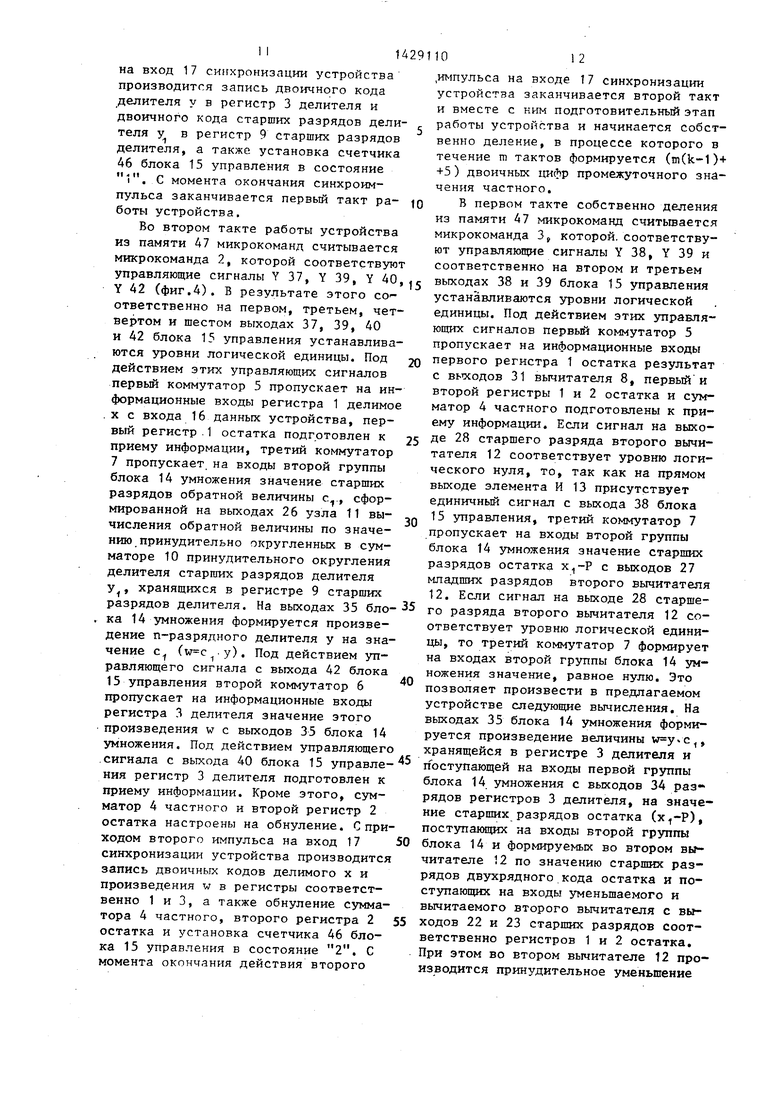

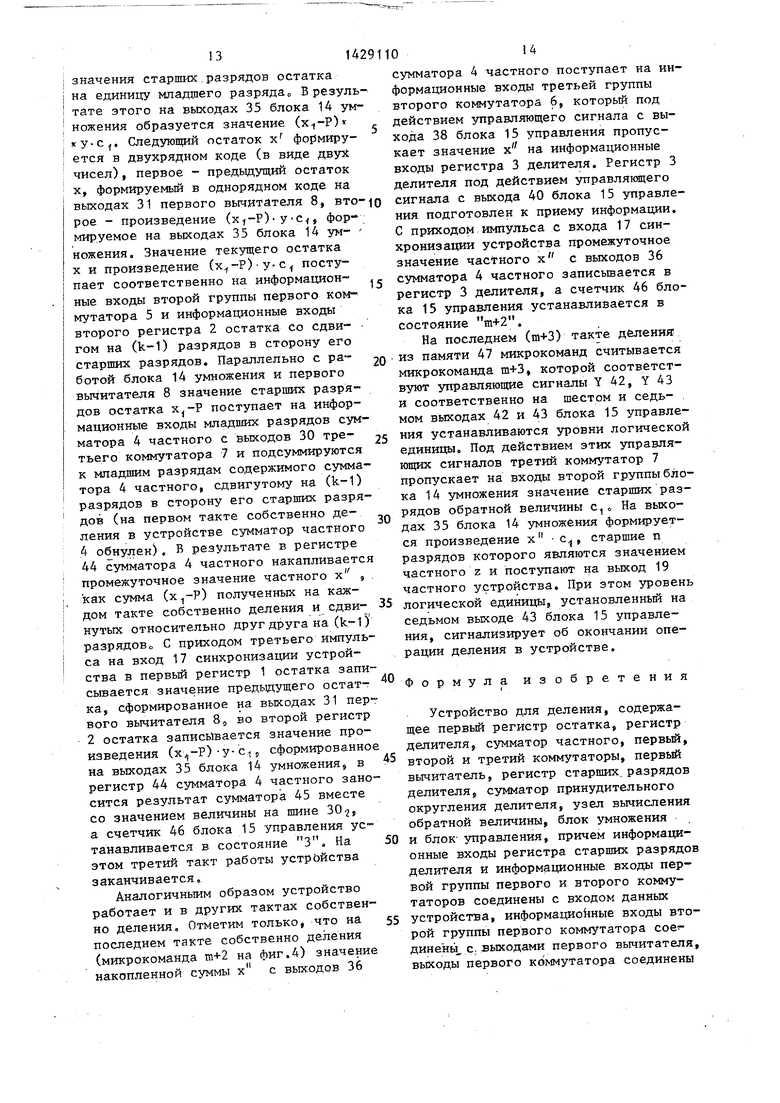

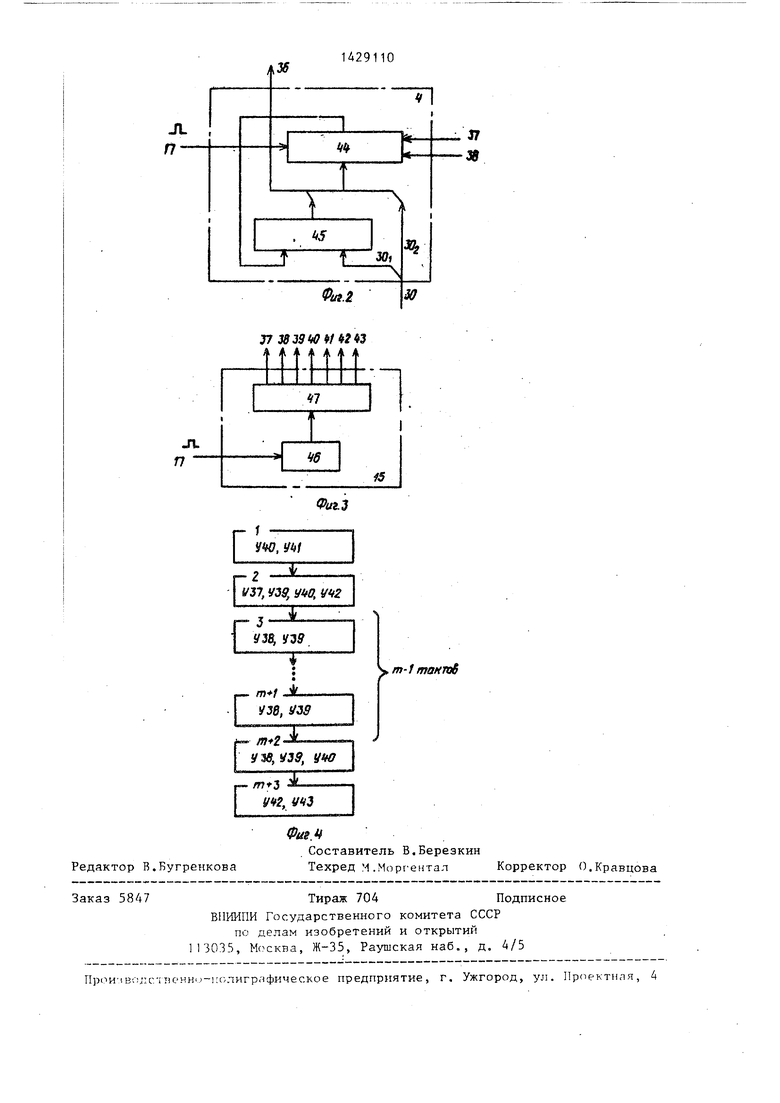

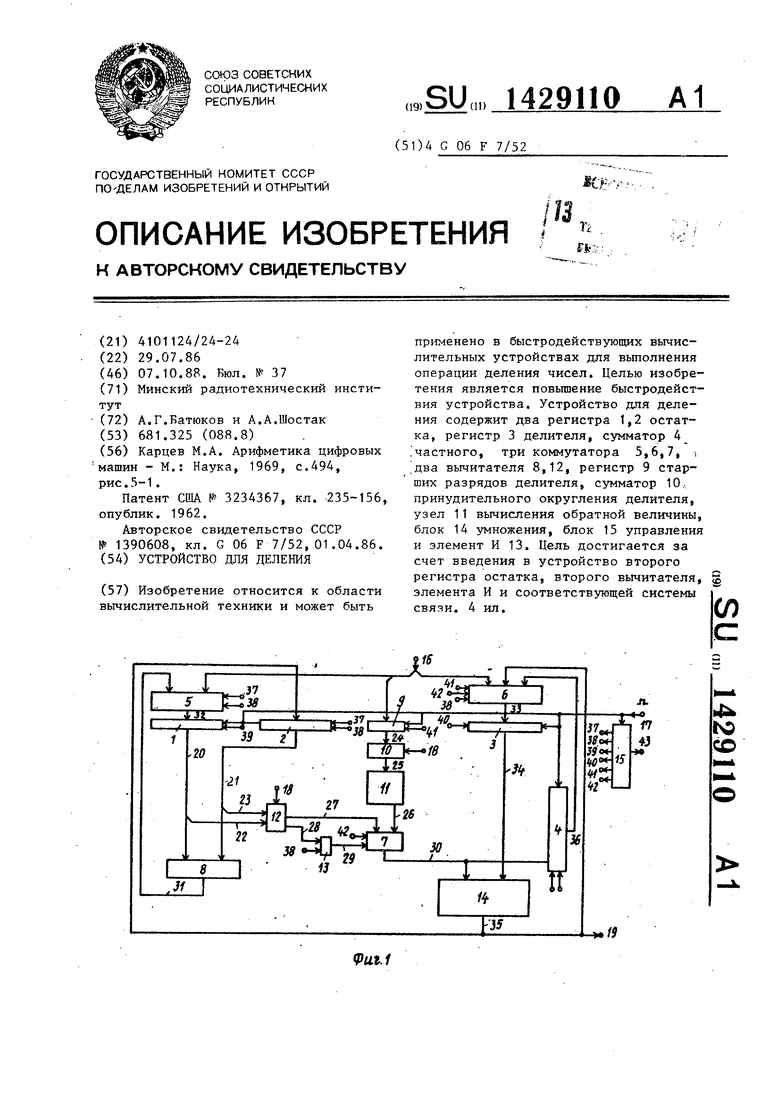

На фнг.1 приведена структурная схема устройства для деления на фиг,2- функциональная схема сумматора частного i на фиг.З - функциональная схема блока управления; на фиг„4 - микро- программа работы устройства.

Устройство лпя деления содержит (фиг„1) первый регистр 1 остаткаг второй регистр 2 остатка, регистр 3 делителя, сумматор 4 частного, первый коммутатор 5, второй коммутатор 6, третий коммутатор 7, первьй пычита- тель 85 регистр 9 старших разрядов делителя, сумматор 10 принудительного

округления делителя, узел 11 вычисления обратной величины, второй вы- читатель 12, элемент И 13 блок 14 умножения, блок 15 управления, вход 16 данных устройствав вход 17 синхронизации устройства, вход 18 логической епини:цы устройства, выход 19 частного устройства, выходы 20 разрядов регистра 1, ВЬЕХОДЫ 21 разрядов регистра 2, выходы 22 старших {разрядов регистра 1, выходы 23 старших разрядов регистра 2 выходы 24 разрядов регистра 9s выходы 25 сумматора 10, выходы 26 узла 11, выходы 27 младших разрядов вычитателя 12, выход 28 старшего разряда вычитателя 12, выход 29 элемента И 13, выходы 30 коммутатора 7 (вьрсоды 30 пяти старших разрядов, выходы 30 (k-1) младших разрядов)р выходы 31 вычитателя 8, выходы 32 коммутатора Sj выходы 33 коммутатора 65 выходы 34 раз рядов 3 регистра, выходы 35 блока 14, выходы 36 сумматора 4 выходы 37-43 блока 15 управления.

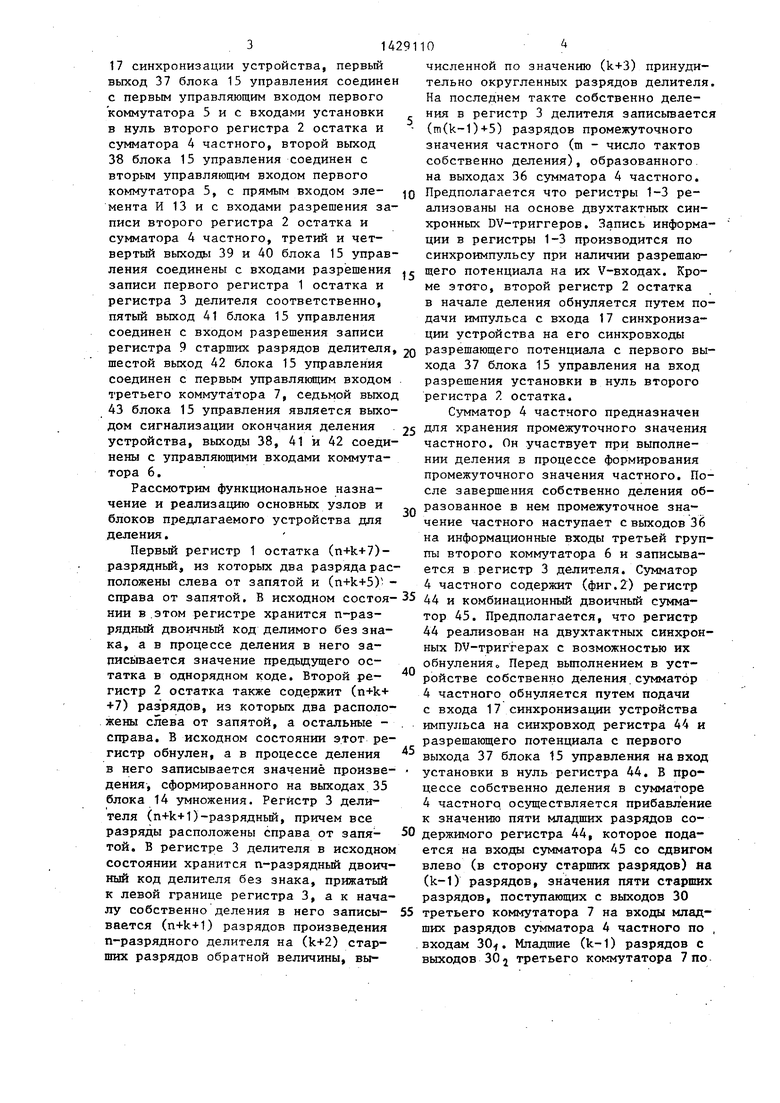

Сумматор 4 (фиг,2) содержит регистр 44 и комбинационный сумматор 4

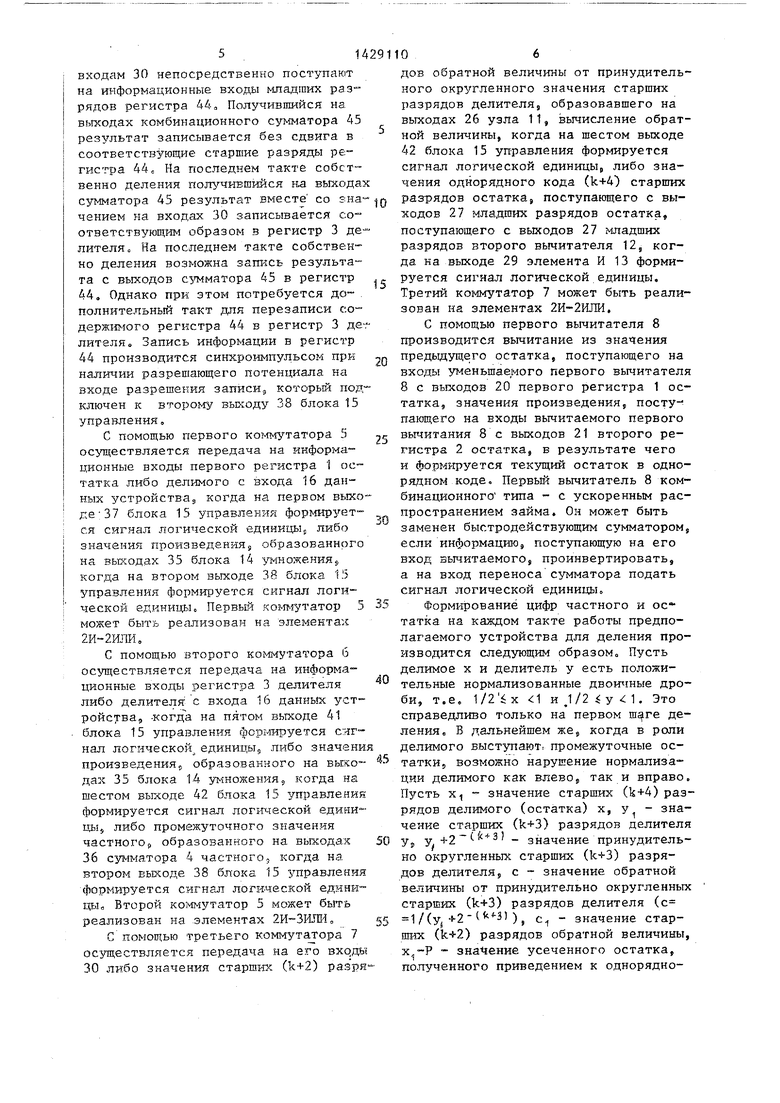

Блок 15 управления () содержит счетчик 46 и память 47 микрокоманд.

Информационные входы регистра 9 старших разрядов делителя и информа- ционные входы первой группы первого и второго коммутаторов 5 и 6 соеди-- нены с входом 16 данных УСТРОЙСТВЕ-,

0

,.

5

0

5

0

0

5

информационные, входы второй группы первого коммутатора 5 соединены с выходами 31 первого вычитателя В, выходы 32 первого коммутатора 5 соединены с информационными входами первого регистра 1 остатка, выходы 20 разрядов которого соединены с входами уменьшаемого первого вычитателя 8, входы вычитаемого которого соединены с выходами 21 разрядов второго регистра 2 остатка, выходы 24 регистра 9 старших разрядов делителя соединены с входами сз мматора 10 принудительного округления делителя, вход переноса которого соединен с входом 18 логической единицы устройства, выходы 25 сумматора 10 принудительного округления делителя соединены с входами узла 11 вычисления обратной величины, выходы 26 которого соединены с информационными входами первой группы третьего коммутатора 7, выходы 22 старших разрядов первого регистра 1 остатка соединены с входами уменьшаемого второго вычитателя 12, входы вычитаемого которого соединены с вы- ходами 23 старших разрядов второго регистра 2 остатка, вход заема второго вычитателя 12 соединен с входом 18 логической единицы устройства, выходы 27 младших разрядов второго вычитателя 12 соединены с информационными входа - ми второй группы третьего коммутатора 7, выход 28 старшего разряда второго вычитателя 12 соединен с инверсным входом элемента И 13, выход 29 которого соединен с вторым управляющим входом третьего коммутатора 7, выходы 30 которого соединены с входами младших разрядов сумматора 4 частного и с входами второй группы блока 14 умножения, выходы 35 которого являются выходом 19 частного устройства н соединены с информационными входами второй группы второго коммутатора 65 ВЫХОДЫ 30 сумматора 4 частного соединены с информационными входами третьей группы второго коммутатора 6, выходы 33 которого соединены с информационными входами регистра 3 делителЯ( выходы 34 разрядов которого соединены с входами первой группы блока 14 умножения, синхровхо- ды первого и второго регистров 1 и 2 остатка, регистра 3 делителя, регистра 9 старших разрядов делителя, сумматора 4 частного и блока 15 управления объединены и соединены с входом

31429110

17 синхронизации устройства, первый численной по значению (k+3) принуди- выход 37 блока 15 управления соединен тельно округленных разрядов делителя. с первым управляющим входом первого На последнем такте собственно деле- коммутатора 5 и с входами установки ния в регистр 3 делителя записывается в нуль второго регистра 2 остатка и - (m(k-1)-t-5) разрядов промежуточного сумматора 4 частного, второй выход значения частного (т - число тактов 38 блока 15 управления соединен с собственно деления), образованного, вторым управляющим входом первого на выходах 36 сумматора 4 частного, коммутатора 5, с прямым входом эле- Q Предполагается что регистры 1-3 ре- мента И 13 и с входами разрещения за- ализованы на основе двухтактных син- писи второго регистра 2 остатка и хронных DV-триггеров. Запись информа- сумматора 4 частного, третий и чет- ции в регистры 1-3 производится по вертый выходы 39 и 40 блока 15 управ- синхроимпульсу при наличии разрешаю- ления соединены с входами разрешения щего потенциала на их V-входах. Кро- записи первого регистра 1 остатка и ме этого, второй регистр 2 остатка регистра 3 делителя соответственно, в начале деления обнуляется путем по- пятый вьпсод 41 блока 15 управления дачи импульса с входа 17 синхрониза- соединен с входом разрешения записи ции устройства на его синхровходы регистра 9 старших разрядов делителя, 2о разрешающего потенциала с первого вы- шестой выход 42 блока 15 управления хода 37 блока 15 управления на вход соединен с первым управляющим входом разрешения установки в нуль второго третьего коммутатора 7, седьмой выход регистра 2 остатка. 43 блока 15 управления является выхо- Сумматор 4 частного предназначен дом сигнализации окончания деления 25 Д- хранения промежуточного значения устройства, выходы 38, 41 и 42 соеди- частного. Он участвует при выполне- нены с управляющими входами коммута- нии деления в процессе формирования тора 6.промежуточного значения частного. ПоРассмотрим функциональное назна- еле завершения собственно деления об- чение и реализацию основных узлов и разованное в нем промежуточное зна- блоков предлагаемого устройства для чение частного наступает с выходов 36 деления. на информационные входы третьей групПервый регистр 1 остатка (n+k+7)- пы второго коммутатора 6 и эаписыва- разрядньй, из которых два разряда рас- ется в регистр 3 делителя. Сумматор положены слева от запятой и (n+k-f5) - 4 частного содержит (фиг.2) регистр справа от запятой. В исходном состоя- 35 Д4 и комбинационный двоичный сумма- нити в .этом регистре хранится п-раз- тор 45. Предполагается, что регистр рядный двоичный код делимого без зна- 44 реализован на двухтактных синхронна, а в процессе деления в него за- ных DV-триггерах с возможностью их письгоается значение предьщущего ос- обнуления Перед выполнением в уст- татка в однорядном коде. Второй ре- ройстве собственно деления.сумматор гистр 2 остатка также содержит (n+k+ 4 частного обнуляется путем подачи +7) разрядов, из которых два располо- с входа 17 синхронизации устройства жены слева от запятой, а остальные - . . импульса на синхровход регистра 44 и справа. В исходном состоянии этот ре- разрешающего потенциала с первого гистр обнулен, а в процессе деления 5 дохода 37 блока 15 управления на вход в него записывается значение произве- установки в нуль регистра 44. В про- дения, сформированного на выходах 35 цессе собственно деления в сумматоре блока 14 умножения. Регистр 3 дели 4 частногц осуществляется прибавление теля (n+k+1)-разрядный, причем все к значению пяти младших разрядов со- разряды расположены справа от запя- 50 держимого регистра 44, которое пода- той. В регистре 3 делителя в исходном ется на входы сумматора 45 со сдвигом состоянии хранится п-разрядный двоич- влево (в сторону старших разрядов) на ный код делителя без знака, прижатый (k-1) разрядов, значения пяти старших к левой границе регистра 3, а к нача- разрядов, поступающих с выходов 30 лу собственно деления в него записы- 55 третьего коммутатора 7 на входы млад- вается (n+k+1) разрядов произведения ших разрядов сумматора 4 частного по , п-разрядного делителя на (k+2) стар- .входам 30. Младшие (k-1) разрядов с ших разрядов обратной величины, вы- выходов 30л третьего коммутатора 7 по

5U

входам 30 непосредственно поступают на информационные входы младших разрядов регистра 44 а Получившийся на выходах комбинационного сумматора 45 результат записывается без сдвига в соответствующие старшие разряды регистра 44, На последнем такте собственно деления получившийся на выхода сзтф атора 45 результат вместе со зна чением на входах 30 записывается соответствующим образом в регистр 3 де лителя. На последнем такте собственно деления возможна sam-icb результата с выходов сз мматора 45 в регистр 44, Однако при этом потребуется дополнительный такт для перезаписи содержимого регистра 44 в регистр 3 де лителя Запись информации в регистр 44 производится синхроимпульсом при наличии разрешающего потенциала на входе разрешения записИд которьм подключен к второму вькоду 38 блока 15 управления,

С помощью первого коммутатора 5 осуществляется передача на информационные входы первого регистра 1 остатка либо делимого с входа 16 данных устройствад когда на первом выхо де-37 блока 15 управления формирз ет ся сигнал логической единицы, либо значения произведенияэ образованного на выходах 35 блока 14 у гножения, когда на втором выходе 38 блока 15 управления формируется сигнал логической единицы. Первьй ком - утатор 5 может быть ре. шизован на элемента 2И--2ИШ,

С помощью второго коммутатора б осуществляется передача на информационные входы регистра 3 делителя либо делителя с входа 16 даннь х устройства, -когдЪ на пятом выходе 41 блока 15 управления форг-шруется с:яг- нал логической единицыg либо значени произведения, образованного на выходах 35 блока 1Л умножения5 когда на шестом выходе 42 блока 15 управлений формируется сигнал логической единицы, либо промежуточного значения частного9 образованного на выходах 36 суь-матора 4 частного, когда на. втором выходе 38 блока 15 управления формируется сигнал логической единицы,, Второй ко 1мутатор 5 может быть реализован на элементах 2H-3HJffl,

С помощью третьего коммута/гора 7 осуществляется передача на его входы 30 либо значения старших (k+2) раз ря

5

5

91

,Q

0

0

5

106

дов обратной величины от принудительного округленного значения старших разрядов делителя, образовавшего на выходах 26 узла 11, вычисление обратной величины, когда на шестом выходе 42 блока 15 управления формируется сигнал логической единицы, либо значения однорядного кода (k+4) старших разрядов остатка, поступающего с выходов 27 младших разрядов остатка, поступающего с выходов 27 младших разрядов второго вычитателя 12, когда на выходе 29 элемента И 13 формируется сигнал логической единицы. Третий коммутатор 7 может быть реализован на элементах 2И-2ИЛИ,

С помощью первого вычитателя 8 производится вычитание из значения предьщущего остатка, поступающего на входы уменьшаемого первого вычитателя 8 с выходов 20 первого регистра 1 остатка, значения произведения, поступающего на входы вычитаемого первого вычитания 8с выходов 21 второго регистра 2 остатка, в результате чего и форм фуется текущий остаток в однорядном коде. Первьй вычитатель 8 комбинационного типа - с ускоренным распространением займа. Он может быть заменен быстродействующим сумматором, если информацио, поступающую на его вход вычитаемого, проинвертировать, а на вход переноса сз мматора подать сигнал логической единицы.

Формирование цифр частного и татка на каждом такте работы предполагаемого устройства для деления производится следующим образомо Пусть делимое х и делитель у есть положительные нормализованные двошшые дроби, т.е. :1 . Это справедливо только на первом деления, В дальнейшем же, когда в роли делимого выступают, промежуточные остатки, возможно нарушение нормализации делимого как влево, так и вправо. Пусть х значение старших (k+4) разрядов делимого (остатка) х, у - значение старших (k+3) разрядов делителя У;, у - значение принудительно округленных старших (k+3) разрядов делителя5 с - значение обратной величины от принудительно округленных старших (k+3) разрядов делителя (с 1/(У(+2 З ) , с - значение старших (k+2) разрядов обратной величины, X -Р - значение усеченного остатка, по.лученного приведением к однорядно7

му коду старших разрядов двухрядного кода остатка, где , если в старших разрядах остатка х при приведении его к однополярному коду придет заем из младших разрядов, и ( если не придет, Р - величина, на которую отличается значение усеченного остатка, полученного приведением к однорядному коду старших разрядов д двухрядного кода остатка и принудительно уменьшенное на единицу младшего разряда во втором вычитателе 12, от значения старших разрядов остатка, получаемого приведением к однорядному коду всех разрядов двухрядного кода остатка в первом вычитателе 8. На подготовительном этапе деления формируется произведение делителя у на значение старших (k+2) разрядов об- JQ ратной величины c,(,). При выполнении собственно деления следующий остаток вычисляется по формуле х x-W X,. Параллельно с вычислением остатка в сумматоре 4 частного про- 25 изводится накапливание промежуточного значения частного х , являющегося суютой всех (Xj-Р), полученных на каждом такте работы устройства и свину- тых относительно друг друга Ha(k-l) разрядов. После выполнения собственно деления .значение х зт-(ножается на значение с. Старшие п разрядов этого произведения и являются значением частного Z.

В устройстве не формируется произ- 35 ведение на каждом такте работы, а производится накапливание промежуточного значения частного как суммы значений (), полученных на каждом такте работы устройства, которое ум- ножается на значение с после вьтол- нения собственно деления. Абсолютная погрешность конечного результата будет меньше либо равна единице младше- го разряда с весом .

Регистр 9 старших разрядов делителя (k+3) разрядный и предназначен для хранения у, старглнх (k+3) разрядов делителя у без знака. Предполагается, что регистр 9 старших разрядов 50 делителя реализован на основе двухтактных синхронных DV-триггеров. Запись информации в регистр производится по синхроимпульсу при наличии разрешающего потенциала на его V-входах.55

Сумматор 10 принудительного округления делителя является комбинационной схемой. В нем осуществляется при30

91

дJQ 25 35

5055

30

10-8

нудительное округление значения старших (k+3) разрядов делителя у путем .прибавления единицы в его младший разряд, поступающий на вход переноса сумматора 10 принудительного округления делителя через вход 18 логической единицы устройства (т.е. в сумматоре 10 вычисляется значение + ). На выходах 25 сумматора 10 образуется значение старших разрядов делителя, увеличенное на единицу раз- ряда. Этим самым устраняется возможность получения на выходе 19 частного устройства частного с избытком.

Уз-ел 11 вычисления обратной величины производит вычисление значения старших (k+2) разрядов обратной величины с от принудительно округленного значения старших разрядов делителя, поступающего на входы узла 11с выходов 25 сумматора 10 принудительного определения делителя. На выходах 26 узла 11 вычисления обратной величины формируется значение старших (k+2) разрядов обратной величины принудительно округленного усеченного делителя. Узел 11 вычисления обратной величины может быть реализован любым из известных методов. В данном случае предполагается его реализация совместно с сумматором 10 принуди тельного округления делителя на ПЗУ.

Второй вычитатель 12 комбинационного типа осуществляет преобразование (k+5) старших разрядов двухрядного кода остатка, хранимого в регистрах 1 и 2 остатка, в однорядный код (два разряда слева от запятой и(k+3) разряда справа от запятой). При этом во втором вычитателе 12 осуществляется принудительное уменьшение значения усеченного остатка на единицу младшего разряда, поступающего на вход займа второго вычитателя через вход 18 логической единицы устройства, и формируется значение х,-Р. На выходах

27младших разрядов второго вычитателя 12 образуется однополярный код (k+4) старших разрядов остатка (один разряд слева от запятой и (k+3) разряда справа от запятой), а на выходе

28старшего разряда второго вычитателя 12 образуется старший разряд остатка. Так как в устройстве при формировании частного используются старшие разряды остатка, полученные при приведении на втором вычитателе 12

к однорядному коду старших разрядов

91

двухрядного кода остатка и принудительно уменьшенные, на единицу младшего разряда, то становится возможным образование неправильного значения частного. Так, если значение старших разрядов приведенного остатка, полученного на выходах 31 первого вычи- тателя 8, равно нулю, то при формировании однорядного кода старших разрядов остатка путем приведения к однорядному коду старших разрядов двухрядного кода остатка и принудительного уменьшения на единицу младшего разряда, возможно получение значения разности на выходах 27 младших разрядов вычитателя 12 меньшего чем нуль на единицу младшего разряда, т.е. значения 1, 1 ... 1. Но в этом случае на выходе 28 старшего разряда второго вьиитателя 12 формируется единица, а в случае, если значение старших разрядов приведенного остатка, полученного на выходах 31 первого вычитателя 8, не равно нулю, на выходе 28 старшего разряда второго вычитателя 12 формируется логический нуль. Для исключения возможности получения в первом случае неверного значения частнЪго в устройстве предусмотрена блокировка (формирование значения старших разрядов остатка равного нулю). Это производится путем подачи на инверсный вход элемента И 13 единичного сигнала с выхода 28 старшего разряда второго вычитателя 12, В этом случае на выходе 29 элемента И 13, не зависимо от значения сигнала на его прямом , формируется сигнал логического нуля, который запрещает прохождение значение с информационных входов второй группы третьего коммутатора 7 на его выходы 30 (формируется .значение 0,0,с„ 0). В случае, когда на инверсный вход элемента И 13 подается сигнал логического нуля с выхода 28 старшег разряда второго вычитателя 12, а на прямой вход элемента И 13 подается сигнал логической единицы с второго выхода 38 блока 15 управления, значе ние старших разрядов остатка с информационных входов второй группы третьего коммутатора 7 поступает на его выходы 30.

Блок 14 з множения производит ум ножение содержимого регистра 3 делителя на значение величины, сформир,о- ванной на выходах 30 третьего комму

0

5

0

5

9

0

5

0

5

0

5

татора 1, На его выходах 35 образуется произведение в однорядном коде. Блок 14 умножения комбинационного типа может быть разработан хорошо известными методами и средствами.

Блок 15 управления координирует работу узлов и блоков устройства при выполнении в нем операции деления чисел. Он может быть реализован самыми различными методами и средствами. На фиг.З в качестве примера приведена реализация блока 15 на основе счетчика 46 и памяти 47 микрокоманд. Счетчик 46 накапливающего типа предназначен для естественной адресации микрокоманд. Вход счета счетчика 46 соединен с входом 17 синхронизации устройства. В качестве памяти 47 микрокоманд может быть применена быстродействующая постоянная память емкостью (М+3)х75 где . В самом

начале работы устройства счетчик 46 устанавливается в некоторое исходное состояние, например в нуль (на фиг.З цепь установки счетчика 46 в исходное состояние не показана). Микропрограмма работы устройства представлена на фиг,4.

Устройство для деления работает следующим образом.

Пусть на вход 16 данного устройства уже поступил п-разрядный двоичный код делителя у (здесь предполагается, что делимое х и делитель у - правильные нормализованные положительные дроби), а счетчик 46 блока 15 управления установлен в исходное нулевое состояние. По содержимому счетчика 46, которое служит адресом обращения к памяти 47 микрокоманд блока 15, из памяти 47 микрокоманд считывается микрокоманда 1, которой соответствуют управляющие сигналы Y 40 и Y 41 (фиг,4)в В результате этого соответственно на четвертом и пятом входах 40 и 41 блока 15 управления устанавливаются зфовни логической единицы. Под действием этих управляющих сигналов второй коммутатор 6 пропускает на информационные входы регистра 3 делителя делитель у с входа 16 данных устройства, а регистр 3 делителя и. регистр 9 старших разрядов делителя подготовлены к приему информации, так как на их входах разрешения записи, присутствуют потенциалы логической единицы. С приходом первого импульса

II14

на вход 17 синхронизации устройства производится запись двоичного кода делителя у в регистр 3 делителя и двоичного кода старших разрядов делителя у в регистр 9 старших разрядов делителя, а также установка счетчика 46 блока 15 управления в состояние 1. С момента окончания синхроимпульса заканчивается первый такт ра- боты устройства.

Во втором такте работы устройства из памяти 47 микрокоманд считывается микрокоманда 2, которой соответствуют управляющие сигналы Y 37, Y 39, Y 40 Y 42 (фиг.4). В результате этого со ответственно на первом, третьем, четвертом и шестом выходах 37, 39, 40 и 42 блока 15 управления устанавливаются уровни логической единицы. Под действием этих управляющих сигналов первый коммутатор 5 пропускает на информационные входы регистра 1 делимое ,х с входа 16 данных устройства, первый регистр . 1 остатка подготовлен к приему информации, третий коммутатор 7 пропускает, на входы второй группы блока 14 умножения значение старших разрядов обратной величины с., сформированной на выходах 26 узла 11 вычисления обратной величины по значению принудительно округленных в сумматоре 10 принудительного округления делителя старших разрядов делителя у , хранящихся в регистре 9 старших разрядов делителя. На выходах 35 бло- ка 14 умножения формируется произведение п-разрядного делителя у на значение с (.у). Под действием управляющего сигнала с выхода 42 блока 15 управления второй коммутатор 6 пропускает на информационные входы регистра 3 делителя значение этого произведения w с выходов 35 блока 14 умножения. Под действием управляющего .сигнала с выхода 40 блока 15 управления регистр 3 делителя подготовлен к приему информации. Кроме этого, сумматор 4 частного и второй регистр 2 остатка настроены на обнуление. С приходом второго импульса на вход 17 синхронизации устройства производится запись двоичных кодов делимого х и произведения w в регистры соответственно 1 и 3, а также обнуление сумматора 4 частного, второго регистра 2 остатка и установка счетчика 46 блока 15 управления в состояние 2. С момента окончания действия второго

г 0 5 5 0 5

0

101 2

.импульса на входе 17 синхронизации устройства заканчивается второй такт и вместе с ним подготовительный этап работы устройства и начинается собственно деление, в процессе которого в течение m тактов формируется (m(k-l)-i- +5) двоичных цифр промежуточного значения частного.

В первом такте собственно деления из памяти 47 микрокоманд считьгоается микрокоманда Зр которой, соответствуют управляющие сигналы Y 38, Y 39 и соответственно на втором и третьем выходах 38 и 39 блока 15 управления устанавливаются уровни логической единицы. Под действием этих управляющих сигналов первьй коммутатор 5 пропускает на информационные входы первого регистра 1 остатка результат с вьосодов 31 вычитателя 8, первый и второй регистры 1 и 2 остатка и сумматор 4 частного подготовлены к приему информации. Если сигнал на выходе 28 старшего разряда второго вычитателя 12 соответствует уровню логического нуля, то, так как на прямом выходе элемента И 13 присутствует единичный сигнал с выхода 38 блока 15 управления, третий коммутатор 7 пропускает на входы второй группы блока 14 умножения значение старших разрядов остатка х.,-Р с выходов 27 младших разрядов второго вычитателя 12. Если сигнал на выходе 28 старшего разряда второго вычитателя 12 соответствует уровню логической единицы, то третий коммутатор 7 формирует на входах второй группы блока 14 ум ножения значение, равное нулю. Это позволяет произвести в предлагаемом устройстве следующие вычисления. На выходах 35 блока 14 умножения формируется произведение величины , хранящейся в регистре 3 делителя и пЪступающей на входы первой группы блока 14 умножения с выходов 34 разрядов регистров 3 делителя, на значение старших разрядов остатка (х,-Р), поступающих на входы второй группы блока 14 и формируемых во втором читателе 12 по значению старших разрядов двухрядного кода остатка и поступающих на входы уменьшаемого и вычитаемого второго вычитателя с выходов 22 и 23 старших разрядов соответственно регистров 1 и 2 остатка, При этом во втором вычитателе 12 производится принудительное уменьшение

13

I значения старших.разрядов остатка I на единицу младшего разряда Врезуль тате этого на выходах 35 блока 14 ум I ножения образуется значение () : ху-с. Следующий остаток х формиру- I ется в двухрядном коде (в виде двух чисел), первое - предыдущий остаток ; X, формируемый в однорядном коде на j выходах 31 первого вьг4итателя 8, втоI рое - произведение ()-у.С|, фор- I мируемое на выходах 35 блока 14 ум- I ножения. Значение текущего остатка I X и произведение ()-у-С| посту- I пает соответственно на информацион- I ные входы второй группы первого ком I мутатора 5 и информационные входы I второго регистра 2 остатка со сдви- I гом на (k-1) разрядов в сторону его I старших разрядов. Параллельно с работой блока 1Д умножения и первого вычитателя 8 значение старших разрядов остатка поступает на информационные входы младших разрядов сумматора 4 частного с выходов 30 тре- тьего коммутатора 7 и подсуммируются к младшим разрядам содержимого сумматора 4 частного, сдвигутому на (k-1) разрядов в сторону его старших разрядов (на первом такте собственно деления в устройстве сумматор частного 4 обнулен), В результате в регистре 44 сумматора 4 частного накапливается промежуточное значение частного х , как сумма (х ,-Р) полученных на каждом такте собственно деления и сдви- нутых относительно друг друга на (k-1) разрядово С приходом третьего импульса на вход 17 синхронизации устройства в первый регистр 1 остатка запи сьшается значение предьдущего остат- ка, сформированное на выходах 31 первого вычитателя В, во второй регистр 2 остатка записывается значение произведения (xj,-P)-у-с 5 сформированное на выходах 35 блока 14 умножения, в регистр 44 сумматора 4 частного заносится результат сумматора 45 вместе со значением величины на шине 30, а счетчик 46 блока 15 управления устанавливается в состояние 3. На этом третий такт работы устройства заканчивается,

Аналогичныим образом устройство работает и в других тактах собственно деления. Отметим только, что на последнем такте собственно деления (микрокоманда на фиг.4) значение накопленной суммы х с выходов 36

15

20

- ю 25. 35 45 50

55

2911014

сумматора 4 частного поступает на информационные входы третьей группы второго коммутатора 6, который под действием управляющего сигнала с выхода 38 блока 15 управления пропускает значение х на информационные входы регистра 3 делителя. Регистр 3 делителя под действием управлякщего сигнала с выхода 40 блока 15 управления подготовлен к приему информации. С приходом импульса с входа 17 синхронизации устройства промежуточное значение частного х с выходов 36 сумматора 4 частного записьгоается в регистр 3 делителя, а счетчик 46 блока 15 управления устанавливается в состояние т+2.

На последнем (т+3) такте деления из памяти 47 микрокоманд считывается микрокоманда m-4-З, которой соответствуют управляющие сигналы Y 42, Y 43 и соответственно на шестом и седь- , мом выходах 42 и 43 блока 15 управления устанавливаются уровни логической единицы. Под действием этик управляющих сигналов третий коммутатор 7 пропускает на входы второй группы блока 14 умножения значение старших разрядов обратной величины с о На выходах 35 блока 14 зт ножения формируется произведение х с, старшие п разрядов которого являются значением частного Z и поступают на выход 19 частного устройства. При этом уровень логической единицы, установленньй на седьмом выходе 43 блока 15 управления, сигнализирует об окончании операции деления в устройстве.

Формула изобретения

I

Устройство для деления, содержащее первый регистр остатка, регистр делителя, сумматор частного, первый, второй и третий коммутаторы, первый вычитатель, регистр старших, разрядов делителя, сумматор принудительного округления делителя, узел вычисления обратной величины, блок умножения и блок- управления, причем информационные входы регистра старших разрядов делителя и информационные входы первой группы первого и второго коммутаторов соединены с входом данных устройства, информационные входы второй группы первого коммутатора сое - динень с, выходами первого вычитателя, выходы первого коммутатора соединены

30

5142

с информационными входами первого регистра остатка, выходы разрядов которого соединены с входами уменьшаемого первого вьгчитателя, выходы блока умножения являются выходом частного устройства и соединены с информационными входами второй группы второго коммутатора, информационные входы третьей группы которого соединены с выходами сумматора частного, выходы второго коммутатора соединены с информационными входами регистра делителя, выходы разрядов которого соединены с входами первой группы блока умножения, выходы разрядов регистра старших разрядов делителя соединены с входами сумматора принудительного округления делителя, вход переноса

которого соединен с входом логичес-г

кой единицы устройства, выходы разрядов сумматора принудительного округления делителя соединены с входами узла вычисления обратной величины, выходы которого соединены с информа- ционными входами первой группы третьего коммутатора, синхровходы первого регистр а остатка, регистра делителя, регистра старших разрядов делителя, сумматора частного и блока управления соединены с входом синхрони зации устройства, первьй выход блока управления соединен с первым управляющим входом первого коммутатора и с входом установки в О сумматора частного, второй выход блока управлеНИН соединен с вторым управляющим входом первого кoм fyтaтopa, с первым управлякяцим входом второго коммутатора и с входом разрешения записи сумматора частного, третий и четвер- тый выходы блока управления соединены с входами разрешения записи первого регистра остатка и регистра делителя соответственно, пятый выход блока управления соединен с входом

л

5

0

, 5 5

101 6

разрешения записи регистра старших разрядов делителя и с вторым управляющим входом второго коммутатора, шестой выход блока управления соединен с третьим управляющим входом второго коммутатора и с первым управляющим входом третьего коммутатора, седьмой выход блока управления является выходом сигнализации окончания деления устройства, отличающееся тем, что, с целью повыщения быстродействия, устройство содержит второй регистр остатка, второй вычитатель и элемент И, причем выходы блока . умножения соединены с информационными входами второго регистра остатка, выходы разрядов которого соединены с входами вычитаемого первого вычита- теля, выходы старших разрядов первого регистра остатка соединены с входами уменьшаемого второго вычитателя, входы вычитаемого которого соединены с выходами старших разрядов второго регистра остатка, вход заема второго вычитателя соединен с входом логической единицы устройства, выходы младших разрядов второго вычитателя соединены с информационными входами второй группы третьего коммутатора, второй управляющий вход которого соединен с выходом элемента И, инверсный вход которого соединен с выходом старшего разряда второго вычитателя, а прямой вход с вторым выходом блока управления, выходы третьего коммутатора соединены с входами второй группы блока умножения и с входами младших разрядов сумматора.частного, входы установки в О и разрешения записи второго регистра остатка соединены с входами установки в О и разрешения записи сумматора частного соответственно, синхровход второго регистра остатка соединен с входом синхронизации устройства.

Л да J5 «3

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1988 |

|

SU1541598A1 |

| Устройство для деления чисел | 1988 |

|

SU1580353A1 |

| Устройство для деления | 1986 |

|

SU1425657A1 |

| Устройство для деления | 1990 |

|

SU1728862A1 |

| Устройство для деления чисел | 1985 |

|

SU1247862A1 |

| Устройство для деления | 1985 |

|

SU1322264A1 |

| Устройство для деления | 1985 |

|

SU1357946A1 |

| Устройство для деления | 1986 |

|

SU1390608A1 |

| Устройство для деления чисел | 1985 |

|

SU1429109A1 |

| Устройство для деления | 1984 |

|

SU1249551A1 |

Изобретение относится к области вычислительной техники и может быть применено в быстродействующих вычислительных устройствах для вьтолнения операции деления чисел. Целью изобретения является повышение быстродействия устройства. Устройство для деления содержит два регистра 1,2 остатка, регистр 3 делителя, сумматор 4 .частного, три коммутатора 5,6,7, два вычитателя 8,12, регистр 9 старших разрядов делителя, сумматор 10.. принудительного округления делителя, узел 11 вычисления обратной величины, блок 14 умножения, блок 15 управления и элемент И 13. Цель достигается за счет введения в устройство второго регистра остатка, второго вычитателя, § элемента И и соответствующей системы связи. 4 ил.

f,m-f moffmS

| Карцев М.А | |||

| Арифметика цифровых машин - М.: Наука, 1969, с.494, рис.5-1 | |||

| Патент США ( 3234367, кл | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Водоотводчик | 1925 |

|

SU1962A1 |

| Устройство для деления | 1986 |

|

SU1390608A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-10-07—Публикация

1986-07-29—Подача