(54) ФУНКЦИОНАЛЬНЫЙ ПРЕСВРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь | 1977 |

|

SU744639A1 |

| Функциональный преобразователь | 1979 |

|

SU842852A1 |

| Функциональный преобразователь | 1980 |

|

SU894748A1 |

| Вичислительное устройство | 1979 |

|

SU783804A1 |

| Вычислительное устройство | 1982 |

|

SU1040493A1 |

| Устройство для воспроизведения переменных во времени коэффициентов | 1980 |

|

SU894737A1 |

| Устройство для воспроизведения переменных во времени коэффициентов | 1981 |

|

SU1005087A1 |

| Устройство для воспроизведения периодических сигналов | 1983 |

|

SU1130881A1 |

| Вычислительное устройство | 1981 |

|

SU1001114A1 |

| Устройство для воспроизведения переменных во времени коэффициентов | 1980 |

|

SU894738A1 |

Изобретение относится к аналогоцифровой и вычислительной технике. Известен функциональный гфеобразователь, содержащий генератор импульсов счетчик, дешифратор, генератор пилообразного на1фяжения, компаратор, блок переменного коэффициента усиления и Выходной усилитель, фильтр Недостатки этого преобразователи пониженная точность формирования вос1фОЕЗведення функции одной переменной на вторую переменную и сложность схемы. Известен функциональный 1 реобразова тель, содержащий блок цифроаналогового умножения, вых:одной усилитель-фильтр, генерагсф импульсов, подключенный выходом Е входу тактовых. импульсов блока линейной скважности, блок аналого- хифро вого 1феобразования, вход которого пер- вым входом функционального щ еобразова теля, а выходы старших разрядов подключены к входам дешифратора адреса, соединенного выходами с адресными вхсм дам и блока памяти, вторые входы блока Ьамяти являются вторым входом функционального щ)еобразователя, а выходы блок памяти соединены с вхсцами выходного усилителя-фильтра, выход блока ии роаналоговрго преобразования, соединенного цифровыми вхрдамЕ с разрядными выходами, блока аналого-цифрового преобразования, подключен к первому входу сумматора, второй вход которого соединен с входом блока авалого -цифрового хфёобразования, а выход подключен к входу , управления скважностью блока линейной скважности, соединенного;выходом с входом управления считыванием дешифратора 2. : Недостатками указанного цреобразователя являются пониженная точность формирования Щ)оизведенин функций одной переменной на вторую переменную, обус ловленная, в чаЬгности ; аналоговой представления, ординат узлов аппроксимации и выполнением операции умножения на вторую переменную путем из

менения напряжения на вторых входах блока памяти, а также большие аппаратурные затраты.

Наиболее близким техническим решением к Щ)едлагаемому является функциональный преобразователь, содержащий блок памяти, первый и вторые блоки ци роаналогового умножения, аналоговые входы, которых соединены и я аляются первым входом преобразователя, выходной усилитель-фильтр, выход которого является выходом преобразователя, генератор импульсов, подключенный выходом к входу тактовых импульсов блока линей ной скважности, дешифратор адреса, выходы которого соедийены с адресными входами блока памяти, блок аналого-цифрового преобразования, вход которого является вторым входом функционального преобразователя, выходы старших разрядов подключены к входам дешифратора айреса, а выходы младших разрядов - к входам управления скважностью блока линейной скважности, две группы элементов И, инвертор, цифровые входы первого и второго блоков цифроаналогового умножения подключены к выходам первой и второй групп элементов И соответственно, выход блока линейной скважности подключен к первым входам элементов И первой группы и к входу инвертора, выход которого подключен к первым Входам элементов И второй группы, вторые входы элементов И обеих групп соединены с выходами блока памяти, выходы Первого и второго блоков, цифроаналогового умножения подключены, к входу усилителя-фильтра З.

Недостатками предлагаемого преобразователя являются пониженное быстродействие в связи с время-импульсным управлением подачей кодов узловых ординат заданной функции на цифровые входы блоков цифроаналогового умножени

Цель изобретения - повышение быстродействия.

Поставленная цель достигается тем, что функциональный прео-бразователь, содержшиий блок памяти, первый и второ блоки цифроаналогового умножения, аналоговые входы которых соединены и являются первым входом преобразователя, Выходной усилитель-фильтр, выход которого является выходом преобразователя, генератор импульсов, подключенный выходом к входу тактовых импульсов блока линейной скважности, дешифратор адреса, выходы которого соединены с адресным

входами блока памяти, блок аналогоцифрового преобразования, вход которо1Х является вторым входом функционального преобразователя, и выходы старших разрядов подключены к входам дешифратора адреса, а выходы младших разрядов к входам управления скважностью блока линейной скважности, инвертор, подключеный входом к выходу блока линейной скважности, дополнительно содержит первый и второй ключи, информационные входы которых соединены соответственно с выходами первого и второго блоков цифроаналогового. умножения, управляюшие входы - соответственно с выходами блока линейной скважности и инвертора, а выходы - с входом усилителя-фильтра, цифровые входы первого и второго блоков цифроаналогового умножения соединены с выходами блока памяти.

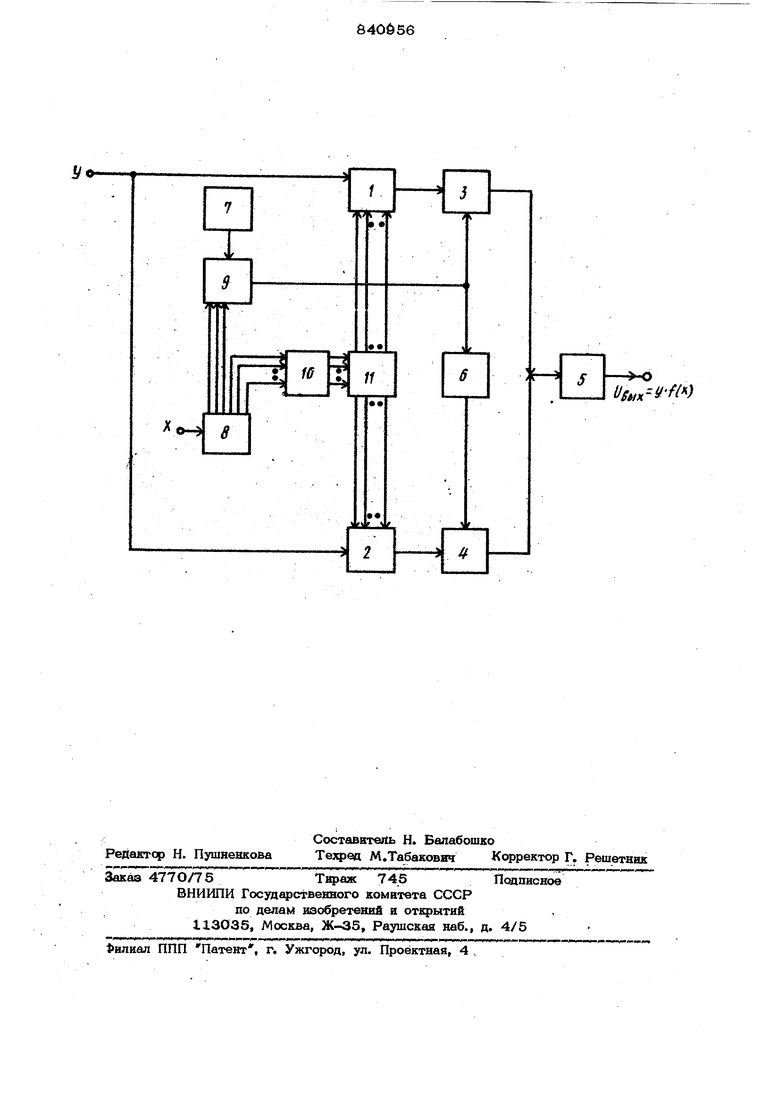

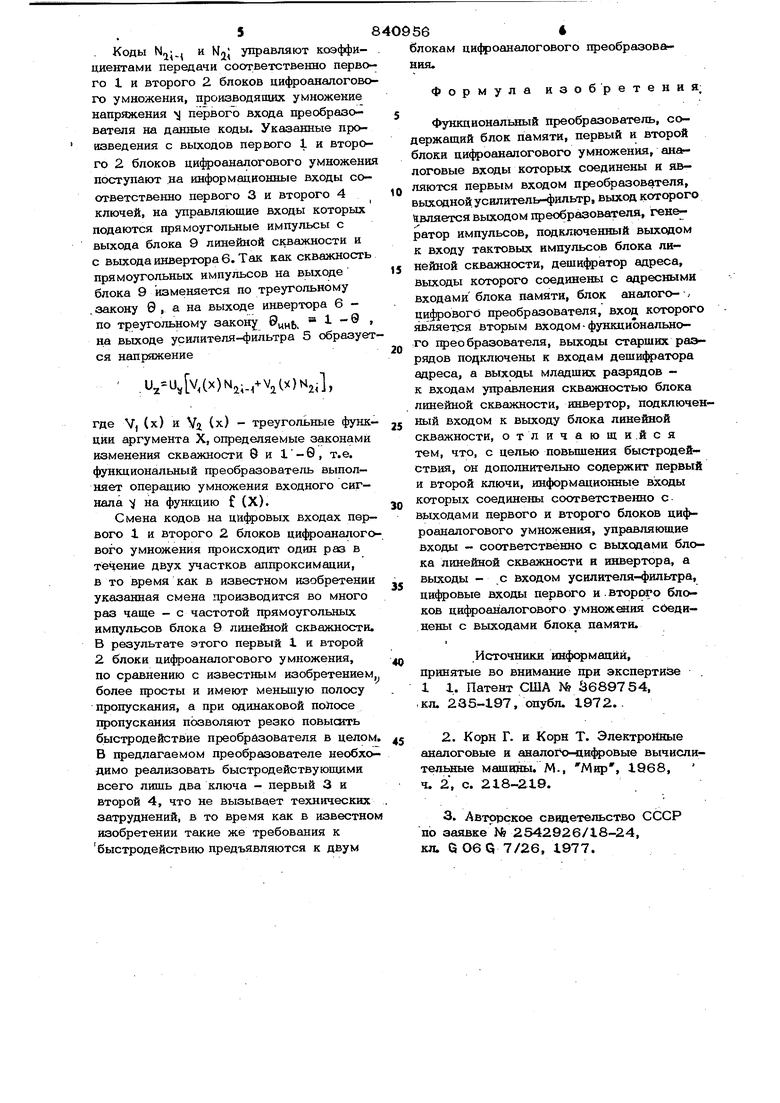

На чертеже представлена блок-схема преобразователя.

Функциональный преобразователь содержит первый 1 и второй 2 блоки цифроаналогового умножения, первый 3 и второй 4 ключи, выходной усилитель-фильтр 5, инвертор 6, генератор 7 импульсов, блок 8 аналого-цифрового пресбразования блок 9 линейной скважности, дешифратор 10 адреса, блок И памяти.

Функциональный преобразователь работает следующим образом.

Аргумент X воспроизводимой функции f (х) в аналоговой форме со второго входа преобразователя поступает на вход блока 8 аналого-цифрового преобразователя, с выхода которого в цифровой форме младшими разрядами поступает на входы управления скважностью блока 9. Блок 9 линейной скважности преобразует аргумент X в прямоугольные импульсы, скважность которых Э изменяется от X по треугольному закону, а частота следования определяется генератором 7 импулсов. С выхода блока 8 аналого-цифрового преобразования старшие разряды преобразованного аргумента X через дешифратор. 1О адреса управляют работой блока 11 памяти таким образом, что на первом и втором его выходных регистрах появляются поочередно нечетные четные Nj; коды ординат узлов аппроксимации функции f (х). При этом смена кодов происходит в моменты достижения аргументов X значений а кодов - при достижении значений X Х , i 1, 2, ... Коды . и MjJ управляют коэффициентами передачи соответственно перво го 1 и второго 2 блоков цифроаналогово го умножения, производящих умножение напрякения первого входа преобразователя на данные коды. Указанные произведения с выходов первого 1 и второго 2 блоков цифроаналогового умножени поступают на информационные входы соответственно первого 3 и Второго 4 ключей, на управляющие входы которых подаются прямоугольные импульсы с выхода блока 9 линейной скважности и с выхода инвертора 6. Так как скважность прямоугольных импульсов на выходе блока 9 изменяется по треугольному закону 9 , а на выходе инвертора 6 по треугольному закону 0цнЬ. 1 -® на выходе усилителя-фильтра 5 образует ся напряжение ())Н,1, где V, (х) и Vi (х) - треугольные функции аргумента X, определяемые законами изменения скважности 8 и 1-0, т.е. функциональный преобразователь выполняет операцию умножения входного сигнала i на функцию С (х). Смена кодов на цифровых входах первого 1 и второго 2 блоков цифроаналого вого умножения происходит один раз в течение двух участков аппроксимации, в то время как в известном изобретении указанная смена производится во много раз чаще - с частотой прямоугольных импульсов блока 9 линейной скважности. В результате этого первый 1 и второй 2 блоки цифроаналогового умножения, по сравнению с известным изобретением, более просты и имеют меньшую полосу пропускания, а при одинаковой полосе пропускания позволяют резко повысить быстродействие преобразователя в целом В предлагаемом преобразователе необхо димо реализовать быстродействующими всего лшиь два ключа - первый 3 и второй 4, что не вызывает технических затруднений, в то время как в известном изобретении такие же требования к быстродействию предъявляются к двум блокам цифроаналогового преобразованвя. Формула изобретения. Функциональный преобразователь, содержащий блок памяти, первый и второй блоки ци(оаналогового умножения, аналоговые входы которых соединены я являются первым входом преобразователя, выходной усилитель-фильтр, выход которого Является выходом преобразователя, генератор импульсов, подключенный выходом к входу тактовых импульсов блока линейной скважности, дещифратор адреса, выходы которого соединены с адресными входами блока памяти, блок аналого- , цифровогЬ преобразователя, вход которого является вторым входом - функционального преобразователя, выходы старших разрядов подключены к входам дещи4 атора адреса, а выходы младших разрядов - к входам упр 1Вления скважностью блока линейной скважности, инвертор, подключенный входом к выходу блока линейной скважности, отличающийся тем, что, с целью повьщ1ения быстродействия, он дополнительно содержит первый и второй ключи, информационные входы которых соединеШ) соответственно с выходами первого и второго блоков цифроаналогового умножения, управляющие входы - соответственно с выходами блока линейной скважности и инвертора, а выходы - ,с входом усилителя-фильтра, цифровые входы первого и . второго блоков цифроаналогового умножения соединены с выходами блока памяти. .Источники инфсфмадйй, принятые во внимание при экспертизе 1 1. Патент США № 3689754, ,кл. 235-197, опубл. 1972., 2.Корн Г. и Корн Т. Электронные аналоговые и аналого-цис овые вычислительные мащвды. М., Мир, 1968, ч. 2, с. 218-219. 3.Авторское свидетельство СССР по заявке № 2542926/18-24, кл. G Об Q 7/26, 1977.

I

Iff

b-5

lisuK yff

i s t

Авторы

Даты

1981-06-23—Публикация

1979-09-13—Подача