Изобретение относится к аналоговой :И аналого-цифровой -вычислительной технике.

Известно устройство для воспроиз- ведения переменных во времени напряжений, содержащее генератор импульсов, блок управления, управляемый дели.тель частоты, счетчик, блок памяти, цифро-аналоговые преобразователи, инвертор, сумматор, коммутатор и многоканальный запоминающий блок fl.

Недостатком устройства является ограниченная область применения, так как оно не позволяет формировать произведения независимых переменных на переменные во времени напряжения.

Наиболее близким к предлагаемому является устройство для воспроизведения переменных во времени козффициентов, содержащее генератор импульсов, подключенный выходом к первому входу основного элемента И и к счетному входу первого счетчика, соединенного выходом старшего разряда со счетным входом второго счетчика, подключенного выходами разрядов к первой группе входов первого дешифратора, соединенного выходами с входами блока памяти, подключенного зна ковым выходом к входу триггера знака, а цифровыми выходами - к первой, группе входов преобразователя код частота, соединенного второй группой входов с выходами разрядов первого счетчика, а выходом - с вторым входом основного элемента И, подключенного выходом к счетному входу реверсивного счетчика, соединенного входом управления реверсом с выходом

10 триггера знака, причем выходы разрядов первого и второго счетчиков подключены к первой группе входов блока сравнения кодов, второй дешифратор, п злементов И, элемент за15держки, третий счетчик и счетчик по модулю п, соединенный выходами раэрядов с второй группой входов первого дешифратора и с входами второго дешифратора, каждый i-ый (l i «n)

20 выход которого подключен к первому входу i-ro элемента И, соединенного вторым входом с выходом блока сравнения кодов, подключенного второй группой входов к выходам разрядов

25 третьего счетчика, соединенного счетным входом с выходом старшего разряда счетчика по модулю п, псэдключенного счетным входом к выходу старшего разряда второго счетчика, причем

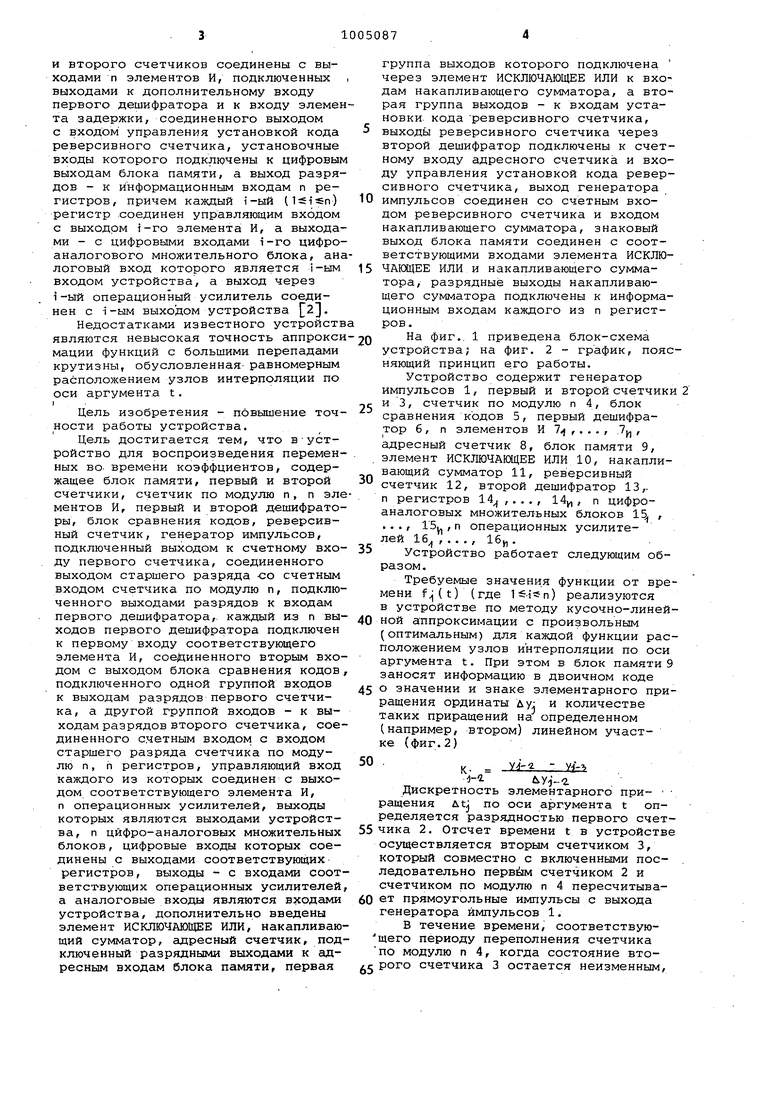

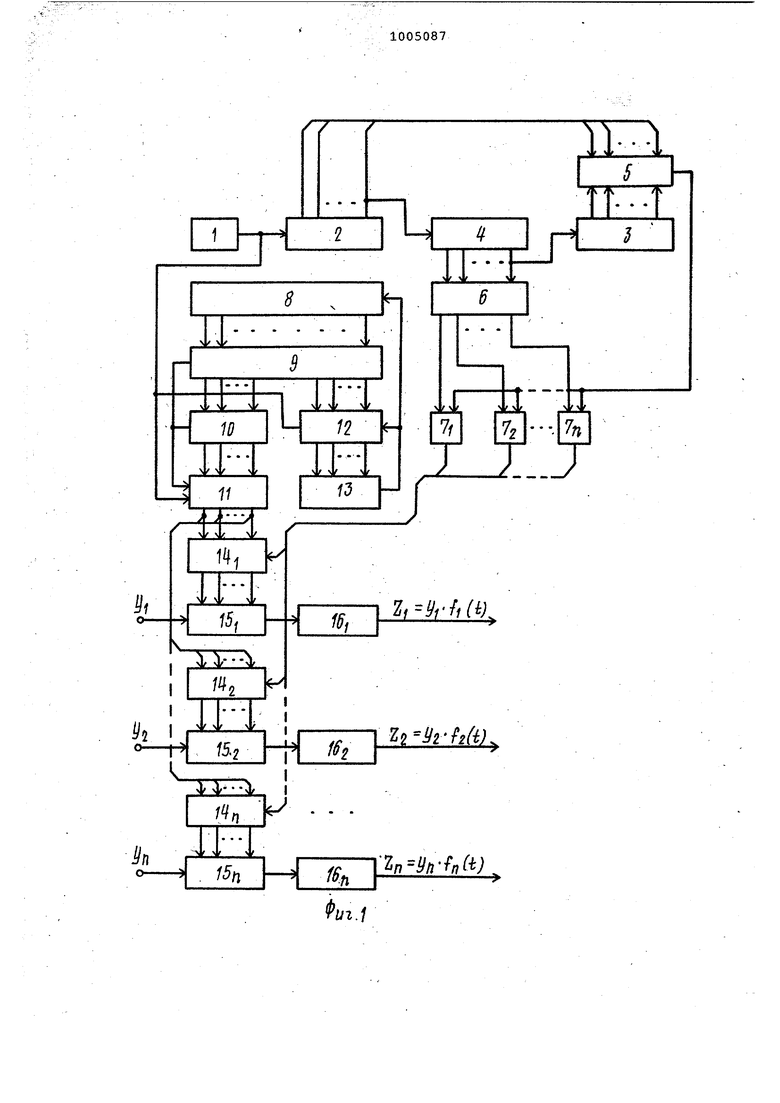

30 инверсные выходы разрядов первого и второго счетчиков соединены с выходами п элементов И, подключенных выходами к дополнительному входу первого дешифратора и к входу элемен та задержки/ соединенного выходом с входом управления установкой кода реверсивного счетчика, установочные входы которого подключены к цифровым выходам блока памяти, а выход разрядов - к информационным входам п регистров, причем каждый i-ый tlsisn) регистр соединен управляющим входом с выходом i-ro элемента И, а выходами - с цифровыми входами i-ro цифроаналогового множительного блока, ан логовый вход которого является i-ым входом устройства, а выход через i-ый операционный усилитель соединен с i-ым выходом устройства 2. Недостатками известного устройств являются невысокая точность аппрокси мации функций с большими перепадами крутизны, обусловленная- равномерным расположением узлов интерполяции по оси аргумента t. I Цель изобретения - повышение точности работы устройства. Цель достигается тем, что вустройство для воспроизведения переменных во. времени коэффциентов, содержащее блок памяти, первый и второй счетчики, счетчик по модулю п, п эле ментов И, первый и второй дешифраторы, блок сравнения кодов, реверсивный счетчик, генератор импульсов, подключенный выходом к счетному вхо ду первого счетчика, соединенного выходом старшего разряда -со счетным входом счетчика по модулю п, подключенного выходами разрядов к входам первого дешифратора,- каждый из п вы ходов первого дешифратора подключен к первому входу соответствующего элемента И, соединенного вторым вхо дом с выходом блока сравнения кодов подключенного одной группой входов к выходам разрядов первого счетчика, а другой группой входов - к выходам разрядов второго счетчика, сое диненного счетным входом с входом старшего разряда счетчика по модулю п, п регистров, управляющий вход каждого из которых соединен с выходом соответствующего элемента И, п операционных усилителей, выходы которых являются выходами устройства, п цифро-аналоговых множительных блоков, цифровые входы которых соединены с выходами соответствующих регистров, выходы - с входами соот ветствующих операционных усилителей а аналоговые входы являются входами устройства, дополнительно введены элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, накапливаю щий сумматор, адресный счетчик, под ключенный разрядными выходами к адресным входам блока памяти, первая группа выходов которого подключена через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ к входам накапливающего сумматора, а вторая группа выходов - к входам установки кода реверсивного счетчика, выходы реверсивного счетчика через второй дешифратор подключены к счетному входу адресного счетчика и входу управления установкой кода реверсивного счетчика, выход генератора импульсов соединен со счетным входом реверсивного счетчика и входом накапливающего сумматора, знаковый выход блока памяти соединен с соответствующими входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и накапливающего сумматора, разрядные выходы накапливающего сумматора подключены к информационным входам каждого из п регистров. На фиг.. 1 приведена блок-схема устройства; на фиг. 2 - график, поясняющий принцип его работы. Устройство содержит генератор импульсов 1, первый и второй счетчики 2 и 3, счетчик по модулю п 4, блок сравнения кодов 5, первый дешифратор б, п элементов И 7) ,. . . , .7 , адресный счетчик 8, блок памяти 9, элемент ИСКЛЮЧАЮЩЕЕ ИЛИЮ, накапливающий сумматор 11, реверсивный счетчик 12, второй дешифратор 13,. п регистров 14,..., 14, п цифроаналоговых множительных блоков IS , .. ., Г5., п операционных усилителей 16 , .. . , 16,. Устройство работает следующим образом. Требуемые значения функции от времени f(t) (где ) реализуются в устройстве по методу кусочно-линейной атгороксимации с произвольным (оптимальным) для каждой функции расположением узлов интерполяции по оси аргумента t. При этом в блок памяти 9 заносят информацию в двоичном коде о значении и знаке элементарного приращения ординаты А у: и количестве таких приращений на определенном (например, втором) линейном участке (фиг.2) К- У i-Z. u.y-j-i Дискретность элементарного при- ращения Atj по оси аргумента t определяется разрядностью первого счетчика 2. Отсчет времени t в устройстве осуществляется вторым счетчиком 3, который совместно с включенными последовательно первйм счетчиком 2 и счетчиком по модулю п 4 пересчитывает прямоугольные импульсы с выхода генератора импульсов 1. В течение времени, соответствующего периоду переполнения счетчика по модулю п 4, когда состояние второго счетчика 3 остается неизменным. устройством осуществляется поочеред ная вре,менная развертка всех п аппроксимирующих функций, текущие зна чения ординат которых в конечном итоге формируются в накапливающем сумматоре 11. Состояние выходов счетчика по мо дулю п 4 определяет порядковый номе развертываемой функции, а состояние выходов первого счетчика 2 - порядк вый номер элементарного приращения ординаты развертываемой, функции ду Выходной код адресного счетчика 8 обеспечивает выбор из блока памяти 9 одновременно значения элемента ного приращения ординаты д у; и его знака. Этот двоичный код с первой группы выходов блока памяти 9 через элемент ИСКЛЮЧДЩЕЕ ИЛИ 10 подается в накапливающий сумматор 11. Двоичный код количества приращений на оп ределенном линейном участке К; снимается с второй группы выходов блока памяти 9 и подается на входы установки кода реверсивного счетчика 1 По мере поступления прямоугольных импульсов с выхода генератора импуль сов- 1 и накапливающем сумматоре 11 происходит непрерывное суммирование или вычитание значений элементарног приращения ординаты uyj . При этом обеспечивается получение заданной крутизны каждого участка аппроксимации развертываемой функции. Знак приращения учитывается путем подачи на элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 10 и В накапливающий сумматор 11 соответствующего сигнала со знакового выхода блока памяти 9, При этом одновременно происходит пересчет в реверсивном счетчике 12 количества таких приращений. Нулевое-, состояние реверсивного счетчика 12 дешифрирует ся дешифратором 13, который формирует импульс, поступающий на счетный вход адресного счетчика 8 и на вход управления установкой кода реверсивного счетчика 12. Процесс выборки из блока памяти 9 и пересчета для следующего линейного участка функции повторяется аналогично. р Сигналы с разрядных выходов первого счетчика 2, как это следует из логики работы устройства, выполняют роль временного аргумента каждого элементарного приращения ординаты ду- i-ой аппроксимирукяцей функции. .Следовательно, в моменты времени, когда состояние выходов этого счетчика совпадает с состоянием выходов счетчика 3 временного аргумента t, . в накапливакядем сумматоре 11 формиру ется текущее значение ординаты 1-ой аппроксимирующей функции. Совпадение кодов на выходах счетчиков 2 и 3 фик сируется блоком сравнения кодов 5, сигнал с выхода которого поступает на вторые входы элементов И 7( t t 7. Первый дешифратор 6 декодирует каждое i-ое состояние счетчика по модулю п 4 и, стррбируя i.-ый элемент И 7- , опрашивает состояние выхода блока сравнения кодов 5.Сигнал совпадения с блока сравнения кодов 5, пройдя через i-ый элемент 7 , поступает на управляющий вход i-ro регистра 14,- , подключенного информационными входами к разрядным выходам накапливающего сумматора 11. При этом в регистр 14,- записывается значение текущей ординаты Г-ой аппроксимирующей функции fj (t).no переполнению счетчика 2 счетчик по модулю п 4 переходит в (1+1)-е состояние, соответствующее развертке i+1 аппроксимирующей функции, и в момент времени, когда произойдет совпадение кодов на выходах счетчиков 2 и 3, аналогично в (1+1)-й регистр 14, записано значение f|Vi(t). . После переполнения счетчика помодулю п -4 второй счетчик (аргумента t) 3 переходит в следующее состояние и процесс, в результате которого будут сформированы значения всех п функций времени для нового значения аргумента, повторяется. Код текущего значения каждой 1-ой функции f;(t) поступает на цифровые входы i-ro цифро-аналогово- . го множительного блока 15. , на аналоговый вход которого поступает сигнал i-ой независимой переменной у. в аналоговой форме. В результате этого на выходе каждого i-го операционного усилителя 16, вход которого подключен к выходу -то цифро-аналогового множительного блока , а выход является i-ым выходом устррйства, будет получено произведение г, y,-.fi(t). . Таким образом, предложенное устрорство позволяет осуществлять одновременное воспроизведение нескольких переменHEdx во времени коэффициентов с произвольным расположением узлов интерполяции, что позволяет повысить точность по сравнению с прототипом и создает предпосылки для широкого использования таких устройств в составе гиб.ридных вычислительных систем и специализированных устройств автоматики. Формула изобретения Устройство для.воспроизведения переменных во времени коэффициентов, содержащее блок памяти, первый и второй счетчики, счетчик- по модулю п, п элементов И, первый и второй дешифраторы, блок сравнения кодов, реверсивный счетчик,. генератор импульсов, подключенный выходом к счетному входу первого счетчика, соединенного выходом старшего разряда со счетным входом счетчика по модулю п, подключенного выходами разрядов к входам первого дешифратора, каждый из п выходов первого дешифратора подключен к первому входу соответствующего эле мента И, соединенного вторым входом с выходом блока сравнения кодов, под ключенного одной группой входов к выходам разрядов первого счетчика, а другой группой входов - к выходам разрядов второго счетчика, соединенного счетным входом с выходом старшего разряда счетчика по модулю п, п регистров, управляюгоий вход каждого из которых соединен с выходом соответствующего элемента И, п операционных усилителей, выходы которых являются выходами устройства, п циф ро-аналоговых множительных блоков, цифровые входы которых соединены с выходами соответствующих регистров, выходы - с входами соответствующих операционных усилителей, а аналоговые входы являются входами устройст ва, отличающееся тем, что, с целью пойьвиения точности работы устройства, оно содержит эле мент ИСКЛЮЧАКЯЦЕЕ ИЛИ, Накапливающий сумматор, адресный счетчик, подклю- ненный разрядными выходами к адресным входам блока памяти, первая .группа выходов которого подключена через элемент ИСКЛЮЧАЮЩЕЕ ИЛИ к входам накапливающего сумматора, .а вторая группа выходов - к входам установки кода реверсивного счетчика, выходы реверсивного счетчика через второй дешифратор подключены к счетному входу адресного счётчика и входу управления установкой кода реверсивного счетчика, выход генератора импульсов соединен со счетным входом реверсивного счетчика и входом накапливающего сумматора, знаковый выход блока памяти соединен с соотверствующими входами элем нта ИСКЛЮЧАЮЩЕЕ ИЛИ и накапливающего сумматора, разрядные выходы накапливающего сумматора подключены к информационным входам каждого из п регистров. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 840957, кл. G Об G 7/26, 1979. 2.Авторское свидетельство СССР по заявке 2904437/18-24, кл. G 06 G 7/26, 1980 (прототип;.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1982 |

|

SU1040493A1 |

| Функциональный преобразователь | 1980 |

|

SU894748A1 |

| Устройство для воспроизведения переменных во времени коэффициентов | 1980 |

|

SU894737A1 |

| Вычислительное устройство | 1981 |

|

SU1001114A1 |

| Вичислительное устройство | 1979 |

|

SU783804A1 |

| Аппроксимирующий функциональный преобразователь | 1984 |

|

SU1205153A1 |

| Функциональный преобразователь | 1981 |

|

SU1018127A1 |

| Функциональный преобразователь | 1983 |

|

SU1115069A1 |

| Устройство для поворота вектора (его варианты) | 1982 |

|

SU1078431A1 |

| Цифро-аналоговый функциональный преобразователь | 1980 |

|

SU895973A1 |

Авторы

Даты

1983-03-15—Публикация

1981-07-20—Подача