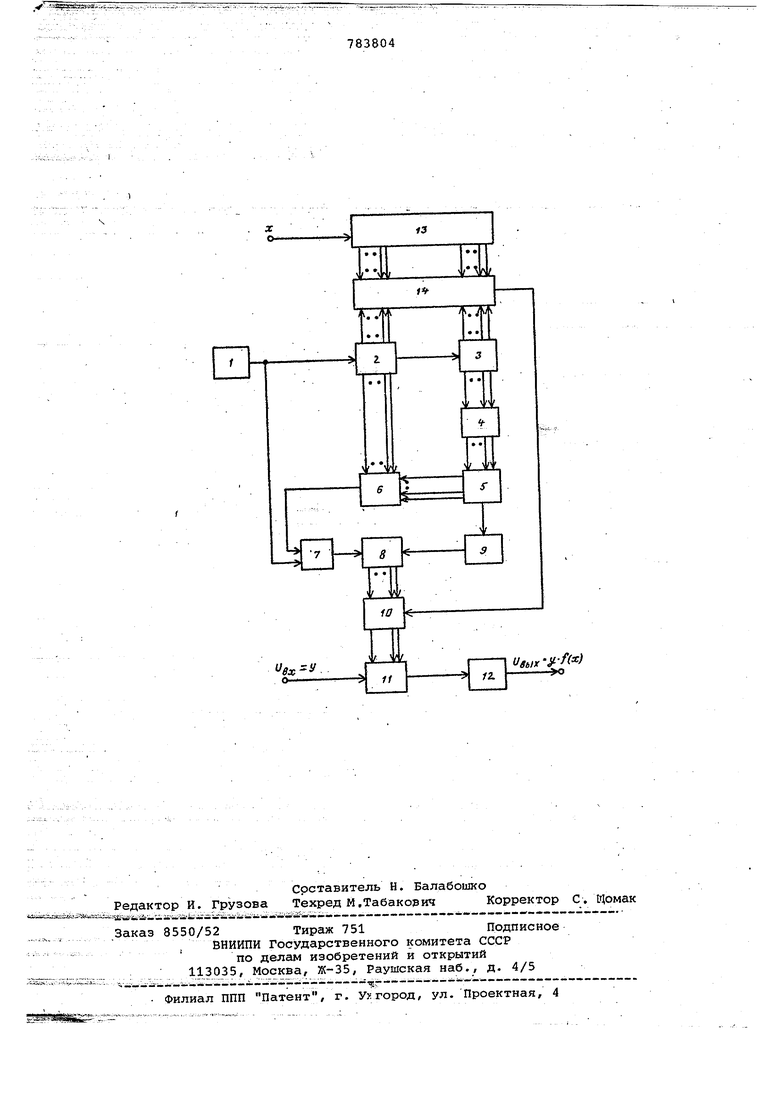

(54) ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО Изобретение относится к области автоматики и вычислительной техники и может быть использовано для реализации функциональных зависимостей вида 2 yf(x), где х, у, z - величины, представленные в аналоговой форме. Известно вычислительное устройство, содержащее шаговый искатель, сек ционный делитель напряжения, наборно поле для коммутации ламелей шагового искателя с отводами делителя напряже ния . Принцип работы указанного устройства заключается в кусочнопостоянной аппроксимации заданной функции времени и умножении ее на входной сигнал. К недостаткам устройства относятся низкая надежность, трудоемкий ручной ввод данных, .ограниченные функциональные возможности, так как аргументом может быть тсэлько время; t Наиболее близким техническим реше нием к изобретению является вычислительное устройство, содержащее набор ное поле, ключевые схемы,;умножающий цифроаналоговый преобразователь, рервесивный счетчик, сумматор, делитель частоты, блок дифференцирования и операционный усилитель, одни вхоцы ключевых схем соединены с выходами делителя частоты, другие входы ключевых схем - с соответствующими выходными шинами наборного поля, выходы ключевых схем через соединенные последовательно блок дифференцирования и сумматор подключены к реверсивному счетчику, выходы которого связаны со входами умножающего цифроаналогового преобразователя, подключенного выходом ко входу операционного усилителя Недостатками прототипа являются невысокое быстродействие к ограниченные функциональные возможности в связи с ручным вводом данных аппроксимируемой функции и использованием только одного вида аргумента - времени t . Цель изобретения - расширение функциональных возможностей устройства путем воспроизведения функций независимого аргумента и повышение быстродействия. Это достигается тем, что вычислительное устройство, содержащее операционный усилитель, выход которого является выходом устройства, цифроаналоговый блок умножения, аналоговый вход которого служит первым входом устройства, а выход подключен ко входу операционного усилителя, первый реверсивный счетчик, вход управления, реверсом которого подключен к выходу триггера знака, дополнительно содержит генератор прямо угольных импульсов, первый и второй счетчики, блок памяти, дешифратор, преобразователь код-частота, элемент . И, аналого-цифровой преббра:зоватёль , блок сравнения кодов и регистр..При этом выход генератора прямоугольных импульсов подключен к счетному входу первого счетчика и к первому входу элемента И, выход старшего разряда первого счетчика - к счетному входу второго счетчика. Разрядные выходы первого счетчика подсоединены к первым входам преобразовагеля код-часто та и к первым входам блока сравнения кодов, разрядные выходы второго счетчика - к первым входам блока сравнения кодов и черездешифратор к адрёс ЁаУ1 входам блока памяти, выходы которого подключены ко вторым входам преобразователя код-частота, подсоединенного выходом ко второму входу элемента И. Знаковый разряд блока памяти подключен ко входу триггера знака, разрядные выходы реверсивного счетчика подсоединены к соответствующим входам регистра, а счетный вход - к выходу элемента И. Цифровые входы цифроаналогового блока умноже ния соединены с выхбдами регистра, управляющий вход которого подключен к выходу блока сравнения кодов, вто рые входы блока сравнения кодов соединены с выходами аналого-цифрового преобразователя, вхОд которого явля ется вторым входом устройства. На чертеже приведена структурная схема вьичислительного устройства. Вычислительное устройство содерж генератор 1 прямоугольных импульсов первый счетчик 2, второй счетчик 3, дешифратор 4, блок 5 памяти, преобразователь б код-частота, элемент И 7, реверсивный счетчик 8, триггер 9 знака, регистр 10, цифроаналоговый блок 11 умножения, операционный уси литель 12, аналого-цифровой преобра зователь 13, блок 14 сравнения кодов Устройство работает следующим образом. Аргумент X воспроизводимой функции в аналоговой форме со второго входа устройства поступает.на вход аналого-цифрового преобразователя 13 с выхода которого в цифровой форме подается на вторые, входь блока 14 сравнения кодов. Прямоуго.льные импульсы с выхода генератора 1 пересчитываются последовательно включенными первым 2 и вторым 3 счетчиками Быстрый счетчик 2 участвует в кусочно-линейной аппроксимации Кс1ждого участка заданной функции, а медленный счетчик 3 служит для отыскания через дешифратор 4 в блоке 5 памяти значений приращений ординат узлов аппроксимации заданной функции. Сигналы с разрядных выходов счетчика 2 и счетчика 3 поступают на первые входы блока 14 сравнения кодов. При равенстве кодов на выходе аналого-цифрового преобразователя 13 и в счетчиках 2 и 3 на выходе блока 14 сравнения кодов формируется сигнал, поступающий на управляющий вход регистра 10 и разрешающий запись в него кода с выхода реверсивного счетчика 8. Преобразователь б код-частота, управляемый по первым входам разрядНЫЛ1И выходами первого счетчика 2, а по вторым - выходами блока 5 памяти, формирует на выходе сигнал разрешения счета, который поступает на вход элемента И 7 и разрешает прохонодение прямоугольных импульсов генератора 1 на вход реверсивного счетчика 8 в зависимости от приращения соседних ординат узлов аппроксимации заданной функции. Триггер 9 знака подключен к знаковому разряду блока 5 памяти и управляет реверсом реверсивного счетчика 8, разрядные выходы которого ; управляют ключами цифроаналогового блока 11 умножения через промех уточный регистр 10. Аналоговый вход блока 11 является первым входом устройства. Преобразователь б код-частота обеспечивает получение заданной крутизны каждого участка аппроксимирующей функции и работает в соответствии с логическим выражением ,-4)vv, - V V -Ф -Ф -ф п п п п-1 п-а %) где Ф - - код на разрядных выходах счетчика 2; v - v - код на разрядных выходах блока 5 памяти; и - выходной сигнал преобразователя б код-частота. Генератор 1 прямоугольных импульсов, первый 2 и второй 3 счетчики, дешифратор 4, блок 5 памяти, преобразователь б код-частота, элеМейт И 7, триггер 9 знака, первый реверсивный счетчик 8 осуществляют временную развертку кусочно-линейной аппроксимирующей функции. С помощью аналого-цифрового преобразователя 13, блока 14 сравнения кодов, регистра 10 проиЬходит фиксация моментов равенства ординат временной и заданной функций для текущего аргумента X. При этом код текущей ординаты функции f (х) , соответствующей напряжению входного аргумента х, поступает на цифровые входы цифроаналогового блока 11 умножения в моменты времени, когда равны код аргумента на выходе аналого-цифрового преобразователя и периодически изменяющий ся код времени на разрядных выходах счетчиков 2 и 3. В данные моменты времени ординаты временной функции и аппроксимирующей функции f(x) также равны. Таким образом, устройство выполняет операцию умножения входного сиг нала у на заданную функцию f(x). Преимуществом предложенного вычис лительного устройства в сравнении с прототипом является расширение его функциональных возможностей за счет воспроизведения функций произвольного аналогового аргумента х и возможности автоматизации ввода узлов ап-проксимации функции f(x) с помощью ЦВМ,что создает предпосылки для широкого использования таких устройств в составе гибридных вычислительных систем. Кроме того, использование в качестве блока 5 памяти постоянных и репрограммируемых постоянных запоминающих устройств позволяет автоматизировать настройку на воспроизведение заданной функции в процессе изготовления и эксплуатации устройства.. . Формула изобретения Вычислительное устройство, содержащее операционный усилитель, выход которого является выходом устройства цифроаналоговый блок умножения, аналоговый вход которого является первым входом устройства, а выход подключен ко входу операционного усилителя, реверсивный счетчик, вход уп равления реверсом которого подключен к выходу триггера знака, отлича ющееся уем, что, с целью расширения функциональных возможностей путем воспроизведения функций независимого аргументами повьидения быстродействия, оно содержит генератор прямоугольных импульсов, первый и второй счетчики, блок памяти, дешифратор, преобразователь код-частота, элемент И, аналого-цифровой преобразователь , блок сравнения кодов и регистр, выход генератора прямоуголь.ных импульсов подключен к счетному входу первого счетчика и к первому входу элемента И, выход старшего разряда первого счетчика подключен . к счетнсму входу второго счетчика, разрядные выходы первого счетчика подключены к первым входам преобразователя код-частота и к первым входс м блока сравнения кодов, разрядн1 1е выходы второго счетчика подключены к первым входам блока сравнения кодов и через дешифратор к адресным входам блока памяти, выходы которого подключены ко вторым входам преобразователя код-частота, подключенного выходом ко второму входу элемента И, знаковый разряд блока памяти подключен ко входу триггера знака, разрядные выходы реверсивного счетчика подключены к соответствующим входам регистра, а счетный вход - к выходу элемента И, цифровые входы цифроаналогового блока умножения соединены с выходами регистра, управляющий вход которого подключен к выходу блока сравнения кодов, вторые входы блока сравнения кодов соединены с выходами аналого-цифрового преобразователя, вход которого является вторым входом устройства. Источникиинформации, принятые во внимание при экспертизе 1.Коган Б. Я. Электронные моделирующие устройстваИ их применение для исследования систем автоматического регулирования. M.jr Физматгиз , 1963, с. 348-34-9, рис. 199, 200. 2.Авторское свидетельство СССР 434421, кл. G 06 G 7/26, 1974 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь | 1980 |

|

SU894748A1 |

| Вычислительное устройство | 1982 |

|

SU1040493A1 |

| Устройство для воспроизведения переменных во времени коэффициентов | 1981 |

|

SU1005087A1 |

| Устройство для воспроизведения переменных во времени коэффициентов | 1980 |

|

SU894737A1 |

| Вычислительное устройство | 1981 |

|

SU1001114A1 |

| Функциональный преобразователь | 1979 |

|

SU840956A1 |

| Функциональный преобразователь | 1977 |

|

SU744639A1 |

| Функциональный преобразователь | 1985 |

|

SU1249547A1 |

| Функциональный преобразователь | 1979 |

|

SU842852A1 |

| Функциональный преобразователь | 1981 |

|

SU1018127A1 |

Авторы

Даты

1980-11-30—Публикация

1979-01-04—Подача