(54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения | 1979 |

|

SU824185A1 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Устройство для сопряжения цифровых вычислительных машин с каналами связи | 1985 |

|

SU1287171A1 |

| Устройство для сопряжения электронной вычислительной машины с дискретными датчиками | 1981 |

|

SU987615A1 |

| Устройство для сопряжения электронной вычислительной машины с каналами связи | 1983 |

|

SU1117627A1 |

| Устройство для сопряжения электронной вычислительной машины с дискретными датчиками | 1982 |

|

SU1084774A1 |

| Устройство для регистрации режимов работы двигателя | 1983 |

|

SU1117670A1 |

| Устройство для ввода информации | 1990 |

|

SU1756877A1 |

| Устройство для обхода узлов сеточной модели | 1985 |

|

SU1322332A1 |

| Устройство для сопряжения | 1982 |

|

SU1112359A1 |

Изобретение относится к технике, решающей аадачн сопряжения датчиков дискретной информации с устройством обработки данных или с управляющей вычислительной машиной при подаче информации о возбужденных датчиках состояний объектов. Известно устройство для сопряжения, содержащее блок считывания, бло местного управления, блок ком1 тации блок предварительного накопления ин формации, блок формирования импульсов, вход которого соединен со входом устройства, а выход - с первым входом блока накопления, второй вхо которого соединён с первым выходом блока управления, входы которого соединены со вторыми входами устрой ва, а второй выход - с первым входо блома коммутации, первый вход котор го сЪединен с выходом блока накопле ния, а выход - с первым входом блок считывания, второй вход которого со динен с третьим выходом блока управ ления, а выходы являются выходами устройства 1. Недостаток известного устройства низкое быстродействие при вводе информации в управляющую вычислительную машину. Из известных устройств наиболее близким к предлагаемому по технической сущности является устройство для сопряжения, содержащее блок управления, регистр,- чблок сравнения, счетчик текущего состояния датчиков, элементы И, распределитель, блок вывода информации, счетчик адреса, дешифратор адреса, коммутатор, первые входы которого соединены со входами устройства, вторые входы - с выходами дешифратора адреса, входы которого соединены соответственно с первыми входа1ии элементов И и с выходами счетчика адресов, вход которого соединен с первым выходом блока управления, второй выход которого соединен с первым входом блока вывода, выход которого есть выход устройства, а второй вход соединен с выходом коммутатора и со входом распределителя импульсов, выходка которого соединены соответственно со вторыми вхрдами элементов И, и с первым входом счетчика текущих состояний, вторые входы которого соединены с выходами элементов И,а выходы - с первыми входами блока сравнения и регистра, второй вход которого соединен с третьим выходом блока управления, а выходы со вторыми входами блока сравнения, выход которого соединен со входом блока управления 2.

Недостаток .известного устройства низкая пропускная способность, что обусловлено тем, что при изменении

состояния хотя бы одного датчика передаются состояния всех датчиков.Это снижает быстродействие устройства и определяет наличие информационной избыточности при передаче.

Цель изобретения - увеличение пропускной способности устройства.

Указанная цель достигается тем, что в устройство, содержащее первый регистр, коммутатор, информационные входы которого соединены с соответст вующнми входами устройства, а адресные входы - с соответствующими выходами доиифратора адреса, схему сравнения и счетчик адреса, соединенный выходами с соответствующими входами дешифратора адреса, а входами - с певым выходом узла синхронизации,второй выход которого подключен к управляющему входу первого регистра, информационные выходы которого соединены с первой группой входов cxe№i сравне ния, введены второй регистр и два шифратора, причем вторая и третья группы входов схемы сравнения подключе.ны соответственчо к выходам дешифратора адреса и с выходом второго регист за, информационным входам первог регистра и первого шифратора, а группа выходов - ко входам второго шифратора и управляющим входам первого шифратора, выходы которых являются соответственно вторыми и первыми выходами устройства, информационные входы второго регистра соединены с соответствующими выходами коммутатора, а управляющий вход - со вторым выходом узла синхронизации.

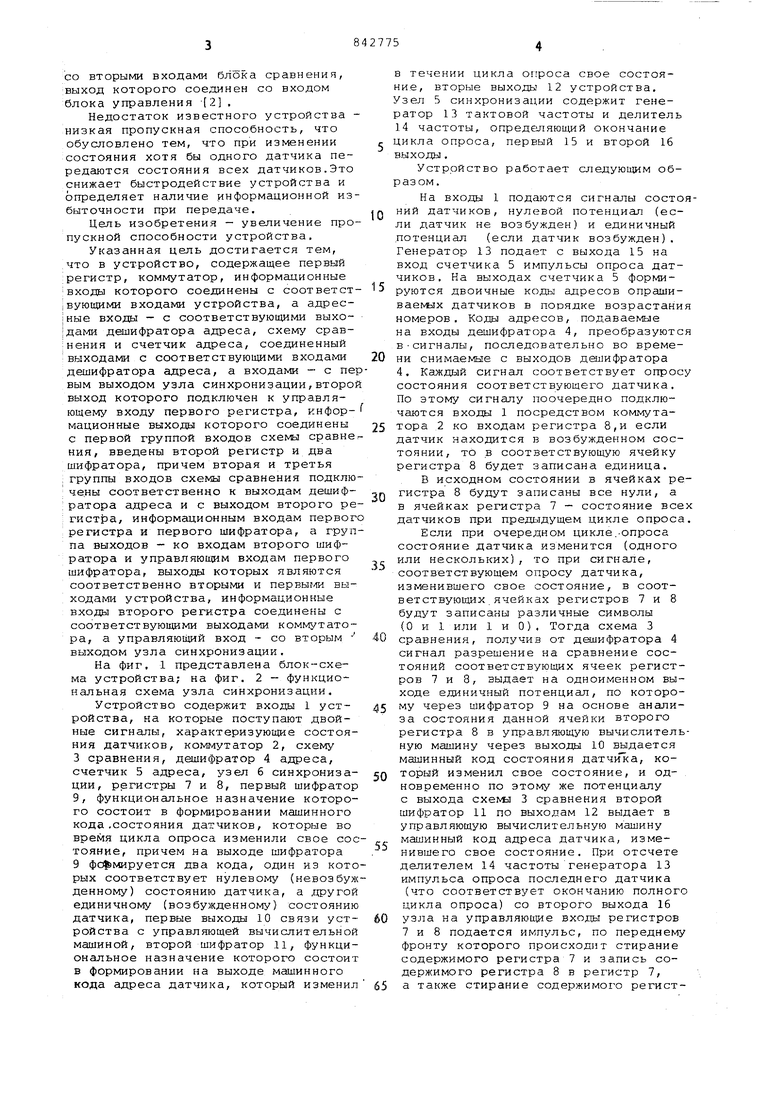

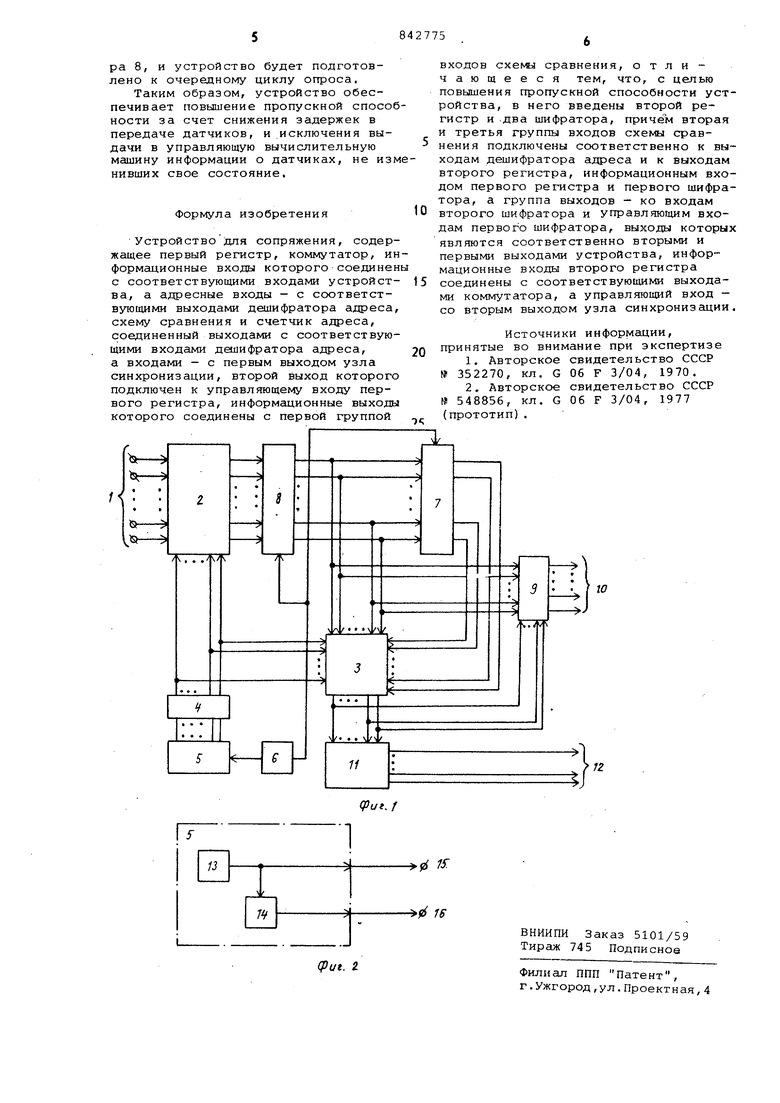

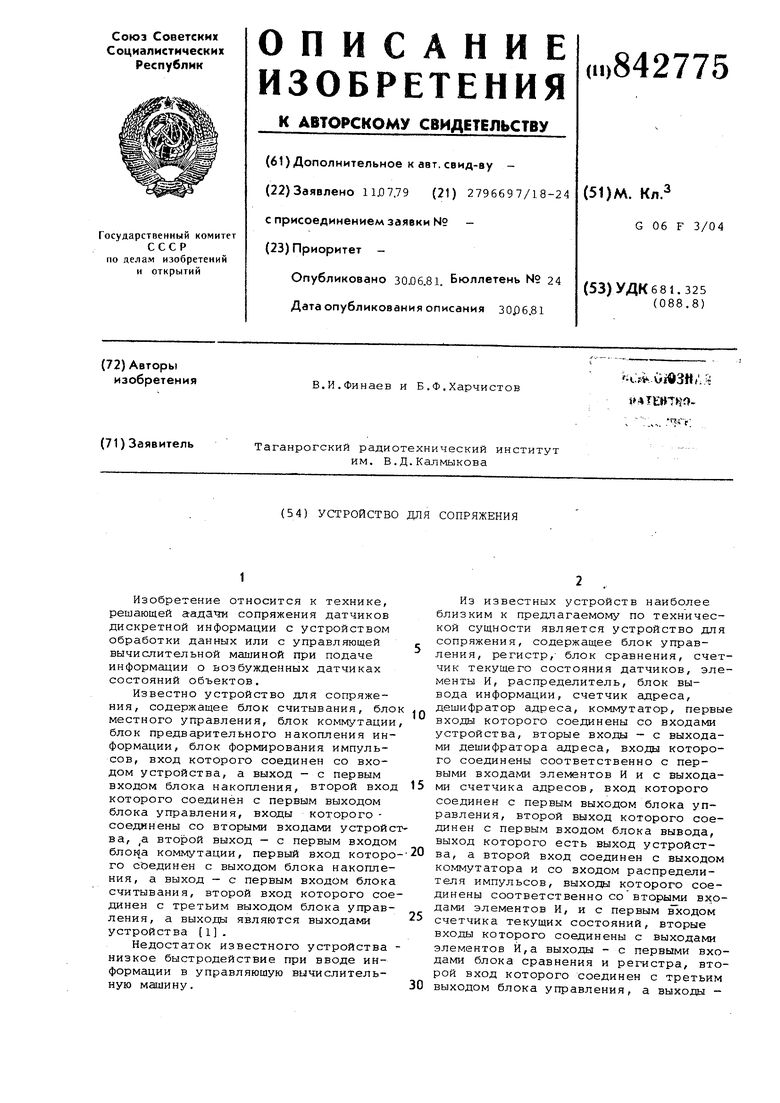

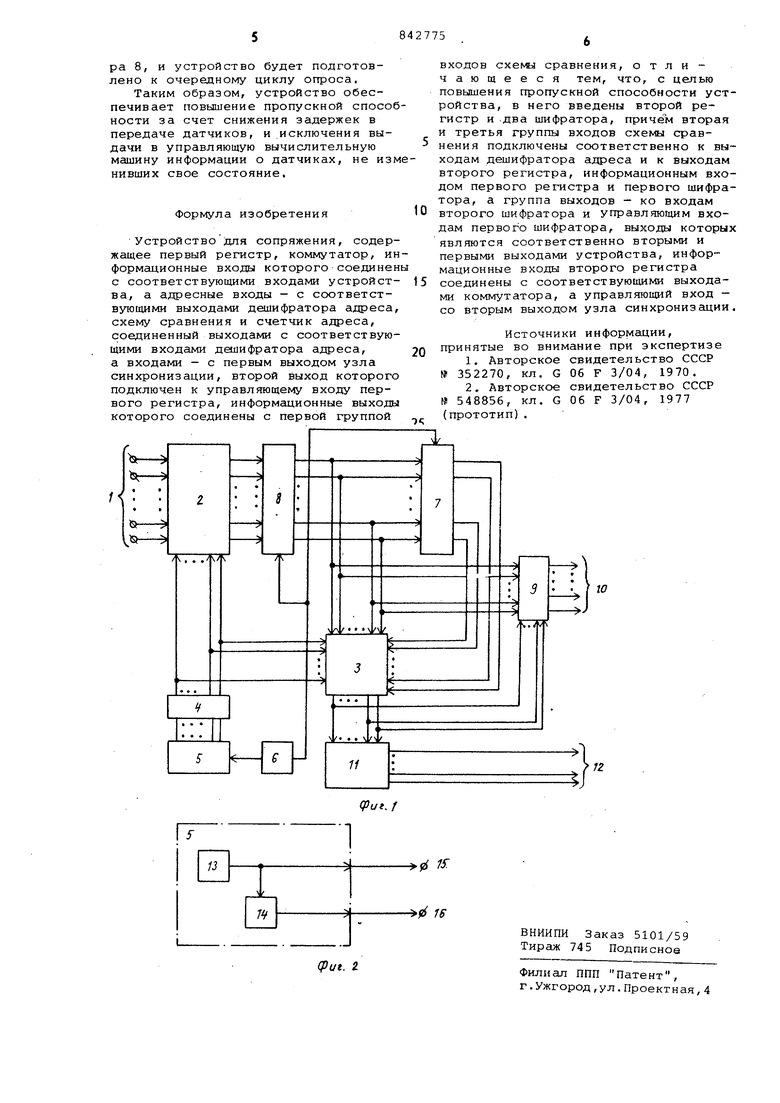

На фиг, 1 представлена блок-схема устройства; на фиг, 2 - функциональная схема узла синхронизации.

Устройство содержит входы 1 устройства, на которые поступают двойные сигналы, характеризующие состояния датчиков, коммутатор 2, схему 3 сравнения, дешифратор 4 адреса, счетчик 5 адреса, узел 6 синхронизации, регистры 7 и 8, первый шифратор 9/ функциональное назначение которого состоит в формировании машинного кода .состояния датчиков, которые во время цикла опроса изменили свое состояние, причем на выходе шифратора 9 формируется два кода, один из которых соответствует нулевому (невозбужденному) состоянию датчика, а другой единичному (возбужденному) состоянию датчика, первые выходы 10 связи устройства с управляющей вычислительной машиной, второй шифратор 11, функциональное назначение которого состоит в формировании на выходе машинного кода адреса датчика, который изменил

в течении цикла опроса свое состояние, вторые выходы 12 устройства. Узел 5 синхронизации содержит генератор 13 тактовой частоты и делитель 14 частоты, определяющий окончание цикла опроса, первый 15 и второй 16 выходы.

Устройство работает следующим образом.

На входы 1 подаются сигналы состоний датчиков, нулевой потенциал (если датчик не возбужден) и единичный .потенциал (если датчик возбужден). Генератор 13 подает с выхода 15 на вход счетчика 5 импульсы опроса датчиков. На выходах счетчика 5 формируются двоичные коды адресов опрашиваемых датчиков в порядке возрастани номеров. Коды адресов, .подаваемые на входы дешифратора 4, преобразуютс в-сигналы, последовательно во времени снимаемые с выходов дешифратора 4, Каждый сигнал соответствует опрос состояния соответствующего датчика. По этому сигналу поочередно йодключаются входы 1 посредством коммутатора 2 ко входам регистра 8,и если датчик находится в возбужденном состоянии, то в соответствующую ячейку регистра 8 будет записана единица,

В исходном состоянии в ячейках регистра 8 будут записаны все нули, а в ячейках регистра 7 - состояние все датчиков при предыдущем цикле опроса

Если при очередном цикле.-опроса состояние датчика изменится (одного или нескольких), то при сигнале, соответствующем опросу датчика, изменившего свое состояние/ в соответствующих ячейках регистров 7 и 8 будут записаны различные символы (О и 1 или 1 и 0). Тогда схема 3 сравнения, получив от дешифратора 4 сигнал разрешение на сравнение состояний соответствунзщих ячеек регистров 7 и 8, выдает на одноименном выходе единичный потенциал, по которому через шифратор 9 на основе анализа состояния данной ячейки второго регистра 8 в управляющую вычислительную машину через выходы 10 выдается машинный код состояния датчика, который изменил свое состояние, и одновременно по этому же потенциалу с выхода cxeNW 3 сравнения второй шифратор 11 по выходам 12 выдает в управляющую вычислительную машину машинный код адреса датчика, изменившего свое состояние. При отсчете делителем 14 частоты генератора 13 импульса опроса последнего датчика (что соответствует окончанию полного цикла опроса) со второго выхода 16 узла на управляющие входы регистров 7 и 8 подается импульс, по переднему фронту которого происходит стирание содержимого регистра 7 и запись содержимого регистра 8 в регистр 7, а также стирание содержимого регистpa 8, и устройство будет подготовлено к очередному циклу опроса.

Таким образом, устройство обеспечивает повышение пропускной способности за счет снижения задержек в передаче датчиков, и исключения выдачи в управляющую вычислительную машину информации о датчиках, не изменивших свое состояние.

Формула изобретения

Устройство для сопряжения, содержащее первый регистр, коммутатор, информационные входы которого соединены с соответствующими входами устройства, а адресные входы - с соответствующими выходами дешифратора адреса, схему сравнения и счетчик адреса, соединенный выходами с соответствующими входами дешифратора адреса, а входами - с первым выходом узла синхронизации, второй выход которого подключен к управляющему входу первого регистра, информационные выхода которого соединены с первой группой

входов схемы сравнения, отличающееся тем, что, с целью повышения пропускной способности устройства, в него -введены второй регистр и-два шифратора, причем вторая и третья группы входов схемы сравнения подключены соответственно к выходам дешифратора адреса и к выходам второго регистра, информационным входом первого регистра и первого ищфратора, а группа выходов - ко входам второго шифратора и управляющим входам первого шифратора, выходы которых являются соответственно вторыми и первыми выходами устройства, информационные входы второго регистра соединены с соответствующими выходами коммутатора, а управляющий вход - со вторым выходом узла синхронизации. /

Источники информации, принятые во внимание при экспертизе

1

Авторы

Даты

1981-06-30—Публикация

1979-07-11—Подача