Изобретение относится к вычислительной технике и передачи данных и может быть использовано в мультиплексорах и концентраторах передачи данных из каналов связи в ЭВМ при оп росе готовностей последовательно-параллельных преобразователей, а также датчиков дискретной информации автоматических систем зшравления. Известно устройство для сопряжения, содержащее коммутатор, блок памяти, первые входы которого соединены со счетчиком, блок элементов И, распределитель импульсов и блок срав нения, первый вход которого соединен с выходом блока памяти, вторые входы - с первыми входами распределителя импульсов, третий вход - с входом устройства и входом распределителя импульсов, выход - с первым входом блока элементов И, второй вход которого соединен с выходом коммутатора, третий вход - с первым входом распре делителя импульсов, выход - с вторьм входом блока памяти, третьи входы которого соединены с вторыми выходами распределителя импульсов, третий выход которого подключен к входу счетчика, выходы которого соединены с соответств тощими входами коммутато ра, четвертый вход блока памяти соединен с четвертью выходом распредели теля импульсов, .ij. Недостатками устройства являются большие аппаратурные затраты и низкое быстродействие, выражающееся в необходимости опроса каждого коммута ционного элемента несколько раз, пос ле чего блок сравнения вырабатьтает синхросигнал, поступающий на выход устройства. Кроме того сложен аппаратурный состав вследствие наличия двух запоминающих устройств. Наиболее близким по технической сущности к предлагаемому является ус ройство для сопряжения дискретных датчиков, содержащее коммутатор, информационные входы которого являются соответствующими входами устройства, а ajgpecHbie входы соединены с соответствующими выходами дещифратора адреса, входа которого подключены к соответствующим, выходам счетчика адреса и первым входам соответствующих элементов И группы, выходами соединенных с соответствующими входами счетчика текущего адреса. группа выходов которого подключена к группе входов регистра и первой группе входов схемы сравнения, вторая группа входов которой,соединена с группой выходов регистра, а выход с входом узла управления, подключенного соответственно первым и вторым выходами к входам счетчика адреса и регистра, памАть адресов и шифратор , причем группа входов памяти адресов подключена к выходам соответствующих элементов И группы, вход к третьему выходу узла управления, а выход - через шифратор к выходу устройства, выход коммутатора соединен с вторыми входами элементов И группы и вторым входам узла управления, группа входов которого подключена к вькодам.счетчика адреса. Узел управления содержит первый и второй дешифраторы, триггер, реверсивный счетчик, генератор, первый, второй, третий и четвертый элементы И, причем первьй вход реверсивного счетчика соединен с вторым входом узла, выходы через первый дешифратор соединены с единичным входом триггера, а второй вход реверсивного счетчика . соединен с третьим вькодом узла управления и с выходом первого элемента И, первый вход которого соединен с нулевым вБкодом триггера, а второй вход - с выходом генератора, первым входом второго элемента И и первым входом третьего элемента И и выходом второго дешифратора, входы которого являются группой входов узла, нулевой вход триггера соединен с первым входом узла и вторым входом четвертого элемента И, выход которого соединен с третьим входом реверсивного счетчика, единичный вход триггера соединён с вторым входом второго элемента И, выход которого является вторым выходом узла 2j. Недостатками известного устройства являются низкая достоверность передачи информации, так как жесткий цикл опрос датчиков - передача их состояния в ЭВМ обуславливает необходимость обязательной передачи в ЭВМ всего содержимого памяти после опроса последнего датчика и возможность потери информации, если ЭВМ занята обработкой другой информации, а также сложность устройства. Цель изобретения - повьпиение достоверности передачи информации.

Поставленная цель достигается тем что в устройство для сопряжения электронной вычислительной машины с каналами связи, содержащее генератор тактовых импульсов, коммутатор информации, группа информационных входов которого является группой информационных входов устройства, а группа адресных входов через дешифратор адреса подключ ена к группе выходов счет чика адресов и первым входам соответствующих элементов И первой группы, выходы которых соединены с информационным входом памяти адресов, элемент И, триггер, нулевым входом подкпюченньй к нулевому выходу распределителя, и схему сравнения, первый вход которой соединен с выходом счетчика числа записанных адресов, вторая группа элементов И, коммутатор адреса, элемент ИЛИ и счетчик числа считанных адресов, причем выход генератора тактовых импульсов соединен с тактовыми входа:ми счетчика адресов и распределителя, вход блокиров ки которого подключен к выходу триггера, управляющему входу коммутатора адреса и входу задания режима памяти адресов, группа вькодов которой является группой информационных выходов устройства, вход синхронизации памяти адресов соединен с выходом элемента ИЛИ, а адресный вход - с выходом коммутатора адреса, первый информа.циоиный вход которого соединен с выходом счетчика числа записанных адресов, а второй информационный вход с выходом счетчика числа считанных адресов и вторым информационным входом схемы сравнения,выход которой является выходом готовности устройстхва, первый, второй и третий выходы распределителя соединены соответственно с первым входом элемента ИЛИ, тактовым входом счетчика числа/ записан- ных адресов и первыми входами элементов И второй группы, первые входы которых подключены к группе выходов дешифратора адреса, а группа выходов является группой выходов сброса каналов устройства, вход блокировки счетчика адресов соединен с вторыми входами элементов И первой группы, единичным входом триггера и выходом элемента И, первый и второй входы которого соединены соответственно с выходом коммутатора информации и с входом режима работы устройства второй вход элемента ИЛИ и тактовый вход счетчика числа счйтанньк адресов соединены с входом синхронизации операции чтения устройства.

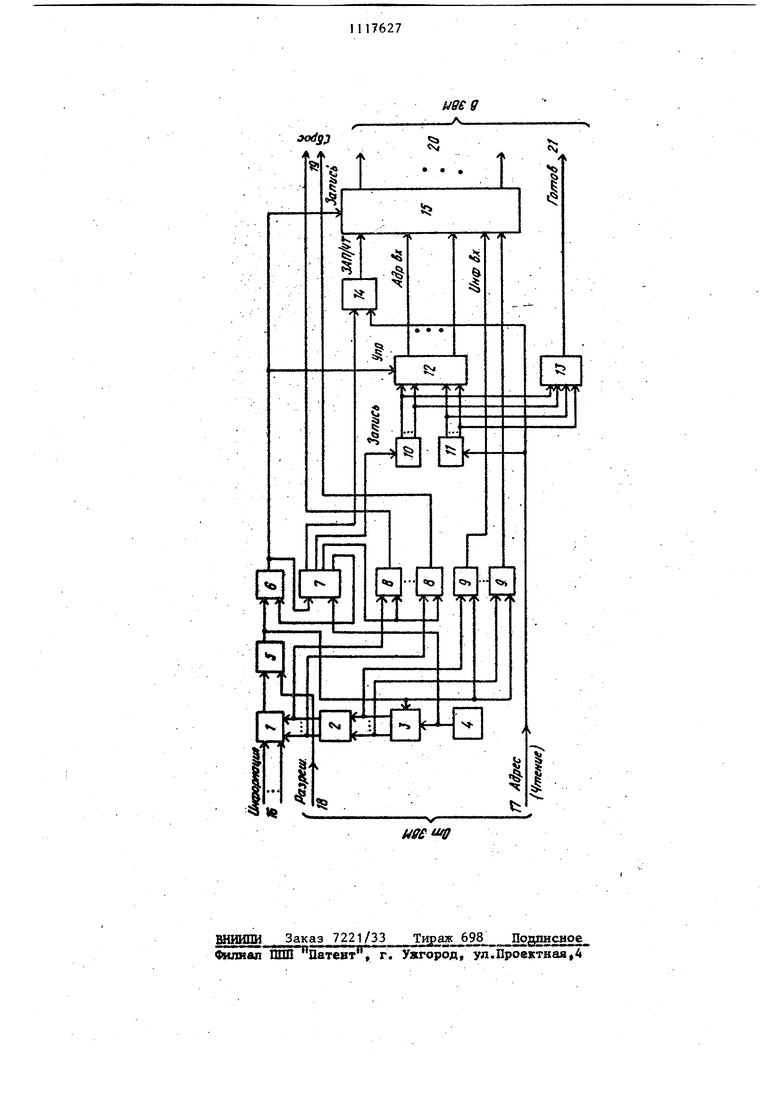

Йа чертеже представлена функцйо.нальная схема устройства.

Схема содержит коммутатор 1 информации, дешифратор 2 адреса, счетчик 3 адресов, генератор А тактовых импульсов, элемент И 5, триггер 6, распределитель 7, элементы И 8 и 9 второй и первой групп, счетчик 10 числа записанньк адресов, счетчик 1 числа считанных адресов, коммутатор 12 адреса схему 13 сравнения, элемент ИЛИ 14, память 15 адресов,группу 16 информационных входов устройства, вход 17 синхронизации чтения устройства, вход 18 режима устройства, группу 19 выходов сброса каналов устройства, группу 20 информационных выходов устройства и выход 21 готоЕЙ1ости устройства.

Устройство работает следующим образом.

После подачи питания ЭВМ вьщает команду, приводящую все периферийные устройства в исходное состояние. По .этой команде счетчики 10 и 11 сбрасывают в О, на шине 18 устанавливается сигнал логического О. Триггер 6 сбрасывается за счет сигнала .обратной связи установки распределителя 7 в импульсы с генератора 4 переключают счетчик 3, так как сигнал на его входе блокировки в состоянии О, и не сдвигают распределитель 7 из-за его блокировки сигналом с выхода триггера 6. Триггер 6 подготавливает коммутатор 12 к пропусканию сигналов, счетчика 11 и память 15 к операции Чтение. На выходе схемы 13 сравнения сигнал отсут ствует.

После подачи команды установки в исходное состояние ЭВМ устанавливает 1 на входе 18. При этом устройство приводится в рабочее состояние - режим ожидания внешней информации. При отсутствии информации состояние схемы не меняется, на выходе элемента И 5 сигнал отсутствует, импульсами генератора 4 через счетчик 3 и дешифратор 2 опрашивается коммутатор 1.

При появлении сигнала на какомлибо входе коммутатора 1 на выходе элемента И 5 появляется единичный сигнал, который останавливает счет11чик 3, перебрасывает триггер 6 и отбывает элементы И 9, через котефые код номера опрашиваемого канала подается на информационные входы памя ти 15. При этом триггер 6 переключает коммутатор 12 на пропускание сигналов со счетчика Ю, подготавлива-ёт память 15 к операции Запись и . разрешает прохождение тактовых импульсоб на распределитель 7, По сигнаду с первого выхода распределителя 7 через элементИЛИ 14 происходит за пись в память 15 номера опрашиваемого коммутатором 1 канала в ячейку с адресом 0...0. Сигнал с второго выхода распределителя 7 запЬсьтает в счетчик 10 число О... 01, подготавливая к записи ячейку с адресом 0...01 памяти 15. Сигнал с третьего выхода распределителя 7 сбрасывает в О опрашиваемый канал через один из открытых элементов И 8, а сигнал с нул вого выхода сбрасывает триггер 6 в первоначальное состояние, и приводит устройство в режим ожидания информации. Так как счетчик 10 установился в состояние 0...01, а счетчик 11 остался в состоянии 0...00, то на выходе схемы 13 сравнения будет состоя ние 1, которое инфop iиpyeт ЭВМ о наличии записанной информации. Если процессор ЭВМ занят отработкой более высокоприоритетной программы, а на входе коммутатора 1 имеется информа1Ц1Я. она аналогичным образом запи сываётся в ячейки памяти 15. При это 74 показания счетчика 10 все более отличаются от показаний-счетчика 11, т.е. счетчик 10 как бы убегает от счетчика 11. Логика считывания информации из памяти 15 адресов следующая. ЭВМ снимает разрешение с входа 18, при этом на выходе элемента И 5 всегда О независимо от наличия информации на входах коммутатора 1. Для исключения потери информации, если снятие сигнала на входе 18 происходит в момент вь(цачи распределителем 7 импульсов записи информации, ЭВМ делает задержку адреса устройства по входу 17 передним фронтом импульса, через элемент ЙПИ 14 читает ячейку памяти 15 с адресом 0...0, а задним фронтом записывает в счетчик 11 число 0...01, т.е. счеТчик 11 как бы догоняет счетчик 10, считывание информации происходит до получения состояния О на выходе схемы 13 сравнения или до обращения к процессору устройства с более высоким приоритетом, т.е. устройство не требует полного считывания памяти 15. После окончания считывания ЭВМ вое станавливает 1 на входе 18 и приводит устройство в режим записи информации. Таким образрм,,устройство более простыми средствами обеспечивает повышение достоверности пе1 едйчи информации счет исключения потерь информации.

иеешд

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения электронной вычислительной машины с каналами связи | 1989 |

|

SU1624465A1 |

| Устройство для управления многоканальной измерительной системой | 1983 |

|

SU1149255A1 |

| Устройство для вывода графической информации | 1987 |

|

SU1437908A1 |

| Устройство для формирования управляющей информации при обработке данных сейсмических колебаний | 1981 |

|

SU1000766A1 |

| Устройство для сопряжения электронной вычислительной машины с каналами связи | 1988 |

|

SU1513463A2 |

| Устройство для обработки сейсмической информации | 1984 |

|

SU1208561A1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1987 |

|

SU1439672A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для управления параллельным выполнением команд в электронной вычислительной машине | 1982 |

|

SU1078429A1 |

| Устройство для сопряжения дискретных датчиков с электронной вычислительной машиной | 1982 |

|

SU1024898A2 |

УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭЛЕКТРОННОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ, содержащее генератор тактовых импульсов, коммутатор информации, группа информационных входов которого является группой информационных входов устройства, а группа адресных входов через дешифратор адреса подключена к группе выходов счетчика адресов и первым входам соответствующих элемен- ов И первой группы, выходы которых соединены с информационным входом памяти адресов, элемент И, триггер, нулевым входом подключенный к нулевому выходу распределителя, исхему сравнения, первый вход которой соединен с выходом счетчика числа записанных адресов, отличающееся тем, что, с целью повышения достоверности передачи информации, в него введены вторая группа элементов И, коммутатор адреса, элемент ИЛИ и счетчик числа считанных адресов, причем выход генератора тактовых импульсов соединен с тактовыми входами счетчика адресов и распределителя, вход блокировки которого подключен к выходу триггера, ЗптравляЬщему входу коммутатора адреса и входу задания режима памяти адресов, группа выходов которой являет;ся группой информационных выходов устройства, вход синхронизации памяти адресов соединен с выходом элемента ИЛИ, а адресный вход - с выходом коммутатора адреса, первый информационный вход которого соединен с выходом счетчика числа записанных адресов, а второй информационный вход - с выходом счетчика числа считанных адресов и вторым информационным входом схемы сравнения, вькод которой является- выходом готовности устройства, первый, второй и третий выходы распределителя соединены соответственно с первым входом элемента ИЛИ, тактовым входом счетчика числа записанных адресов и первыми входами элементов И второй группы, первые входы которых подключены к группе выходов дешифра,тора адреса, а группа выходов является группой выходов сброса каналов устройства, вход блокировки счетчика ; адресов соединен с вторыми входами :зь д элементов И первой группы, единичным входом триггера и выходом элемента И, первый и второй входы которого соединены соответственно с выходом коммутатора информации и с входом режима работы устройства, второй вход элемента ИЛИ и так- товый вход счетчика числа считанных адресов соединены с входом синхрониза1Д1и операции чтения устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для ввода информации | 1979 |

|

SU847313A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для сопряжения | 1979 |

|

SU824185A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-10-07—Публикация

1983-07-01—Подача