чен ц входу второго счетчика и управляющему входу мультиплексора адреса буферной памяти, второй вход шифра,тора .формата слова подключен к выходу третьего триггера, счетный вход которого соединен с выходом шестого элемента И, выход первого триггера подключен к третьему входу шифратора формата слова, выход которого подключен к информационному входу буферной памяти, адресный вход которой подключен к выходу мультиплексора адреса буферной памяти, первым

информационным входом соединенного с входом шестого элеметта И и выхо дом второго счетчика, а вторым информационным входом - с вторым вы,ходом согласукнцего коля 1утатора, третий и четвертый выходы которого подключены соответственно к входу регистра и второму информационному входу мультиплексора ащреса памяти запрета анализа, первый и второй входы - к управляющему входу устройства и выходу буферной па, мяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1985 |

|

SU1278866A1 |

| Устройство для ввода информации | 1982 |

|

SU1089566A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Устройство для сопряжения процессора с памятью | 1986 |

|

SU1363229A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство для управления сверхоперативной буферной памятью мультипроцессорной ЭВМ | 1981 |

|

SU980097A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Устройство для сопряжения ЭВМ с каналами связи | 1987 |

|

SU1411762A1 |

| Устройство для подключения устройств ввода-вывода к многосегментной магистрали | 1987 |

|

SU1564638A2 |

Изобретение относится к вычислительной технике и может быть использовано в автоматизированных системах управления для сброса информации от двухпозиционных датчиков.

Известно устройство для сбора информации от дискретных датчиков, содержащее устройства сравнения для аждого датчика, устройства запоминания кодов датчиков , устройство запоминания изменения состояния датчиков, устройство записи изменившейся информгщии, предназначенное для записи нового кода в регистр числа, устройство для формирования адреса датчика, изменившего свое состояние, регистр адреса и устройство для формирования сигналов разрешения передачи информации ij ,

Недостаток, этого устройства большие аппаратные затраты,вызванные наличием индивидуальных для кгикдого датчика устройств сравнения и устройств запоминания кодов датчиков.

Наиболее близким к предлагаемому по сущности технического раиения является устройство для сопряжения электронной вычислительной машины с дискретными датчика1 и, содержащее коммутатор, счетчик, , схему сравнения, первый и второй триггеры, узел синхронизации, узел согласования с электронной вычислительной машиной (ЭВМ), причем информационные входы коммутатора являются соответствуюйщми входами устройства, а адресный вход соединен с выходом счетчика, подключенного входом к первому выходу узла синхронлзации, второй выход которого соединен с синхронизирующим входом памяти, подключенной выходом к первому входу схемы сравнения , и узел согласования с электронной вычислительной машиной, выходы которого являются выходами устройства,- первый и второй выходы nepвого триггера подключены соответственно к вцходу коммутатора и третьему выходу узла синхронизации, а выход - к информационному входу памяти и второму входу cxevsa срав{1ения, выходом соединенной с первым входом второго триггера, второй вход которого подключен к второму выходу узла синхронизации, а выход и третий вход - соответственно к информационному входу и управляющему выходу .узла согласования с ЭВМ, адресный вход которого соединен с выходсм счетчика и адресным входом памяти, вход пуска узла синхронизации соединен с выходом второго триггера, а вход тактов является тактовым входом устройства 2 .

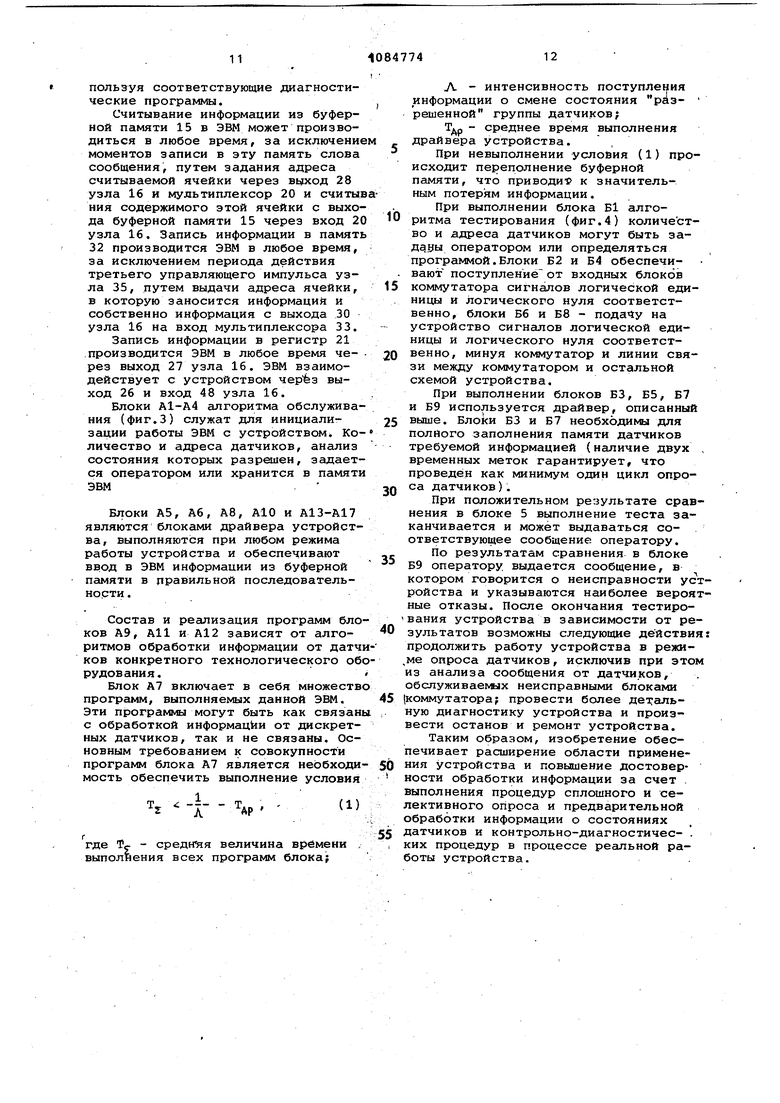

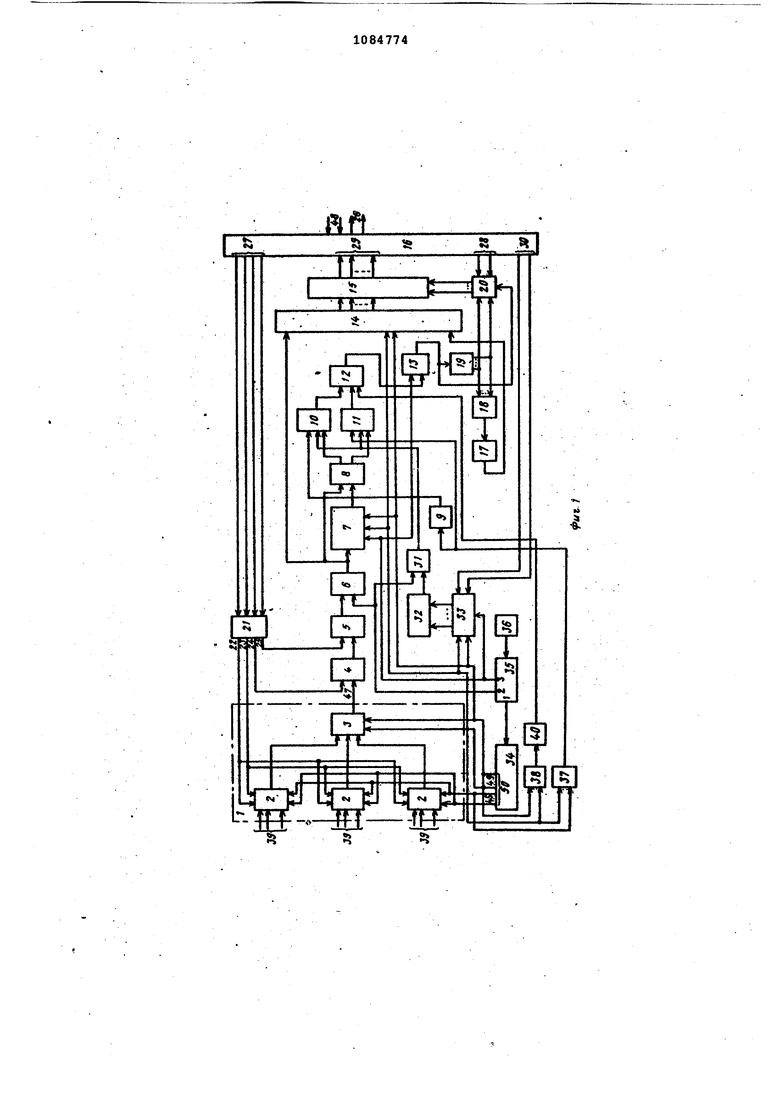

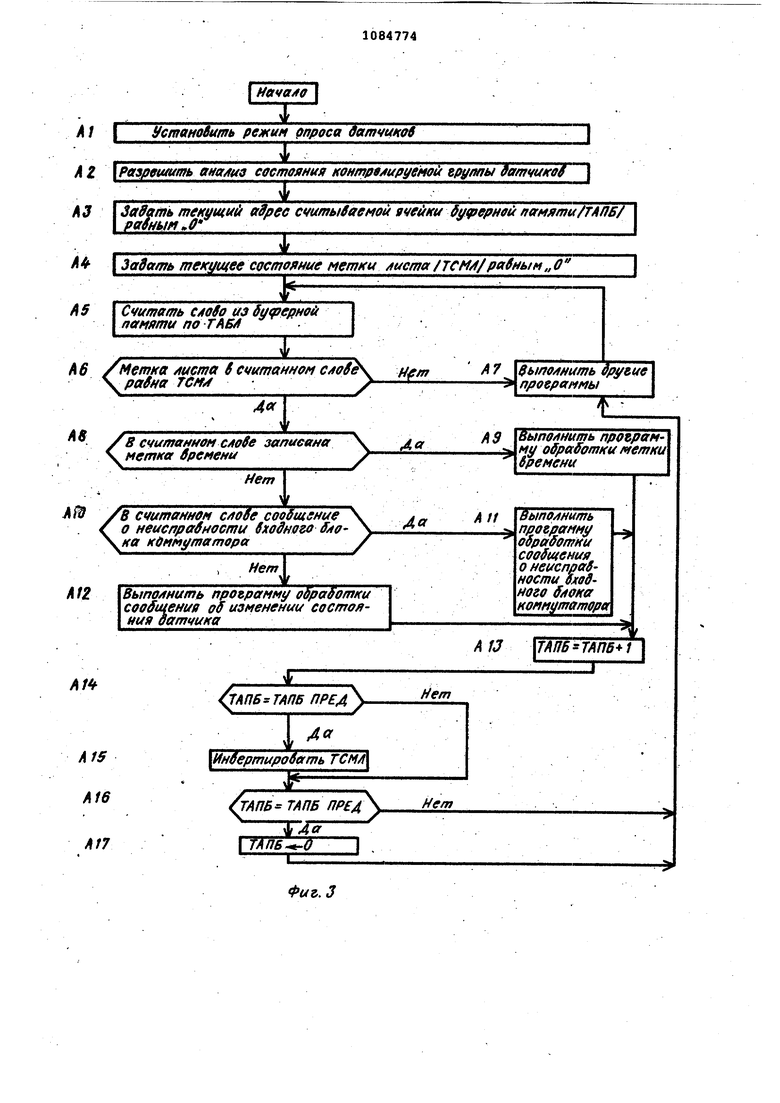

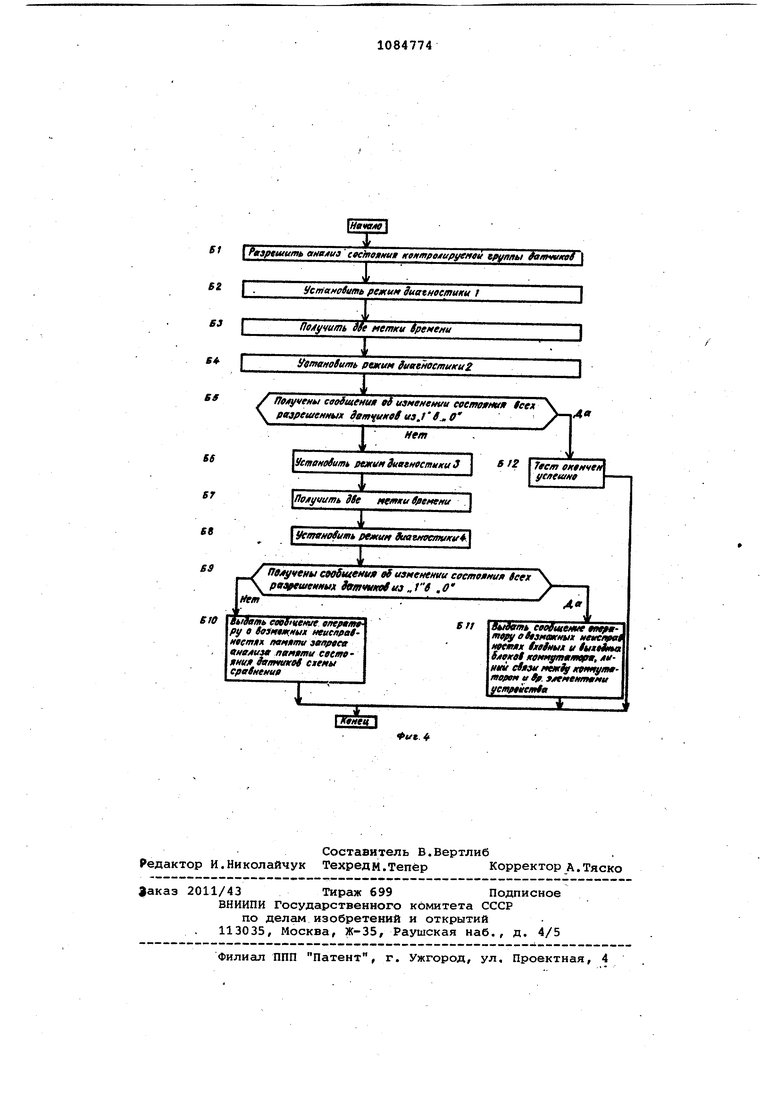

Недостатком известного устройства является низкая достоверность обработки информации из-за возможности потери информации от ряда датчиков, обусловленной тем, что сканирование датчиков приостанавливается . на время обработки запроса прерывания в ЭВМ, генерирующегося при каждом несравнении состояния датчика в соседних циклах. Такой режим работы создает болыиие трудности при использовании устройства при кратковременных срабатываниях дискретных датчиков. Кроме того, ограничена область применения этого устройства, что обусловлено Невозможностью использования устройства в системах, обслуживающих большое количество групп датчиков удаленн1ах от ЭВМ, и имеется большое число кратковременно срабатывающих датчиков в каждой группе. В таких условиях известное устройство допускает потери информации о состоянии датчиков, так как сканирование датчикрв приоСтанав ливается на время обработки запроса прерывания в ЭВМ, генерирующегося при каждом несравнении состояния датчика в соседних циклах. устройстве .отсутствует возможность искл1очения из анализа в цикле сканирован состояния отдельных групп датчиков, отключенных, что повышает вероятность потери информации за счет увеличения цикла сканирования и обработки избыточной информации. Кроме того, в известном устройст ве отсутствует возможность проведения контроля и диагностики оборудов ния без отключения его от системы, что снижает достоверность информаци о срстоян ии контролируемых датчиков. Целью изобретения является повышение достоверности работы устройст .Поставленная цель достигается тем, что в устройство, содержащее два триггера, коммутатор, информаци ные группы входов которого являются соответствующими информационными группами входов устройства, а управ ляющий вход соединен с адресным входом памяти состояния датчиков и выходом первого счетчика, подключенного входом к первому выходу узла синхронизации, вход и второй выход которого соединены соответственно с генератором тактовых импульсов и синхронизирующим входом памяти состо яния датчиков, подключенной выходом к первому входу схемы сравнения, а информационным входом - к выходу пер вого триггера и второму входу схемы сравнения, согласующий коммутатор, первый выход которого является выходом устройства, первый вход первого триггера подключен к третьему выходу узла синхронизации, введены шесть элементов И, три элемента ИЛИ, два элемента НЕ, третий триггер, регистр второй счетчик, шифратор формата слова, память запрета анализа, буферная память, мультиплексор адреса памяти запрета анализа и мультиплексор адреса буферной памяти, причем выход коммутатора подключен к первом входу первого элемента ИЛИ, выход которого подключен к первому входу первого элемента И, выход которого подключен к второму входу первого триггера, пергвый и второй контрольны входы коммутатора подключены соответ ственно к первому и второму разрядным выходам регистра, третий и четвертый разрядные выходы которого под ключены соответственно к вторым входам первых элементов И, второй выход узла синхронизации пЪдключен к управляющему входу мультиплексора адреса памяти запрета анализа и первому входу второго элемента И, третий выход узла синхронизации подключен к первому входу второго триггера, выход которого подключен к пер вым входам третьего и четвертого элементов И, а второй вход - через память запрета анализа к выходу мультиплексора адреса памяти запрета анализа, первый - третий входы второго элемента ИЛИ подключены соответственно к выходам четвертого и третьего элементов И и через первый элемент НЕ . к выходу третьего элемента ИЛИ, вход которого.подключен к выходу первого счетчика, входу пятого элемента И, первому информационному входу мультиплексора адреса памяти запрета анализа и первому входу шифратора формата слова, выход пятого элемента И соединен с вторым входом третьего элемента И и через второй элемент НЕ с вторым входом четвертого элемента И, третьи входы третьего и четвертого элементов И соединены соответственно с первым и вторым выходами схемы сравнения, первый выход второго элемента ИЛИ подключен к второму входу второго элемента И, выход которого подключен к входу второго счетчика и управляющему входу мультиплексора адреса буФеонпй памяти, второй вход шифратора формата слова подключен к выходу третьего триггера счетный вход которого соединен с выходом шестого элемента И, выход первого триггера подключен к третьему входу шифратора формата слова, выход которого подключен к информационному входу буферной памяти, адресный вход которой подключен к выходу мультиплексора адреса буферной памяти, первым информационным входом соединенного с входом шестого элемента И и выходом второго счетчика, а вторым информационным входом - с вторым выходом согласующего коммутатора,третий и четвертый выходы которого подключены соответственно к входу регистра и второму информационному входу мультиплексора адреса памяти запрета анализа, первый и второй входы -. соответственно к управляквдему входу устройства и выходу буферной памяти. На фиг. 1 представлена блок - схема устройства; на фиг. 2 - функциональная схема второго блока коммутатора на фиг. 3 и 4 - блок-схемы алгоритма обслуживания и алгоритма тестирования устройства. , Устройство содержит коммутатор 1, включающий в себя-входные блоки 2. и выходной блок 3, первый элемент ИЛИ 4, первый элемент И 5, первый триггер б, память 7 состояния датчиков, схему 8 сравнения, второй элемент НЕ 9, четвертый 10 и третий 11 элементы -И, второй элемент ИЛИ 12, второй элемент И 13, шифратор 14, буферную память 15, согласующий коммутатор 16, третий триггер 17, шестой элемент И 18, второй счетчик 19, мультиплексор 20 буферной памяти 15, регистр 21, первый четвертый разрядные выходы 22-25 регистра, первый третий выходы 26-28 согласующего ко .мутатора 16, второй вход 29 и четве тый рыход 30 согласующего комму.та тора 16 с ЭВМ, второй триггер 31, |память 32 запрета анализа, мульти плексор 33 памяти 32 запрета анализа, первый счетчик 34, узел 35 синх ронизации, генератор 36 тактовых им пульсов, пятый элемент И 37, третий элемент ИЛИ 38, входы 39 информацио ных групп входов коммутатора 1 и пе вый элемент НЕ 40. Входные блоки 2 коммутатора 1 со держат (фиг.2) элемент ИЛИ 41, эле менты И 42 и 43, триггер 44, шины 45 старших разрядов адресного входа и мультиплексор 46, выход 47. На фиг.1 показаны также шины 48 первого входа устройства и шины 49 младших разрядов выхода 50 счетчика 34. Коммутатор 1 конструктивно представляет собой совокупность разнесенных между собой входных блоков 2 и выходного блока 3. Последний пред ставляет собой муд ьтиплексор, обеспечивающий передачу уровня сигнала с выходов входных блоков 2 на выход 47.. Память 7 состояния датчиков.и па память 32 запрета анализа - статические- запоминающие устройства емкостью п 1 бит, причем nji N, где N - количество обслуживаемых датчиков. Буферная память 15 - статическое запоминающее устройство емкостью m , где m - количество I-разрядных ячеек памяти, и выбирается в зависимости от быстродействия ЭВМ и интенсивности входного потока сигналов. Минимальная разрядность ячеек памяти t определяется необходимой .разрядностью слова сообщения: (1 бит метка листа + 1 бит - состояние дат чика + С1о82КД бит - адрес датчика) где N - количество обслуживаемых датчиков; х1 - целая часть х+1. Шифратор 14 формирует в соответствующем формате слово сообщения дл 3airiucH в 1-разрядную ячейку буферной памяти 15. I Согласующий коммутатор 16 обеспечивает электрическое согласование сигналов, поступающих из устройства в ЭВМ и наоборот, а также коммутацию сигналов, поступающих на первый вход согласующего коммутатора, на один из вторых - четвертых выходов. Устройство предназначено для работы в системах с объектами контрол сложной структуры (порядка 10 000 датчиков). Датчики формируют нестационарный поток данных с минимальным временем присутствия сигналов на датчиках 20-30 мс. Такой поток информации характерен, например, для датчиков контроля состояния технологического оборудования городских телефонных станци (ГТС). Здесь на фоне небольшой интенсивности потока данных от датчиков технологического оборудования ГТС наблкдаются всплески информационного потока в часы наибольшей нагрузки. Устройство позволяет располагать входные блоки 2 коммутатора 1 в ,непосредственной близости к контро|лируемому объекту. Это обеспечивает существенное сокращение длины соединительных линий для подключения двоичных датчиков к устройству .Связь между KONa iyTaTopOM 1 и остальными блоками устройства организуется магистралью с количеством соединительных линий п, определяемым из выражения , ,, где N - количество контролируемых двоичных датчиков. Устройство взаимодействует с ЭВМ в асинхронном режиме. Это достигается применением буферной памяти 15, которая обеспечивает сглаживание информационного потока. Такой режим работы устройства позволяет уменьшить потери информации, обусловленные нестационарностью входного информационного потока, и рационально использовать вь числительные ресурсы ЭВМ, появляется возможность предварительной обработки информации. Объем буферной памяти 15 определяется по условиям усредненной интенсивности входного потока информации, а также вычислительной мощности ЭВМ. Период цикла сканирования датчиков определяется :минимальным временем присутствия сигнала на датчике контролируемого оборудования. Время изменения состояния любого датчика из контролируемой совокупноети фиксируется с помощью временных меток, расставляемых устройством с точностью до периода цикла сканирования. В устройство заложена возможность исключения из анализа по командам ЭВМ информсщии от определенных датчиков. Такой режим работы может возникать по условиям функционирования устройства либо при исключении из анализа информации от отключенных и неисправных датчиков или блоков 2 коммутатора 1. В таблицеприведены четыре режима проверки устройства, могут включаться периодически по командам ЭВМ. Проверка л Вывод логической единицы со всех ний связи входных блоков 2 между вход коммутатора 1 ными блока ми 2 и выходным бло Вывод логического ком 3, лин нуля со всех входных блоков 2 связи межд выходом 47 коммутатора 1 коммутатор 1 и входом элемента ИЛИ 4. Ввод логической Проверка пр единицы в память вильности з 7 состояния писи в памя датчиков 7 состояния датчиков Ввод логического Проверка пр нуля в память 7 вильности з состояния дат- писи нулей в память 7 состояния датчиков Включение четвертого диагностического режима вслед за третьим (и наоборот) позволяет полностью проверить памйть 7 состояния датчиков, так как в этом случае должны сформироваться сообщения об изменении всех ячеек памяти 7, т.е. имити руется изменение за один цикл опроса состояния всех датчиков. Возможна проверка по отдельным выбранным областям-памяти 7, используя запрещение анализа состояния остальных областей, что может оказаться необходимым при небольшом объеме буферной памяти 15. В устройстве буферная память 15 заполняется последовательно, ячейка за ячейкой, причем после заполнения последней ячейки запись производится в первую и т.д. Таким образом, память заполняется циклически. Для того, чтобы отличить два соседних цикла, введена метка лист, предста ляющая собой определенный бит в ело ве сообщения, формируемом шифратором 14. Значение метки сохраняется постоянным для всех слов, записываем|лх в течение одного цикла запол нения буферной памяти 15 и меняется лишь при окончании цикла, т.е. при записи в последнюю ячейку. Считывание информации в ЭВМ и запись со стороны устройства в буферную память 15 происходит асинхронно, метка листа дает возможность ЭВМ отличать вновь поступившие сообщения от записанных в предыдущем цикле. ЭВМ последовательно считывает содержимое буферной памяти 15, проверяет принадлежность считанного слова текущему циклу заполнения буферной памяти 15. Устройство при асинхронном режиме считывания информации из буферной памяти 15 в ЭВМ сохраняет временную последовательность поступления сигналов от датчиков с помощью меток времени, записываемых в буферную память 15 в начале каждого цикла сканирования, т.е. при появлении на выходе первого счетчика 34 кода, содержащего все нули. При этом датчик сигнала не подключается к входу с соответствующим адресом. Устройство работает следующим образом. Режим работы устройства устанав:ливается ЭВМ путем записиуправляющего слова в регистр 21 через выход 27 согласующего коммутатора. I - Режим опроса датчиков - основной режим работы устройства, при котором на выходах 23 и 25 регистра 21 активный уровень, а на выходах 22 и 24 - пассивный. На узел 35 поступают тактовые импульсы от генератора 36, причем по каждому тактовому импульсу формируются последовательно три управляющих сигнала. По первому импульсу, поступающему на счетчик 34 и увеличивающему его содержимое на единицу, происходит опрос входов коммутатора 1, т,е, опрос одного из входов 39 по шинам 45 старших разрядов счетчика 34 и выходов одного из блоков 2 по шинам 49 младших разрядов счетчика 34. Результат опроса поступает на выход 47 выходного блока 3. По коду счетчика 34, соответствующему адресу заданной группы входов 39 на выходе памяти 7, устанавливается сигнал состояния выбранного датчика, записанного в предыдущем цикле опроса, а на выходе памяти 32 устанавливается сигнал соответствующий значению, записанному в эту память ЭВМ через выход 30 узла 16 и мультиплексор 33. По второму сигналу узла 35 (третий выход) производится запись уровня входного сигнала опрошенного датчика в триггер 6, после чего в схеме 8 сравнения происходит сравнение уровня этого, сигнала с его уровнем в предыдущем цикле опроса. По второму управлянхцему сигналу производится также запись сигнала с- выхода памяти 32 в триггер 31, сигнал с выхода которого разрешает или запрещает прохождение сигналов с выхода схемы 8 сравнения через элементы И и 11 и элемент ИЛИ 12 на вход элемента И 13. По третьему управляющему сигналу узла 35 (второй выход) прои:5водится запись в память 7 состояния триггера 6 , а также разрешается во время действия этого сигнала запись инфор мации в память 32.с выхода 30 через мультиплексор 33. Если на выходе эл мента ИЛИ 12 присутствует активный уровень сигнала, то по третьему управляющему сигналу узла 35 элемент И 13 вырабатывает импульс, поступаю щий на шифратор 14, счетчик 19 и мультиплексор 20, При этом шифратор 14 формирует слово сообщения, содержащее код датчика (код на выход |Счетчика 34)., текущее состояние (состояние триггера 6) и метку листа (состояние триггера 17), а мультиплексор 20 записывает сформиро ванное шифратором слово в- буферную память 15 по адресу, соответствунлцему коду счетчика 19. Во время записи слова в буферную память 15 мультиплексор 20 запрещает прохождение адресной информации с выхода 28 для чтения информации ЭВМ. При появлении на выходе счетчика 19 кода, содержащего все единицы (конец листа) на выходе элемента И 18 образуется импульс, поступающий на счетный вход триггера 17 и переводящий его в противоположное состояние. Шифратор 14 в этом случае и далее до следующего переключения триггера 17 формирует слово, содержащее новую метку листа При появлении на выходе 50 счетчика 34 кода, содержащего все нули, на выходе элемента ИЛИ 38 появляется сигнал пассивного уровня, который инвертируется элементом НЕ 40 и поступает на вход элемента ИЛИ 12 и на входе элемента И 13 устанавливается активный уровень. При поступлении третьего управляющего импульса от уз ла 35 в буферную память 15 записывается слово сообщения, аналогично тому, как это происходит при несравнении состояния датчика. Отличается слово кодом датчика (все нули.), что является отличительной чертой метки времени. При появлении на шинах 45 старших разрядов счетчика 34 кода, содержащего все единицы, на выходе эле мента И 43 каждого входного блока 2 (фиг.2) появляется сигнал, поступающий на счетный вход триггера 44 и опрокидывающий его в противоположное состояние. Одновременно на выходе элемента И 37 появляется сигнал, открывающий элемент И 11 и запирающий через элемент НЕ 9 элемент И 10, При этом на другой вход элемента И 11 подается сигнал с второго выхода cxeVw 8 сравнения, Если этот сигнал активный, что происходит в том случае,когда состояние триггера 44 в предыдущем и текущем циклах сканирования совпадает и анализ данного сигнала не запрещен сигналом с выхода памяти 32 и сигнсшом на вцходетриггера 31, то по третьему упр авляющему импульсу узла Э5 происходит запись диагностического сообщения о неисправности в проверяемом входном блоке 2 в буферную память 15. Режим диагностики 1, Этот режим устанавливается при занесении ЭВМ в регистр 21 кода, при котором на выходах регистра устанавливаются . следующие уровни: на выходах 22, 23 и 25 - активный, на выходе 24 - пассивный. При этом впамять 7 заносятся единицы, так как на входах элементов ИЛИ 41 входных блоков 2 (фиг,2) постоянно присутствует активный .уровень с выхода 22 регистра 2 что имитирует единичное состояние всех входов мульт иплексоров 46, Режим диагностики 2,. Этот режим устанавливается при занесении ЭВМ в регистр 21 кода, при котором на выходах 24 и 23 регистра 21 - пассивный уровень, на выходе 25 - активный, состояние выхода 22 безразлично. При этом в память 7 заносятся нули, так как пассивный сигнал на входах элементов И 42, поступающий с выхода 23 регистра 21, имитирует нулевое состояние всех входов мультиплексоров 46, Режим диагностики 3, Этот режим устанавливается занесением в регистр 21 кода, при котором на выходах 24 и 25 присутствуют активные уровни, состояние выходов 22 и 23 безразлично. При этом в память 7заносятся единицы независимо от текущего состояния датчиков, так как на входе элемента ИЛИ 4 с выхода 24 регистра 21 постоянно присутствует активный уровень, Режим диагностики 4. Этот режим устанавливается зане-сением в регистр 21 кода, при котором на выходе 25 присутствует пассивный уровень, состояние остальных выходов 22-23 безразлично. При этом в память 7 заносятся нули независимо от текущего состояния датчиков, так как на входе элемента И 5 с выхода 25 регистра 21, постоянно присутствует пассивный сигнал. Использование различных комбинаций режимов диагностики и запрета анализа информации отдельных выбранных датчиков позволяет произвести глубокую диагностику устройства, используя соответствующие диагностические программы. Считывание информации из буферной памяти 15 в ЭВМ может производиться в любое время, за исключение моментов записи в эту память слова сообщения, путем задания адреса считываемой ячейки через 28 узла 16 и мультиплексор 20 и считыв ния содержимого этой ячейки с выхода буферной памяти 15 через вход 20 узла 16. Запись информации в память 32 производится ЭВМ в любое время, за исключением периода действия третьего управляющего импульса узла 35, путем выдачи адреса ячейки, в которую заносится информации и собственно информация с выхода 30 узла 16 на вход мультиплексора 33. Запись информации в регистр 21 производится ЭВМ в любое время через выход 27 узла 16. ЭВМ взаимодействует с устройством черёз выход 26 и вход 48 узла 16. Блоки А1-А4 алгоритма обслуживания (фиг.З) служат для инициализации работы ЭВМ с устройством. Количество и адреса датчиков, анализ состояния которых разрешен, задается оператором или хранится в памяти ЭВМ Блоки А5, А6, А8, AlO и А13-А17 являются блоками драйвера устройства, выполняются при любом режима работы устройства и обеспечивают ввод в ЭВМ информации из буферной памяти в правильной последовательности . Состав и реализация программ бло ков А9, All и А12 зависят от алгоритмов обработки информации от датч ков конкретного технологического об рудования. Блок А7 включает в себя множеств программ, выполняемых данной ЭВМ. Эти программы могут быть как связан с обработкой информации от дискретных датчиков, так и не связаны. Основным требованием к совокупности программ блока А7 является необходи мость обеспечить выполнение условия г где Те- - средняя величина времени , выполнения всех программ блока; Л - интенсивность поступления информации о смене состояния р зрешенной группы датчиков; Тдр - среднее время выполнения драйвера устройства. При невыполнении услойия (1) происходит переполнение буферной памяти, что приводив к значительным потерям информации. При выполнении блока Б1 алгоритма тестирования (фиг.4) количество и адреса датчиков могут быть заданы оператором или определяться программой.Блоки Б2 и Б4 обеспечивают поступление от входных блоков коммутатора сигналов логической едиНИ1ДЛ и логического нуля соответственно, блоки Б6 и Б8 - подачу на устройство сигналов логической единицы и логического нуля соответственно, минуя коммутатор и линии связи между коммутатором и остальной схемой устройства. При выполнении блоков БЗ, Б5, Б7 и Б9 используется драйвер, описанный выше. БЗ и Б7 необходимы для полного заполнения памяти датчиков требуемой информацией {наличие двух , временных меток гарантирует, что проведён как минимум один цикл опроса датчиков). При положительном результате сравнения в блоке 5 выполнение теста заканчивается и может выдаваться соответствующее сообщение оператору. По результатам сравнения в блоке Б9 оператору, выдается сообщение, в котором говорится о неисправности устройства и указываются наиболее вероятные отказы. После окончания тестирования устройства в зависимости от результатов возможны следующие действия: продолжить работу устройства в режиме опроса датчиков, исключив при этом из анализа сообщения от датчиков, обслуживаемых неисправными блоками коммутатора; провести более детальную диагностику устройства и произвести останов и ремонт устройства. Таким образом, изобретение обеспечивает расширение области применения устройства и повышение достоверности обработки информации за счет . выполнения процедур сплошного и сеективного опроса и предварительной бработки информации о состояниях атчиков и контрольно-диагностичес- . их процедур в процессе реальной раоты устройства.

ftft

ts

33

4

гз

2г

«7

«/

42

ffS

иъ. Z

Начало I

l( Устанобигпь режим (мроса датчиков 1(1 I Задать текущее состояние метки

А5

Считать слово аз 6у рерной паняти по Т ABA

6 /Метка иста 6считанномслов Л7 равна

Af3

ЛПБ ТАПБ ПРЕА

Лее

MS

Инвертирове1ть ТСМл j. Af6

/глпк ГАПК

Лег

At

Фиг.З

91ипо/1мить оруъие проераммы

X/J ШЖ ГЛ/75 /

Нет Хразрвмить емамз состояния контр9Аируемо( группы 9amwffof 3a9gatb mtnyutuu аЗрее считываемой ячейки буферной пегмяти/ТАПБ/ равным .... иста/ТСМ /равным.,0

ft Ptr3fHutumii anetiua cedneginie нвмтронируенвй tpf/пяы ватлетв

I

Установить ретим duatHoemunu I

52

S3

flo yvuait 8lt метки Лреме/ и

УдтаноЙить режим Уивеноетики 2

f«

noiiyveHMеввбщеиия пизмвнении ecemofnun всея paipeitiemtHx Sem uttoluaJt O

Полууа1пь 9te нении времени . |

7 I Уетвновияь peixtiH

в

3

Пвлучени Ывбиеений eS изменении ссстоямия teex . pvaffшeltllux ittmwMtM ,0

ю

. r/ еоввшение вяервтвpy в Воиптныя Heuenpatнвстия панятч зварвсв внализв авняти светеяния SemwKOt сиены сравнения

I

A

Виват еоовщемие мкдпг-,

sn тврувввзмактх меиспра нвеяах 1хв1ныя и явннутвяврв, линии связи неяг miMjfoi парен и 9р. 9лтнт ми ycmpweaitm

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| УСТРОЙСТВО для СБОРА ИНФОРМАЦИИ от ДИСКРЕТНЫХ ДАТЧИков | 0 |

|

SU377759A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для сопряжения электроннойВычиСлиТЕльНОй МАшиНы C диСКРЕТНыМидАТчиКАМи | 1979 |

|

SU830367A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1984-04-07—Публикация

1982-10-01—Подача