(54) УСТРОЙСТВО ДЛЯ ИЗВЛЕЧЕНИЯ КОРНЯ ТРЕТЬЕЙ СТЕПЕНИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для возведения п-разрядных чисел в квадрат | 1979 |

|

SU911520A1 |

| Устройство для извлечения квадратного корня | 1978 |

|

SU773617A1 |

| Устройство для вычисления квадратного корня из суммы квадратов двух п-разрядных чисел | 1979 |

|

SU877528A1 |

| Устройство для вычисления суммы квадратов К @ -разрядных чисел | 1981 |

|

SU993256A1 |

| Устройство для вычисления скалярного произведения двух векторов | 1981 |

|

SU955088A1 |

| Устройство для решения системлиНЕйНыХ АлгЕбРАичЕСКиХ уРАВНЕНий | 1978 |

|

SU805336A1 |

| Матричный вычислитель функции @ | 1984 |

|

SU1216779A1 |

| Устройство для вычисления корней квадратного уравнения | 1980 |

|

SU999060A1 |

| Устройство для вычисления скалярного произведения двух векторов | 1981 |

|

SU1179369A1 |

| Матричный вычислитель | 1982 |

|

SU1083185A1 |

1

Изобретение относится к вычислительной технике и может быть применено автономно и в комплексе с цифровой вычислительной машиной.

Известно устройство для извлечения корня третьей степени, содержащее два счетчика, накапливающий сумматор, триггер, элемент задержки , элемент И, ИЛИ и формирователь импульсов 1 .

В этом устройстве в основу алгоритма работы положено итерационное выражение, что определяет его относительно невысокое быстродействие.

Наиболее близким по технической сущности к предлагаемому является устройство для извлечения корня треей степени, содержащее элементы И первой группы, выходы которых соединены со входами первого сумматора, элементы И второй группы, выходы которых соединены со входами второго сумматора 2,

Однако известное устройство выпоняет операцию извлечения корня третьей степени в виде последовательности шагов, что определяет его относительно невысокое быстродействие.

Цель изобретения - увеличение быстродействия устройства.

Указанная цель достигается тем, что в устройство для извлечения корня третьей степени, содержащее первую группу элементов И, первый сумматор, вторую группу элементов И, второй сумматор, введен п-разрядный вычитатель, где п-разрядность подкоренного выражения, каждый i-ый разряд которого (i 3.,., п) состо0ит из сумматора по модулю два и элемента И, первый вход которого соединен с вьлходом i-ro разряда первого сумматора (i 4,., п) и первым входом сумматора по модулю два, второй

5 вход которого соединен с разрядным входом устройства, а выход-с разрядным выходом устройства и вторым входом элемента И, выход которого соединен с входом переноса (H-l)-ro раз0ряда первого сумматора, первый и второй разрядные входы устройства соединены с первым и вторым разрядными выходами устройства соответственно, первая группа элементов И

5 выполнена в виде матрицы из двухвходовых элементов И,каждый Е -ый (К

п ,

при п четном и t 2

1

, . f

-, при п нечетном) столбец кото|; Ой содержит 26 элементов И, первые ХОДЫ которых объединены и подключены к выходу (| -е;-го, при п четном и () -го при п нечетном разряда устройства, вторые входы диагональных и каждого из параллельных диагональным элементов И матрицы объединены, вторые входы i-ых (i

3,,.,, п ) элементов И (2 1)-го

- I

при п четном и ()-го при п нечетном столбца матрицы соединены с (i-1 ым разрядньв 1 выходом устройства, выход элемента И В-го столбца i-ой строки (i 3..., п) матрицы подключен к tf -му входу i-rO разряда второго сумматора (1 3,,., п), дополнительные входы i-ых разрядов которого (при четном i) подключены к (1-1)-ым разрядньаи выходам устрой- ства, вторая группа элементов И выполнена в виде треугольной матрицы элементов И, причем первые входы элементов И К-го (К 1..., п-2 при п черном, К 1.., п-1 при п нечетном) столбца треугольной матрицы подключены к выходу (п-К+1)-го разряда второго сумматора, а вторые входы диагональных элементов И трёу1х льной матрицы объединены между собой, вторые входы элементов И (п-2)го при п четном, (п-1)-го при п не-: четном столбца (1+2)-ой строки (i 1,.., п-2) подключены к i-му разрядному выходу устройства, выход элемента И К-го столбца i-ой (i 4.,., п) строки треугольной матрицы подключен к K-Nly входу i-ro разряда первого сумматора, выход элемента И (при ) подключен к первому входу сумматора по модулю два i-ro разряда вычитателя.

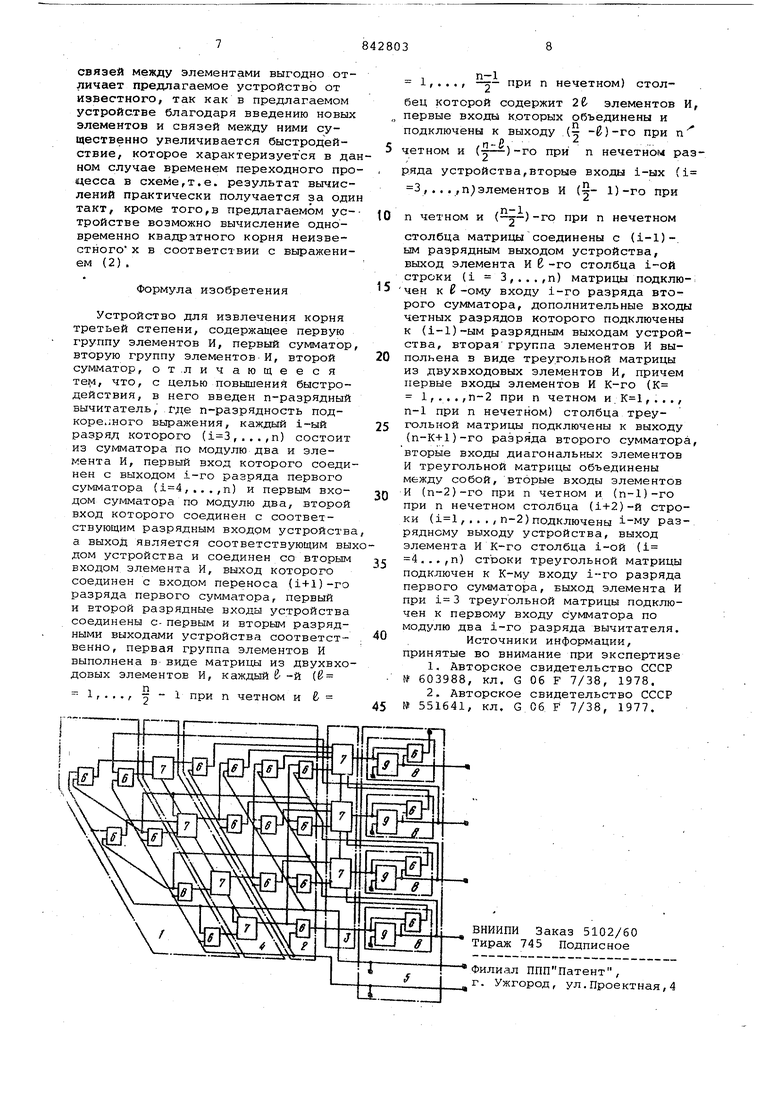

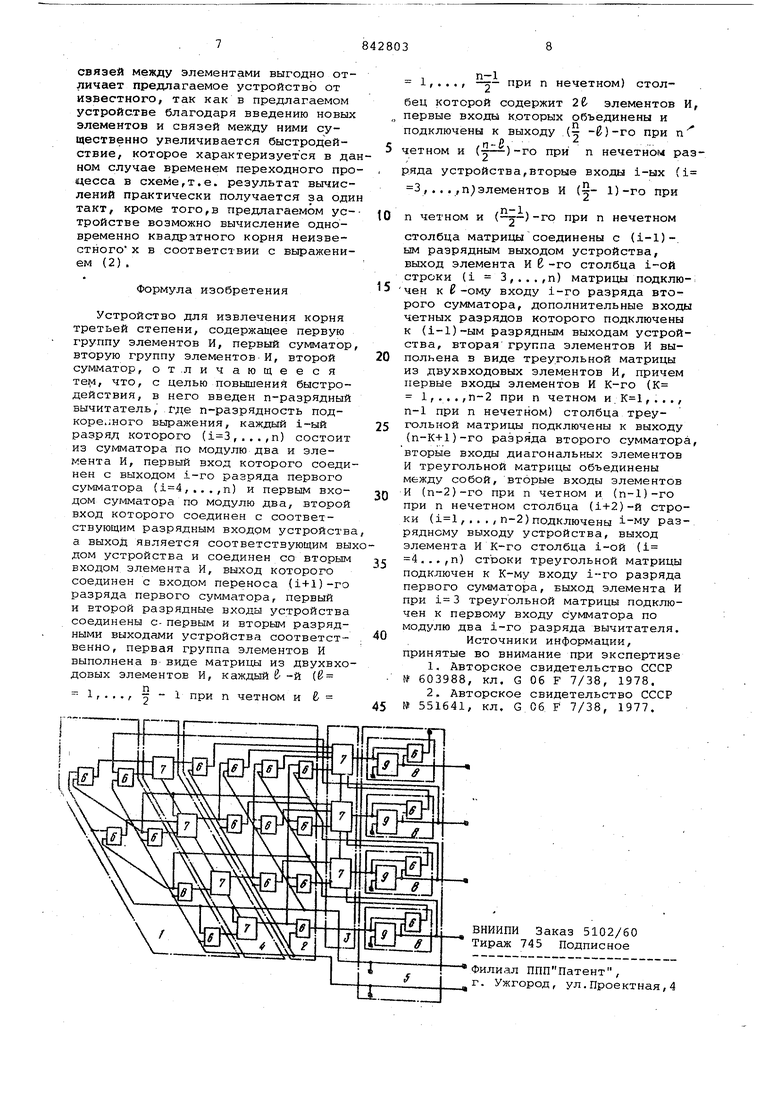

На чертеже представлена схема предлагаемого устройства для случая

||+$5

AI-b +M+Jlx+ak

ь . а э. 3|Ч хх+хх+хх

ik

когда информация представлена п 6 двоичными разрядами.

Устройство содержит элементы И 1 первой группы, элементы И 2 второй

группы, первый сумматор 3, второй румматор 4, вычитатель 5. Элементы /И 1 первой группы и второй группь 2 состоят иэ двухвходовых элементов И 6. Первый сумматор 3 и второй 4 включают одноразрядные сумматоры 7. Вычитатель 5 состоит из одноразрядных вычитателей 8, а одноразрядный вычитатель 8 - из сумматора 9 по модулю два.

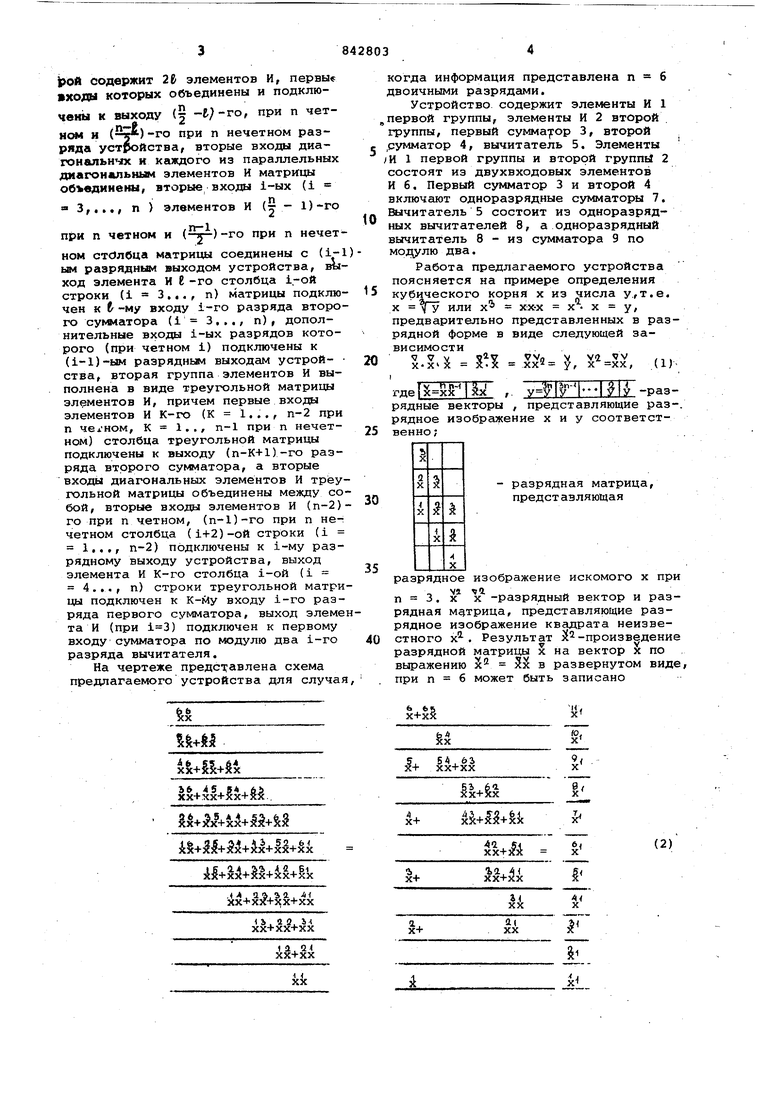

Работа предлагаемого устройства поясняется на примере определения кубического корня х из числа у,т.е. X Vy или X хх-х X . X у, предварительно представленных в разрядной форме в виде следующей зависимости

7 V Уо у уа. У

7 V „ V va v ... ХХХ ХХ xx у, X хх, (1)

ЗННЖ-РазГУ п пч I а I где i I XX ,

г-„.,:- , представляющие разрядные векторы рядное изображение х и у соответственно;

- разрядная матрица, предст авляюадая

разрядное изображение искомого х при

п 3. X х -разрядный вектор и разрядная матрица, представляющие разрядное изображение квадрата неизвестного х . Результат }{2-произведение разрядной матрицы х на вектор х по выражению х 5х в развернутом виде, при п б может быть записано

М,

х+х

х

IL

§

(2)

Л J

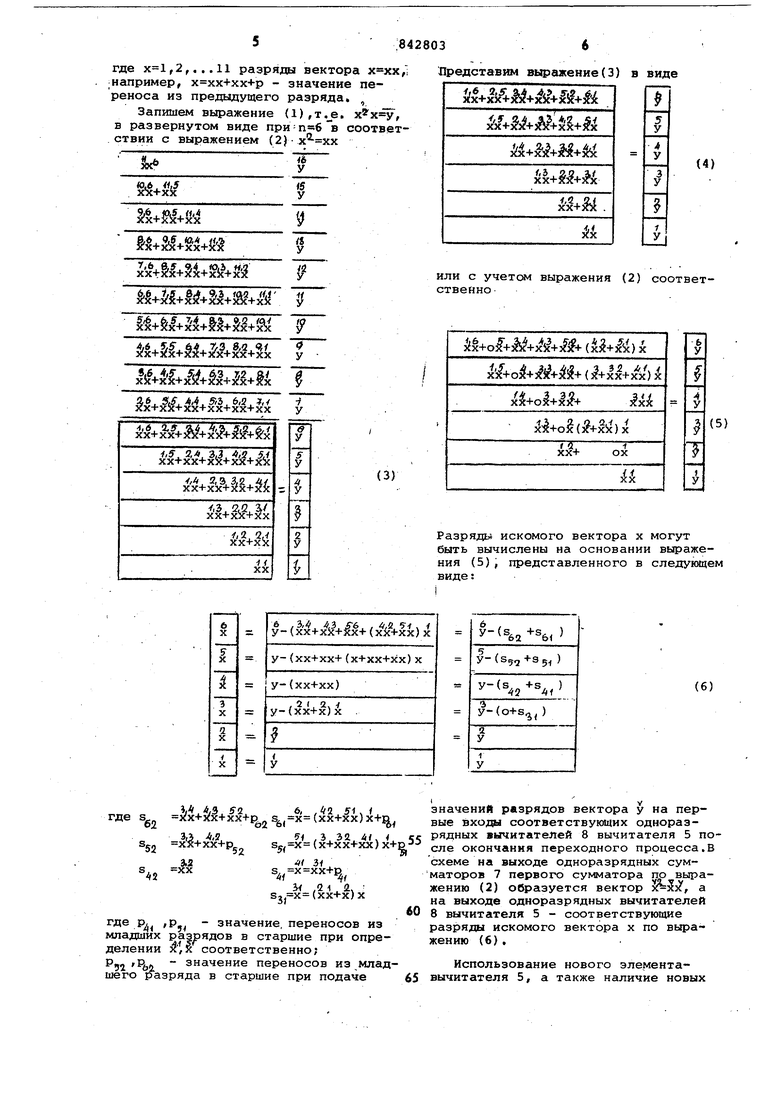

±. i где ,2,...ll разряды вектора x-xXf. ;например, х хх+хх+р - значение переноса из предыдущего разряда, , Запишем выражение (1),т.е. , в развернутом виде при соответствии с выражением (2) где s :i x+j x+xx+| 2 ) .3 32 4. xx+xx+p Sy,x (x+xx+xx) x 3 . % - -- J Si , s,x(xx+x)x ,p - значение, переносов из младших разрядов в старшие при определении соответственно; а%i значение переносов из млад шего разряда в старшие при подаче 8428

.

(2) соответили с учетом выражения ственноРазряды искомого вектора х могут быть вычислены на основании выражения (5), представленного в следующем виде:

У-( 5

y-(S55+S5

(6)

y-(o+s) 036 Лредставим выражение(3) в виде м+м+ значений разрядов вектора у на первые входы соответствующих одноразрядных вычитателей 8 вычитателя 5 после окончания переходного процесса.В схеме на выходе одноразрядных сумматоров 7 первого сумматора по выражению (2) образуется вектор , а на выходе одноразрядных вычитателей В вычитателя 5 - соответствующие разряды искомого вектора х по выражению (6) . Использование нового элементавычитателя 5, а также наличие новых

Авторы

Даты

1981-06-30—Публикация

1979-05-07—Подача