(,54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ КВАДРАТНОГО КОРНЯ ИЗ СУММЫ КВАДРАТОВ ДВУХ п-РАЗРЯДНЫХ ЧИСЕЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для извлечения квадратного корня | 1981 |

|

SU1015378A1 |

| Устройство для вычисления квадратного корня | 1981 |

|

SU1053105A1 |

| Вычислительное устройство | 1981 |

|

SU1086426A1 |

| Устройство для возведения п-разрядных чисел в квадрат | 1979 |

|

SU911520A1 |

| Вычислительное устройство | 1981 |

|

SU1115047A2 |

| Устройство для вычисления суммы квадратов К @ -разрядных чисел | 1981 |

|

SU993256A1 |

| Устройство для извлечения квадратного корня | 1979 |

|

SU857981A1 |

| Устройство для вычисления зависимости @ = @ + @ + @ | 1981 |

|

SU1019446A1 |

| Устройство для извлечения квадратного корня | 1978 |

|

SU773617A1 |

| Множительно-делительное устройство | 1981 |

|

SU1267407A2 |

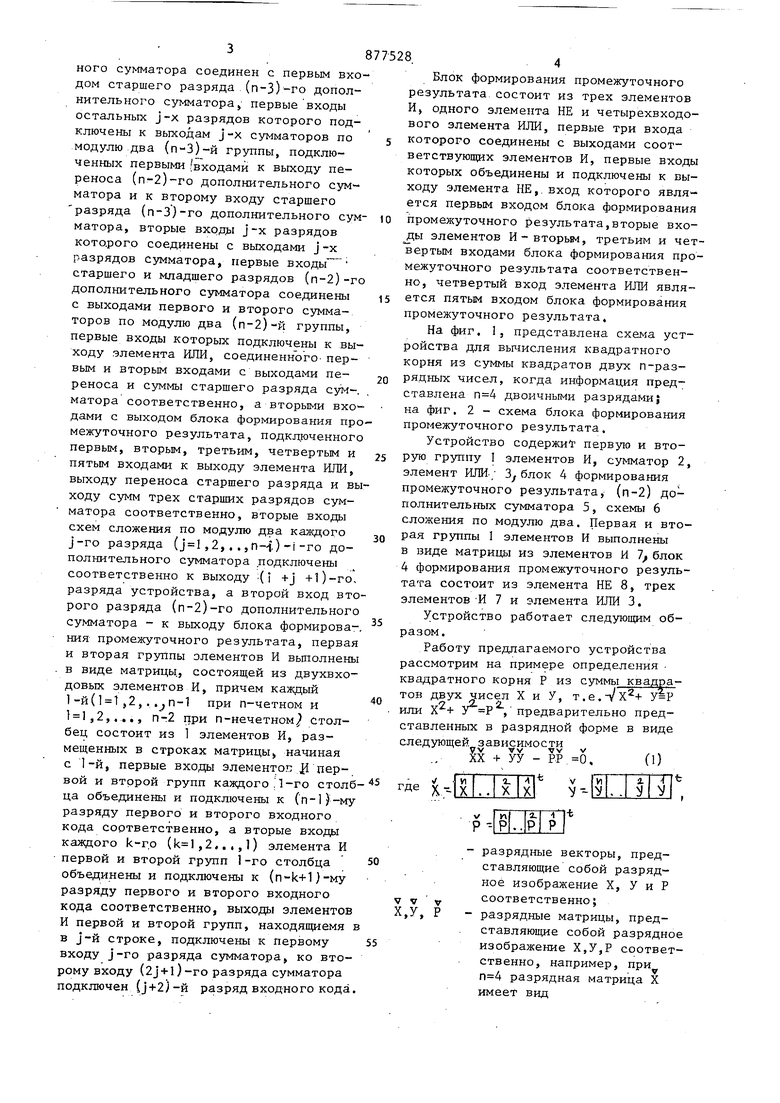

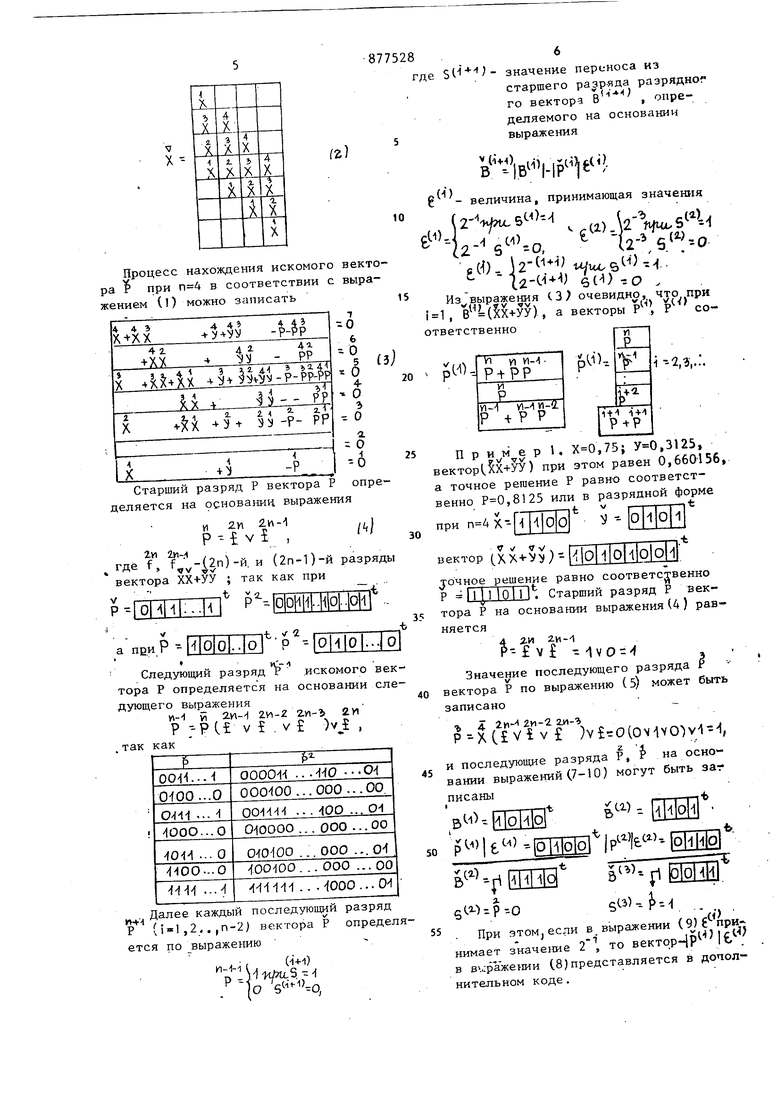

Изобретение относится к вычислительной технике и может быть применено автономно либо в комплексе с цифровой вычислительной машиной. Известно устройство для вычисления квадратного корня из суммы квадратов двух , содержащее два бло ка выделения модуля, сумматор, схему сравиения, коммутатор |,11« В известном устройстве вычисление квадратного корня из суммы квадратов двух чисел осуществляется за относительно большой промежуток времени. Наиболее близким по технической сущности к предлагаемому является уст ройство, содержащее две группы элемен тов И, су№1атор {2. Однако устройство вьтолняет операцию вычисления квадратного корня из суммы квадратов двух чисел в виде последовательности шагов, что опреде ляет его относительно невысокое быст родействие . Цель изобретения - увеличение быстродействия устройства. Указанная цель достигается тем, что в устройство для вьиисления квадратного корня из суммы квадратов двух п-разрядных чисел, содержащее первую, вторую группы элементов И и сумматор, введены элемент ИЛИ, блок формирования промежуточного результата, п-2 дополнительных сумматоров И п-2 группы сумматоров по модулю два, причем выход каждого j-ro (j 1 ,2. .. ,n-i) кроме (n-i)-ro разряда, )-ro ( ,2,.. jn-) дополнительного сумматора подключен к первому входу (j+1)-го. разряда i-го дополнительного сумматора, второй вход разряда которого подключен к выходу j-ro сумматора по модулю два 1-й группы, подключенного своим первым входом к выходу переноса и второму входу старших разрядов (i + l)-ro и I-годополнительных сумматоров, выход младшего разряда (п-2)-го дополнительного cyNfMaropa соединен с первым входом старшего разряда (п-3)-го дополнительного сумматора первые входы остальных J-X разрядов которого подключены к выходам J-X сумматоров по модулю два (п-З)-й группы, подключенных первыми /входами к выходу переноса (п-2)-го дополнительного сумматора и к второму входу старшего разряда (п-3}-го дополнительного сум матора, вторые входы j-x разрядов которого соединены с выходами j-х разрядов Сумматора, первые входы старшего и младшего разрядов (п-2)-го дополнительного сумматора соединены с выходами первого и второго сумматоров по модулю два (п-2)-и группы, первые входы которых подключены к выходу элемента РШИ, соединенного- первым и вторым входами с выходами переноса и суммы старшего разряда сум-. матора соответственно, а вторыми входами с выходом блока формирования про межуточного результата, подключенного первым, вторым, третьим, четвертым и пятым входами к выходу элемента ИЛИ, выходу переноса старшего разряда и вы ходу сумм трех старших разрядов сумматора соответственно, вторые входы схем сложения по модулю два каждого j-ro разряда (,2,..,П-4)-i-го дополнительного сумматора .подключены соответственно к выходу ( i +j +l)-ro, разряда устройства, а второй вход вто рого разряда (п-2)-го дополнительного сумматора - к вькоду блока формирования промелсуточного результата, первая и вторая группы элементов И выполнены . в виде матрицы,, состоящей из двухвходовых элементов И, причем каждый 1-й(,2,...п-1 при п-четном и ,2,..,, п-2 при п-нечетном столбец состоит из 1 элементов И, размещенных в строках матрицы начиная с 1-й, первые входы элементов Ji первой и второй групп каждого.1-го столб ца объединены и подключены к (п-1)-му разряду первого и второго входного кода соответственно, а вторые входы каждого k-rp (,2,.,,l) элемента И первой и второй групп 1-го столбца объединены и подключены к (n-k+1)-My разряду первого и второго входного кода соответственно, выходы элементов И первой и второй групп, находящиемя в j-й строке, подключены к первому входу j-ro разряда сумматора, ко второму входу (2j + l)-ro разряда сумматора подключен ij+2) -и разряд входного кода 4 Блок формирования промежуточного результата состоит из трех элементов И, одного элемента НЕ и четырехвходового элемента ИЛИ, первые три входа которого соединены с выходами соответствующих элементов И, первые входы которых объединены и подключены к выходу элемента НЕ,, вход которого является первым входом блока формирования промежуточного результата,вторые входы элементов И-вторьм, третьим и четвертым входами блока формирования промежуточного результата соответственно, четвертый вход элемента ИЛИ является пятым входом блока формирования промежуточного результата. На фиг. I, представлена схема устройства для вычисления квадратного корня из суммы квадратов двух, п-разрядных чисел, когда информация представлена двоичными разрядами; на фиг, 2 - схема блока формирования промежуточного результата. Устройство содержиг первую и вторую группу I элементов И, сумматор 2, элемент РШИ-; 3, блок 4 формирования промежуточного результата, (п-2) дополнительных сумматора 5, схемы 6 сложения по модулю два. Первая и вторая группы I элементов И выполнены в виде матрицы из элементов И 7 блок 4 формирования промежуточного результата состоит из элемента НЕ 8, трех элементов -И 7 и элемента ИЛИ 3, Устройство работает следующим образом. Работу предлагаемого устройства рассмотрим на примере определения квадратного корня Р из суммы квадратов двух чисел X и У, T.e. или , предварительно представленных в разрядной форме в виде следующей зависимости Н + УУ - РР разрядные векторы, представляющие собой разрядное изображение X, У и Р соответственно; разрядные матрицы, представляющие собой разрядное изображение Х,У,Р соответственно, например, при разрядная матрица X имеет вид

V

X -Процесс нахождения искомого ра Р при в соответствии с можно записать жением Старший разряд Р вектора Р деляется на ocHosaifflH выражени и 2У 2.И--1 P---EV , гм 2м-1 где f, (2п-1)-й р вектора ХХ+УУ ; так как при р ГШЕППШ шМжй а пвиР - -flQlPl. Следующий разряд Р искомо тора Р определяется на основани дующего выражения и-- и 2И- 2.П-Ъ 2V Р ;РС V f . v )v так как

., Далее каждый последуюшяй

. V

Р 1«,2..,п-2) вектора Р ется по выражению

И-1-1(. 2:) Р П -К/таЗ - -1

г -S (;.и1

)

О 6

О,

8775286

где )- значение переноса из

старшего разр-яда раэрядног го вектора , определяемого на основании выражения

V (),

.()

- величина, принимающая значения

SW)-.-..

.р-.о

сСО.

При этом,если в выражении (9)8 при нимает значение , то векторЦр li . в в.;ражении (.8) представляется в дополнительном коде. ( ,, , рШ. 2- u/ux.. -() 4t) -.0 . Из выражения СЗ; очевидно, что при , В (ХХ+УУ), а векторы соi --2, г,.:. П Р Р I. ,75{ ,3125, вектор1,5х+УУ) при этом равен 0,660-156, а точное решение Р равно соответственно ,8125 или в разрядной форме при X вектор (XX-t-V }-И OhlohJOJoHl jo4Hoe решение равно соответственно Р 11 11 loin , Старший разряд Р вектора Р на основании выражения(4 ) равняется4 2.И 2.И--1 -. г Значение последующего разряда вектора Р по выражению (5) может быть записано Ч, 4 2м--г ))v/l-, И последующие разряда Р, Р на основании выражений (7-10) могут быть заг П р и м е р 2. Х«0,4375; ,375 соответственно ХХ+УУ 0,332031 и .76221 или в разрядной форме у г г . -l-lt- V ,1- 1-1-it X-phH V (х- 55-Г- fPHJoMfoHloR HloloN -ivo-fpioc-i vovDvo a . в -- Rraiol ЩоШ -- ШН - №р1о р-О -1 Работа предлагаемого устройства для конкрет{|ых значений X И У рассмотренных выше примеров происходит следующимобразом. При подаче| значений и У на входы первой -и второй группы 1 элементов И после окончания переходного процесса в схеме на выходе переноса старшего разряда и выходах суммы сумматора 2 образуется вектор СХХ + ЗТ),.на выходе элемента ИЛИ 3 по выражению (4J образуется страший разряд искомого .вектора Р , на выходе блока 4 по выражению(5) образуется значение последующего разряда вектора Р, а на выходах переносов до полнительных сумматоров 5 по выражениям (7-10) образуются соответствующие разряды искомого вектора Р. Формула изобретения 1, Устройство для вычисления квад ратного корня из суммы квадратов дву П-разрядных чисел, содержащее первую вторую группы элементов И и сумматор о тличающееся тем, что, с целью увеличения быстродействия, в него введены элемент КИИ, блок форми рования промежуточного результата, (п-2) дополнительных сумматоров и пгруппы сумматоров по модулю два, при чем выход каждого j-ro (j 1,2,..,, f1-l), кроме (n -i)-ro разряда, (i + U го (,2,., n-l) дополнительного су матора подключен к первому входу (j + l)-ro разряда 1-го дополнительног сумматора, второй вход разряда которого подключен к выходу j-ro сумма - тора по модулю два i-и .группы, подключенного свйим первым входом к выходу переноса и первому входу старших разрядов (l-fU-ro и 1-го допол1штельных сзТФ1аторов, выход младшего разряда (п-2) -го дополнительного суммато-ра соединен с первым входом старшего разряда (п-3)дополнительного сумматора, первые входы остальных j-x разрядов которого, подключены к выходам j-x сумматоров по модулю два (п-З)-й группы, подключенных первыми входами fe выходу переноса (п-2)-го дополнительного сумматора и к второму входу старшего разряда (п-З)-го дополнительного сумматора, вторые входы j-x разрядов которого соединены с выходами j-x разрядов сумматора, первые входы старшего и младшего разрядов (п-2)-го дополнительного сумматора соединены с выходами первого и второго сумматоров по модулю два )-й группы, первые входы которых подключены к ВЫХОДУ элемента ИЛИ, соединенного первым и вторым входами с выходами переноса и суммы старшего разряда сумматора соответственно, а вторыми входами с выходом блока формирования промежуточного результата, подключенного первым, вторым, третьим, четвертым и пятым входами к выходу элемента ИЛИ, выходу переноса старшего разряда и выходам сумм трех старших разрядов сумматора соответственно, вторые входы сумматоров по модулю два каждого j-rp разряда (,2,..,п-}) i-го.дополнительного сумматора под.ключены соответственно к выходу (i-HJ- +l)ra разряда устройства,а второй вход второго разряда (n-2j-ro дополнительного сумматора - к выходу блока формирования промежуточного результата, первая и вторая группы элементов И выполнены в виде матрицы, состоящей из двухвходовых элементов И, причем каждый 1-й (,2,..n-l при П четном и ,2,...п-2 при П нечетном) столбец состоит из 1 элементов И, размещенных в строках матрицы, начиная с 1-й, первые входы элементов И первой и второй групп каждого столбца объединены и подключен ; к (п-1)-му разряду первого и второго входного кода соответственно, а вторые входы каждого (kel,2,..l) элемента И первой и второй групп 1 то столбца объединены и подключены к iTi-k-fl)-My разряду первого и второго кода соответственно, выходы элементов И первой и второй rpjmn, находящиеся в j-й строке подключены к первому входу j-го разряда сумматора, ко второму входу (2j-f1)uro разряда сумматора, ко второму входу (2J 1)-го разряда сумматора подключен (j+2)-и разряд входного кода.

Источники информации, принятые во внимание при экспертизе

2,Авторское свидетельство СССР

№ 627477, кл. G 06 F 7/38, 1978 (прототип).

Авторы

Даты

1981-10-30—Публикация

1979-06-25—Подача