рой и третий гходы пятого и шестого элементов 2И-ИЛИ соединены с вторым разрядом первого информационного входа функционального переключателя, , четвер1тый вх:од пятого и второй вход шестого элементов 2И-ИЛИ соединены с третьим разрядом первого информационного входа функционального переключателя, второй вход первого, четвертый вход второго и третий вход четвертого элементов 2И-ИЛИ соединены с втррым информационным входом функционального переключателя, третий вход первого элемента 2И-ИЛИ соединен с входом старшего разряда функционального переключателя, выход второго элемента 2И-ИЛИ соединен с первым выходом функционального переключателя, второй выход которого соединен с выходом четвертого элемента 2И-ИЛИ, выходы третьего, пятого и шестого элементов 2И-ИЛИ соединены с третьим выходом функционального переключателя, выход старшего разряда которого соединен с выходом первого элемента 2И-ИЛИ.

3. Вычислитель по п. 1, отличающийся тем, что (i +1)-й функциональный переключатель содержи {i+7) элементов 2И-ИЛИ, первые входы которых соединены с управляющим входом функционального переключателя , первый выход которого соединен с выходами элементов 2И-ИЛИ с третьего по (1+7)-й, втоЕжае входы элементов 2И-ИЛИ с третьего по

(i+6)-H соединены с выходом первого элемента 2И-ИЛИ, третьи входы (т+3)-ги- (i+4)-ro элементов 2И-ИЛИ соединены с первым разрядом первого информационного вх-ода функционального переключателя, второй разряд первого информационного входа которого соединен с третьими входами (i-b6)-ro и {i+7)-ro элементов 2И-ЙЛИ четвертый вход (i+6)-ro и второй вход (i+7)-ro элементов 2И-ИЛИ соединены с третьим разрядом первого информационного входа функционального переключателя, второй и третий .входы второго элемента 2И-ИЛИ соединены с вторым информационным входом функционального переключателя, второй вход первого элемента 2И-ИЛИ соединен с вторым входом второго эле- . f мента 2И-ИЛИ и с вторым информационным входом и выходом старшего разряда функционального переключателя, выход второго элемента 2И-ИЛИ соединен с вторым выходом функционального переключателя, третий входвторого элемента 2И-ИЛИ соединен с входом старшего разряда функционального переключателя, третий вход (г+3)-го элемента 2И-ИЛИ (,2,,.., i ) соединен с соответствующим разрядом третьего информационного входа функционального переключателя, выход которо го соединен с выходом (т+5)-го элемента 2И-ИЛИ, выход второго элемента 2И-ИЛИ соединен с вторым выходом функционального переключателя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричный вычислитель | 1983 |

|

SU1137464A1 |

| Матричный вычислитель функции @ | 1984 |

|

SU1216779A1 |

| Устройство для вычисления логарифмов чисел | 1980 |

|

SU932491A1 |

| Матричное устройство для деления | 1985 |

|

SU1247863A1 |

| Множительно-делительное устройство | 1980 |

|

SU920712A1 |

| Универсальное суммирующее устройство | 1990 |

|

SU1786484A1 |

| Устройство для возведения в квадрат и извлечения квадратного корня | 1987 |

|

SU1413627A1 |

| Устройство для вычисления зависимости @ = @ + @ + @ | 1981 |

|

SU1019446A1 |

| Устройство для вычисления суммы квадратов К @ -разрядных чисел | 1981 |

|

SU993256A1 |

| Устройство для вычисления давления в узле трубопроводной системы | 1983 |

|

SU1170460A1 |

1. МАТРИЧНЫЙ ВЫЧИСЛИТЕЛЬ, содержащий (п-1) сумматоров ( П - разрядность выходного кода) и элемент ИЛИ, входы которого соединены с входами двух старших разрядов аргумента устройства, выход j-ro разряда (J3B2,3,..., i+2) i-го сумматора (,2,..., n-2) соединен с (j-l)-M разрядом первого входа (i+1)-го сумматора, отличающийся гем, что, с целью расширения класса решаемых задач путем дополнительной Возможности вычисления обратной функции помимо пряглой, в него введены (и -1) функциональных переключателей, одноразрядный сумматор и коммутатор, причем управляющие входы функциональных переключателей и ,коммутатора и младшие разряды первых входов сумматоров соединены с управляющим вхог дом вычислителя, первый выход (i+l)го функционального переключателя соединен с вторым входом 1-го сумматора, первый вход

Изобретение относится к вычислительной технике и может быть применено в качестве спецпродессора в комплексе с цифровой вычислительной машиной для оперативного вычисления операции корня квадратного или квадрата числа.

Известно устройство для извлечения квадратного корня, содержащее {п-1) группу последовательно соединенных одноразрядных сукматоров, группу сумматоров по модулю два, группу элементов ИЛИ, группу элементов НЕ, (п-2) дополнительные груп пы из (n-i-i) сумматоров по модулю два в каждой, группу элементов И и генератор единиц, причем выход каждого j-ro (,2,...,2+i) одноразрядного сумматора i-й группы (i 1,2,...п) соединен с первым входом (j-l)-ro одноразрядного сумматора (И-1)-й группы С ЗНедостатком данного устройства является ограниченный класс решаемых

задач из-за того, что.в устройстве реализуется тольк.о операция извлечения квадратного корня.

Наиболее близким к предлагаемому по технической сущности является устройство, содержащее (п-1) группу последовательно соединенных одноразрядных сумматоров по (2+i) в каждой i-й группе, группу- сумматоров по

модулю два, группу элементов ИЛИ,,группу элементов НЕ, группу из (п-2) элементов И и генератор единиц, причем выход каждого j-ro одноразрядного сумматора (,2,...,2+1)

(1+1)-й группы соединен с первым входом (j-l)-ro одноразрядного сумматора i-й группы 2J.

Недостатком известного устройства является ограниченный класс решаемых задач, определяемый тем, что в нем

реализуется только одна функция и не реализуется обратная.

Цель изобретенная - расширение класса решаемых задач за счет дополнительной возможности вычисления обратной функции у j/lt.

Поставленная цель достигается там, что в матричный вычислитель, содержащий (п-1) сумматоров (п- разрядность выходного кода) и элемент ИЛИ, входы которого соединены с входами двух старших разрядов аргумента устройства, выход j-ro разряда (,3,...,1+2) i-ro сумматора (,2,...,п-2) соединен с (j-l)-M разрядом первого входа (i+l)-ro сумматора, йведены (п-1) функциональных переключетелей, одноразрядный сумматор и коммутатор, причем управляющие входы функциональных переключателей и коммутатора и младшие разряды первых входов сумматоров соединены с уп равляющим входом вычислителя, первый выход (1+1)-го функционального переключателя соединен с вторым входом 1-го сумматора, первый информационный вход (к+1 )-го .функционально.го переключателя (,1,2,... п-2) соединен с (2к+2)-м, (2к+3)-м и (2к+4)-м разрядами входа аргумента вычислителя, выход переноса и старшего разряда суммы 1-го сумматора соединен с вторым информационным входом (H-l)-ro функционального переключателя, выход элемента ИЛИ соединен с вторым информационным входом первого функционального переключателя, первый и второй информационные вхОды коммутатора соединены соответственно с выходом переноса старшего разряда первого сумматора и выходом старшего разряда третьего функционального переключателя, выход которого подключен к входу переноса одноразрядного сумматора, разрядный вход которого соединен с первым выходом первого функционального перёключа- теля, вход старшего разряда (2+2)-го функционального переключателя соединен с выходом старшего разряда (2+3)го функционального переключателя (,2,..., п-4), вход старшего разряда первого функционального переключателя соединен с выходом старшего разряда второго функционального переключателя, выход (п-1)-го сумматора и вторые выходы функционал1ьных переключателей соединены с выходом устройства, третий выход 1-го функционального переключателя соединен с (1+1)-м разрядом третьего информационного входа т-го функцио-; нального переключателя (,i+lr... п-1), третий выход первого функционального переключателя соединен с разрядным входом п-ервого сумматора, выход одноразрядного сумматора еоеди)1ен с вторым информационным входом второго функционального переключа геля.

Причем первый функциональный переключатель содержит шесть элементов 2И-ИЛИ, первые входы которых соединены с управляющим входом первого функционального переключателя, 5 вторые входы второго, третьего и четвертого элементов 2И-ИЛИ соединены с первым разрядом nepBOio информационного входа функционального переключателя, третий вход второго,

10 четвертый вход третьего, второй и третий входы пятого и шестого элементов 2И-Ш1И соединены с вторым разрядом первого информационного входа функционального переключателя,

15 четвертый вход пятого и второй вход шестого элементов 2И-ИЛИ соединены с третьим разрядом первого информационного входа функционального переключателя, второй вход первого, чет20 вертый вход второго и третий вход четвертого элементов 2И-ИЛИ соединены с вторым информационным входом функционального переключателя, третий вход первого элемента 2И-ИЛИ соеди25 нен с входом старшего разряда функционального переключателя, выход второго элемента 2И-ИЛИ соединен с первым выходом функционального переключателя , второй выход которого

Q соединен с выходом четвертого эле- мента 2И-ИЛИ, выходы третьего, пятого и шестого элементов 2И-ИЛИ соединены с третьим выходом функционального переключателя, выход старшего разряда которого соединен с выходом первого элемента 2И-ИЛИ.

При этом (1+1)-й функциональные переключатель содержит (1+7) элементов 2И-ИЛИ, первые входы которых

( соединены с управляющим входом функционального переключателя, первый выход которого соединен с выходами элементов 2И-ИЛИ с третьего по(1+7)-й, вторые входы элементов

2И-ИЛН С| третьего по (1+6)-й соединены с выходом первого элемента 2И-ИЛИ, третьи входы (1+3)-го и (1+4)-го элементов 2И-ИЛИ соединены с первым разрядом первого информационного входа функционального

переключателя, второй разряд первого информационного входа . которого соединен с третьими входами (1+б)-го и (1+7)-го элементов 2И-ИЛИ, четвертый вход (1+6)-го и второй вход

5 (1+7)-го элементов 2И-ИТО1 соединены с третьим разрядом первого информационного входа функционального переключателя, второй и третий входы второго элемента 2И-ИЛИ соединены

0 с вторым информационным входом функционального переключателя, второй вход первого элемента 2И-ИЛИ соединен с вторым входом второго элемента 2И-ИЛИ и с вторым информационным вхо5 дом и выходом старшего разряда функционального переключателя, выход второго элемента 2И-ИЛИ соединен с вторым выходом функционального переключателя, третий вход второго элемента 2И-ИЛИ соединен со входом старшего разряда функционального переключател третий вход (г+3)-го элемента 2И-ИЛИ (,2,..,,i) соединен с соответствующим разрядом третьего информационного входа функционального переключателя, выход которого соединен с выходом (i+5)-ro элемента 2И-ИЛИ, выход второго элемента 2И-ИЛИ соединен с вторым выходом функционального переключателя.

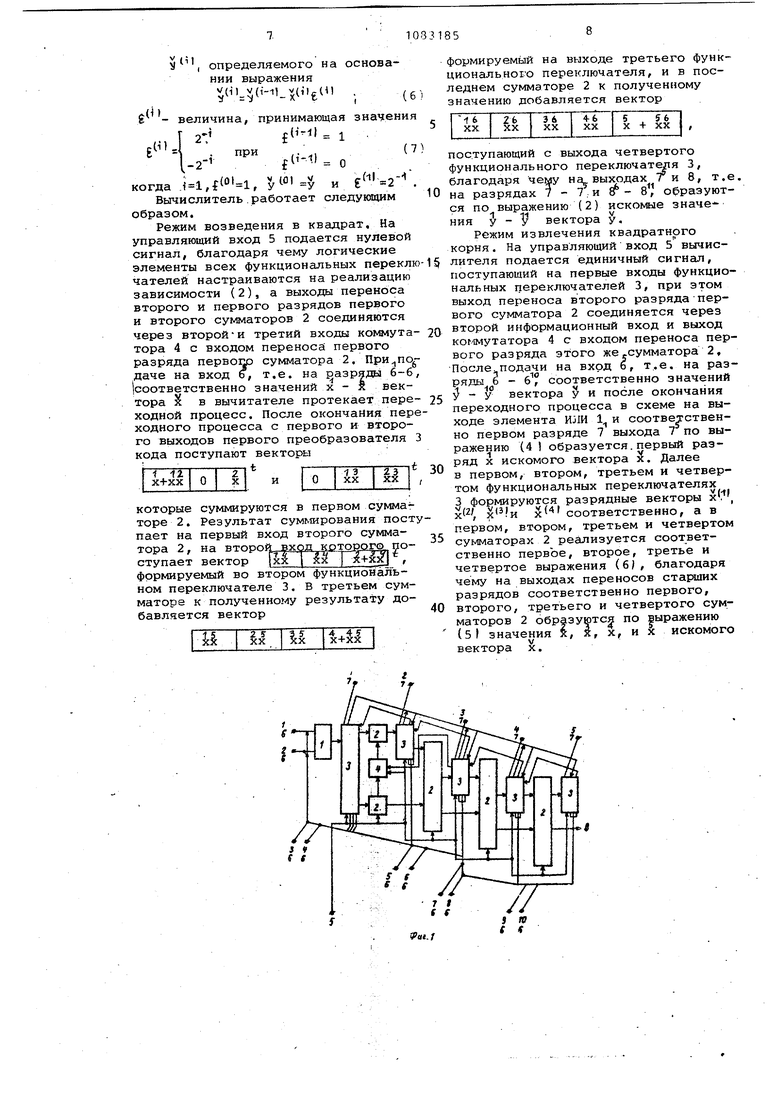

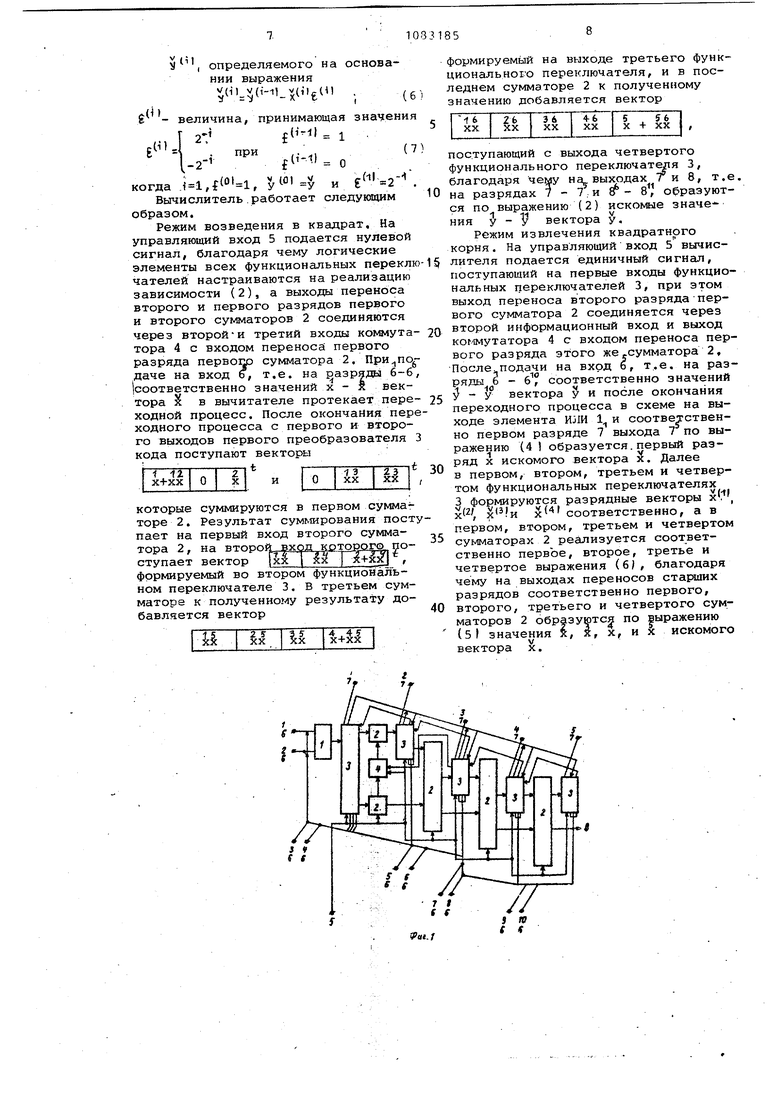

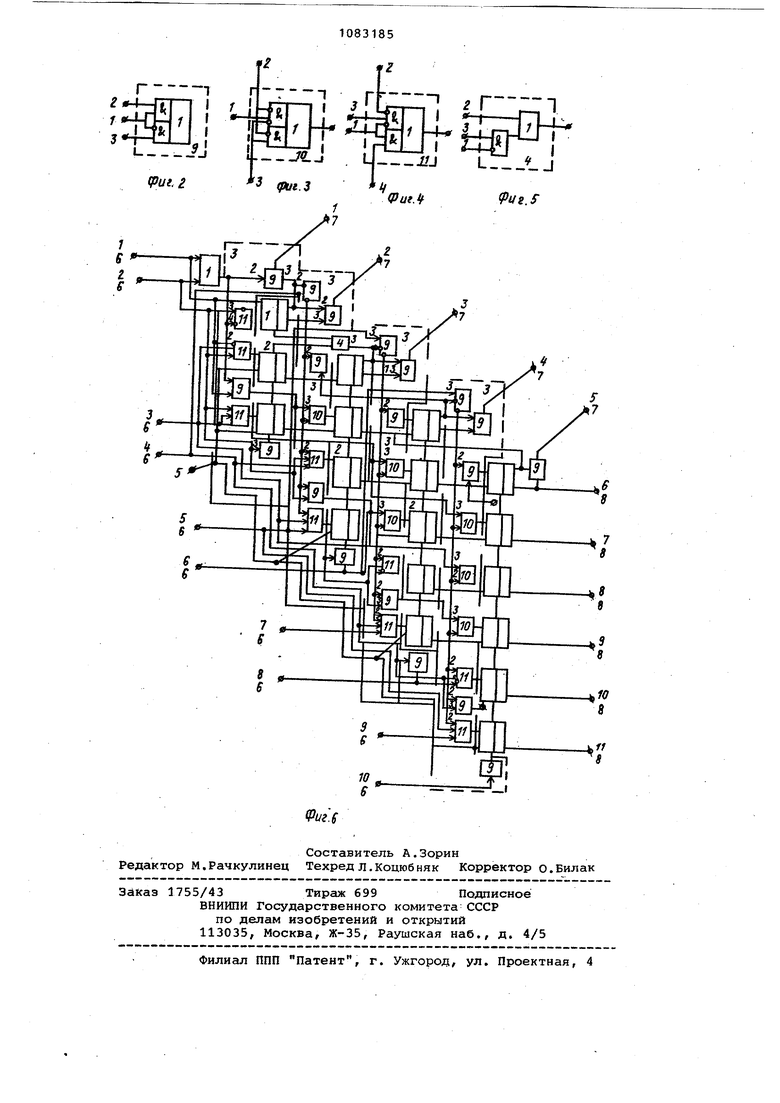

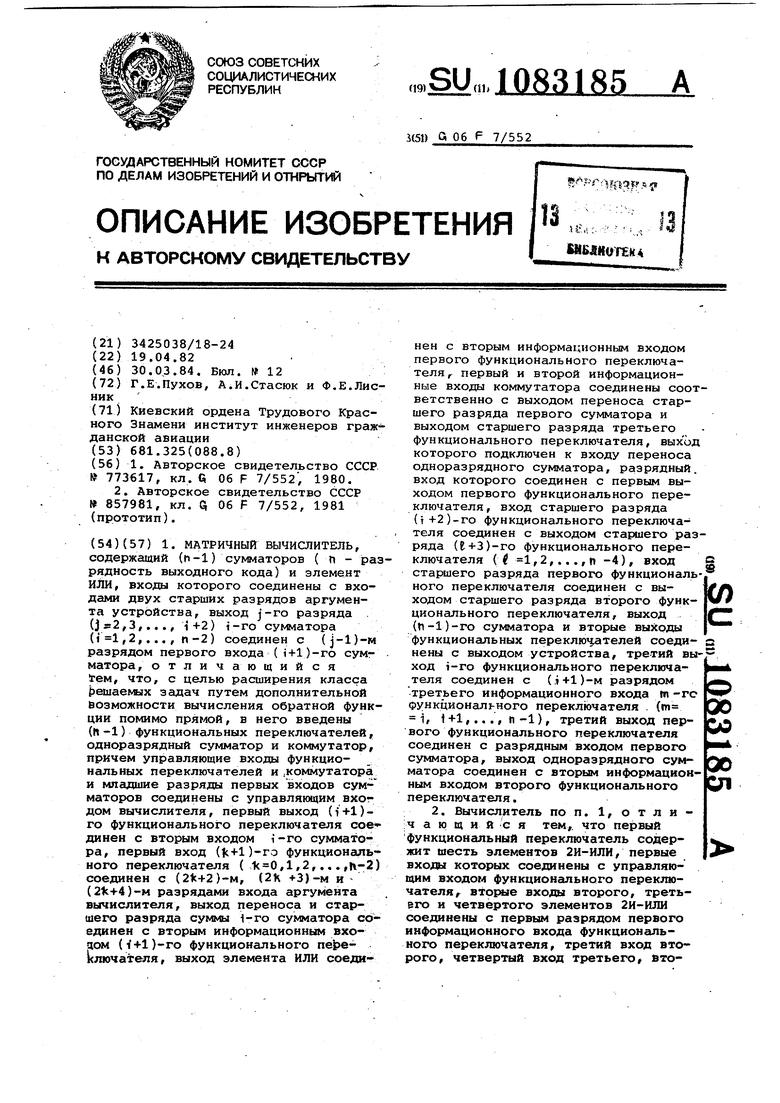

На фиг. 1 представлена блок-схема предлагаемого вычислителя; на фиг. 2-4 - логические элементы 2И-ИЛ используемые в функциональных переключателях; на фиг. 5 - схема коммутатора; на фиг. 6 - блок-cxeiyia варианта реализации вычислителя ().

Матричный вычислитель содержит . элемент ИЛИ 1, сумматоры 2, переключатели 3 кода, коммутатор 4, управляющий вход 5, вход 6, а также,выхода 7 и 8. Функциональные переключатели содержат элементы 2И-ИЛИ 9-11.

Работу матричного вычислителя объясним на примере определения функ.2

ции вида и обратной функции .

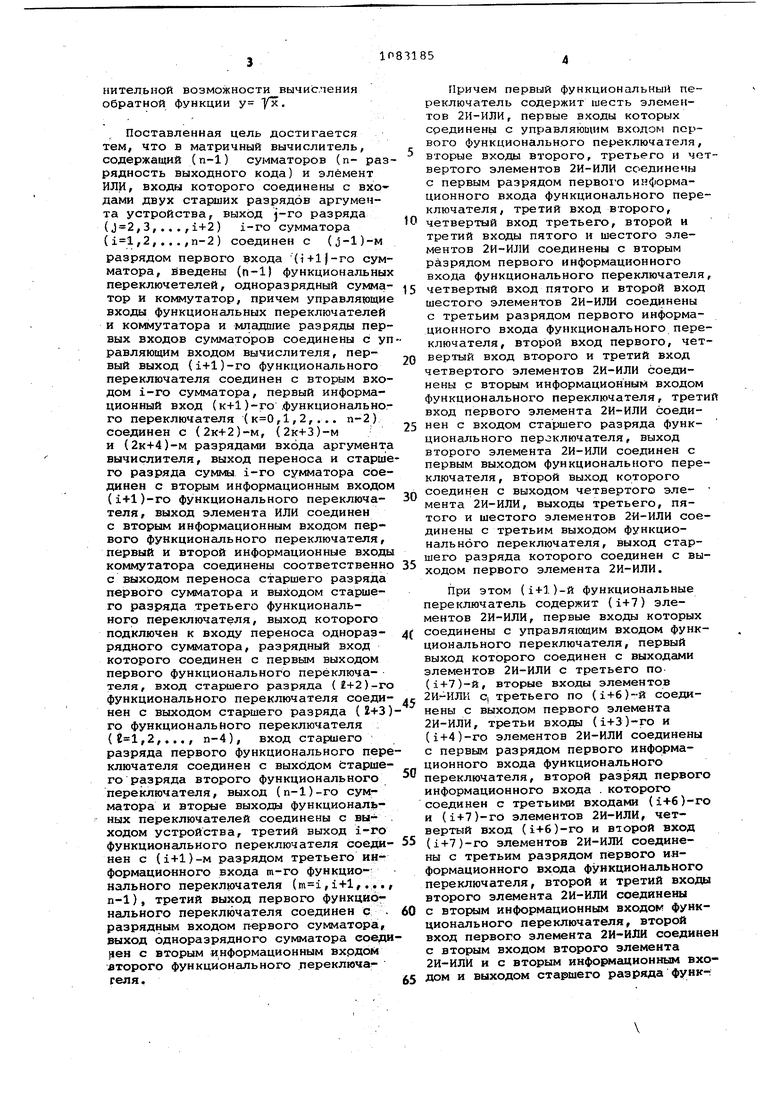

Операция возведения в квадрат. Представим выражение в разрядной форме

бой разрядное изображение х и у соответственно;

- разрядная

матрица, пред- 50 ставляющая собой изображения X при

.

Процесс нахождения искомого вектора у в соответствии с выражением (1) при может быть представлен в 60 виде

у

«

112

У Х+Х X

1 3

у XX

2,23,24 Х+ХХ+ХХ

(2)

+М+У

3 5 XX

ч 4S х+хх

10

у

Операция иэвлечения квадратного корня. Для определения значений разрядов X искомого вектора х представим выражение (1) как Jf - Зс О и запишем в развернутой форме, при .

3)

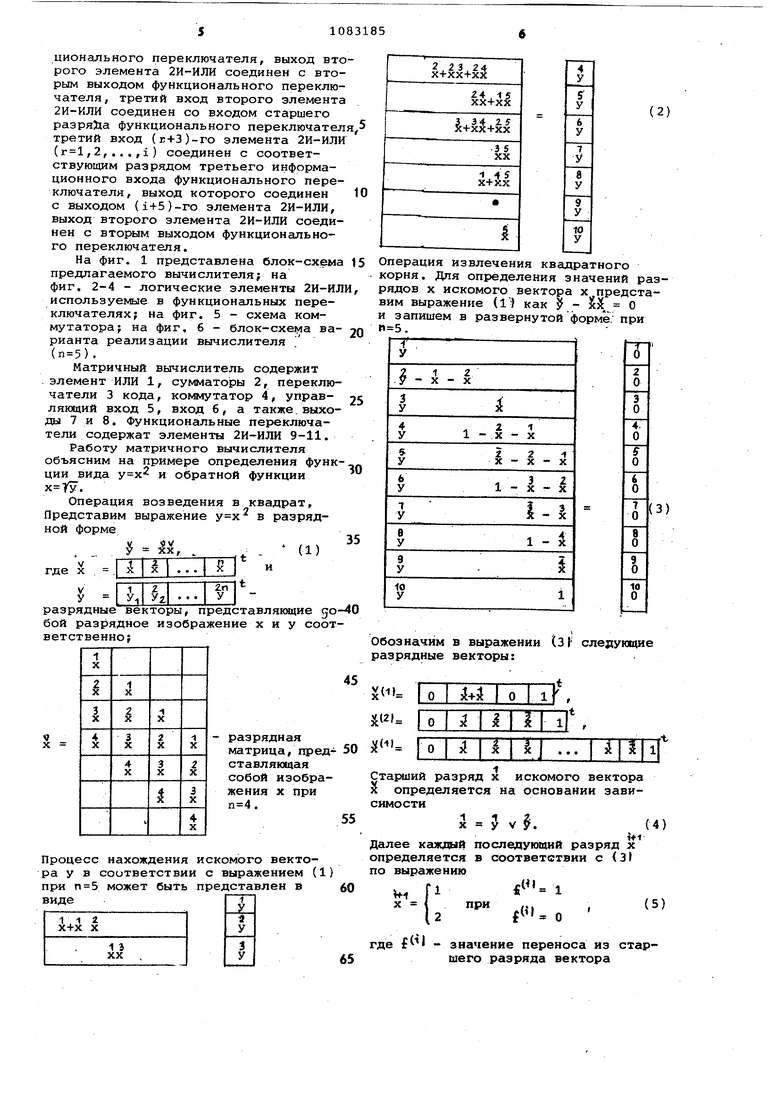

Обозначим в выражении (З Г следукхцие разрядные векторы:

V(U

(21 I О } I I ТЫ , jjHU

Старший разряд х искомого вектора }( определяется на основании зависимости

У V§.

(4)

последующий разряд х в соответствии с (31

«(« 1

(5)

ри

f(i.

где - значение переноса из старшего разряда вектора I определяемого на основании выражения (( ; ( величина, принимающая значени (1-Я 1 при ,. .,( fl--t О когда ,Jf(, Wl 4 и Вычислитель.работает следующим образом. Режим возведения в квадрат. На управляющий вход 5 подается нулевой сигнал, благодаря чему логические элементы всех функциональных перекл чателей настраиваются на реализацию зависимости (2), а выходы переноса второго и первого разрядов первого и второго сумматоров 2 соединяются через второйи третий входы коммута тора 4 с входом переноса первого разряда первого сумматора 2. При,,по даче на вход ь, т.е. на разрядь 6-6 соответственно значений х - х вектора 51 в вычитателе протекает пере ходной процесс. После окончания пер ходного процесса с первого и второго выходов первого преобразователя кода поступают векторы которые суммируются в первом сумматоре 2. Результат сумлшрования пост пает на первый вход второго сумматора 2, на второй вход КОТОРОГО КОТОРОГО gc IVV 1 VV y-i-vv I ступает вектор 1 Л.Л. I Л.Л. I л. I Формируемый во втором функциональном переключателе 3. В третьем сумматоре к полученному результату добавляется вектор 2-формируемый на выходе третьего функционального переключателя, и в последнем сумматоре 2 к полученному значению добавляется вектор поступающий с выхода четвертого функционального переключателя 3, благодаря чему на выходах г и 8, т.е. на разрядах 7 - 7. и 8г - образуются по выражению (2) искомые значения у - V вектора у. Режим извлечения квадратного корня. На управляющий вход 5 вычислителя подается единичный сигнал, поступающий на первые входы функциональных переключателей 3, при этом выход переноса второго разрядапервого сумматора 2 соединяется через второй информационный вход и выход ког1мутатора 4 с входом переноса первого разряда этого же сумматора 2, После;.подачи на вход б, т..е. на разряды б - 6 соответственно значений - у вектора 5 и после окончания переходного процесса в схеме на выходе элемента ИЛИ 1,, и соответственно первом разряде 7 выхода 7 по выражению (4 1 образуется.первый разряд X искомого вектора з. Далее в первом, втором, третьем и четвертом функциональных переключателях 3 формируются, разрядные векторы . соответственно, а в , первом, втором, третьем и четвертом сумматорах 2 реализуется соответственно первое, второе, третье и четвертое выражения (6J, благодаря чему на выходах переносов стаЕяаих разрядов соответственно первого, второго, третьего и четвертого сумматоров 2 образуются по выражению (51 значения х, х, х, и х искомого вектора Ji.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для извлечения квадратного корня | 1978 |

|

SU773617A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для извлечения квадратного корня | 1979 |

|

SU857981A1 |

| G, Q6 F 7/552, 1981 (прототип). | |||

Авторы

Даты

1984-03-30—Публикация

1982-04-19—Подача