(S) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ КОРНЕЙ КВАДРАТНОГО УРАВНЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления зависимости @ = @ + @ + @ | 1981 |

|

SU1019446A1 |

| Устройство для вычисления суммы квадратов К @ -разрядных чисел | 1981 |

|

SU993256A1 |

| Устройство для извлечения квадратного корня | 1981 |

|

SU1015378A1 |

| Устройство для вычисления скалярного произведения двух векторов | 1981 |

|

SU955088A1 |

| Множительно-делительное устройство | 1980 |

|

SU920712A1 |

| Устройство для решения системлиНЕйНыХ АлгЕбРАичЕСКиХ уРАВНЕНий | 1978 |

|

SU805336A1 |

| Матричный вычислитель функции @ | 1984 |

|

SU1216779A1 |

| Устройство для вычисления элементарных функций | 1981 |

|

SU999046A1 |

| Матричный вычислитель экспоненты | 1981 |

|

SU1024911A1 |

| Устройство для возведения п-разрядных чисел в квадрат | 1979 |

|

SU911520A1 |

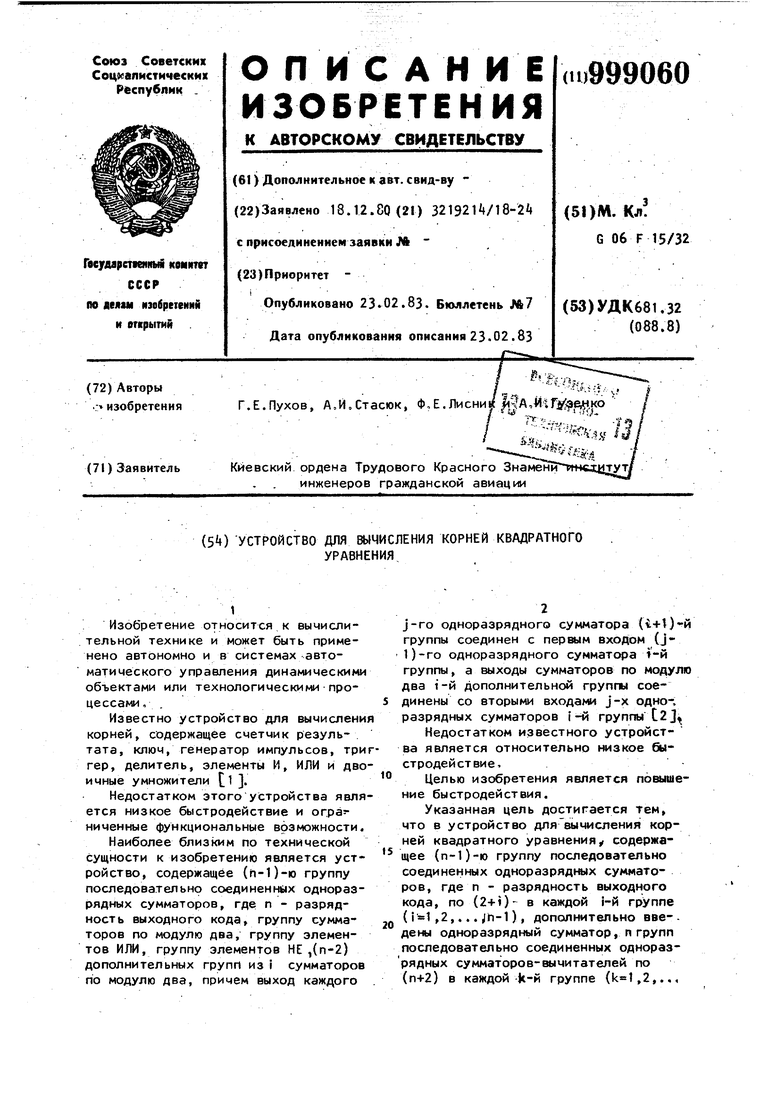

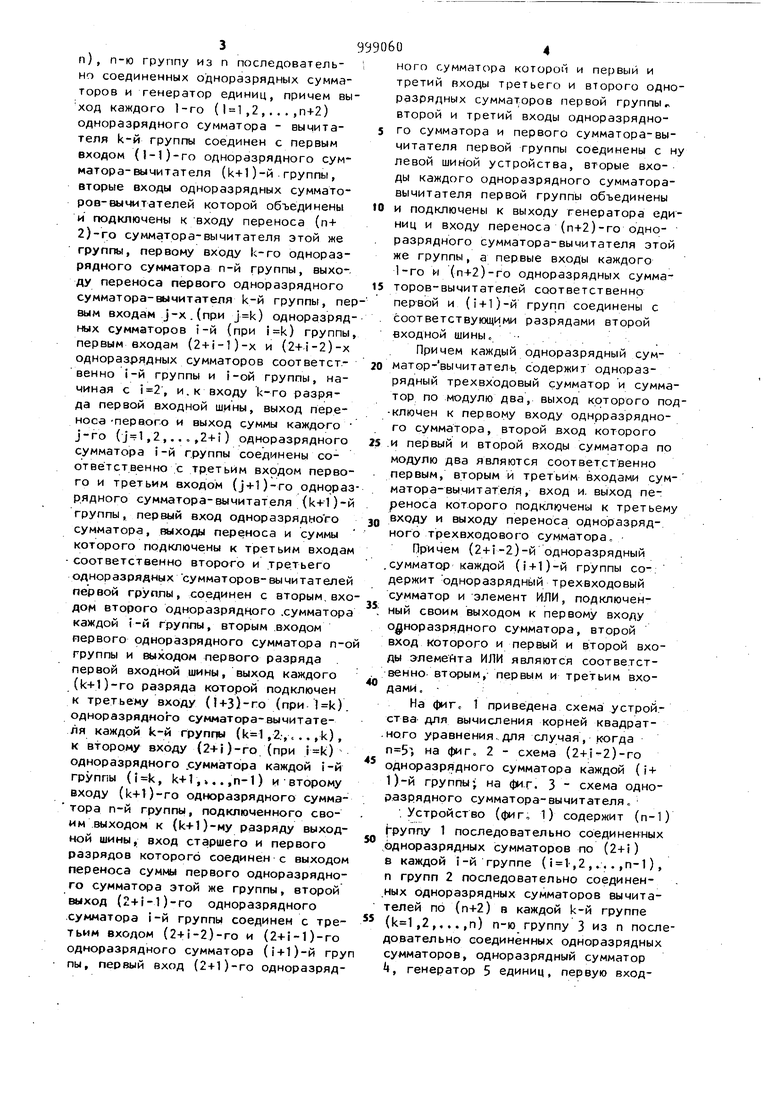

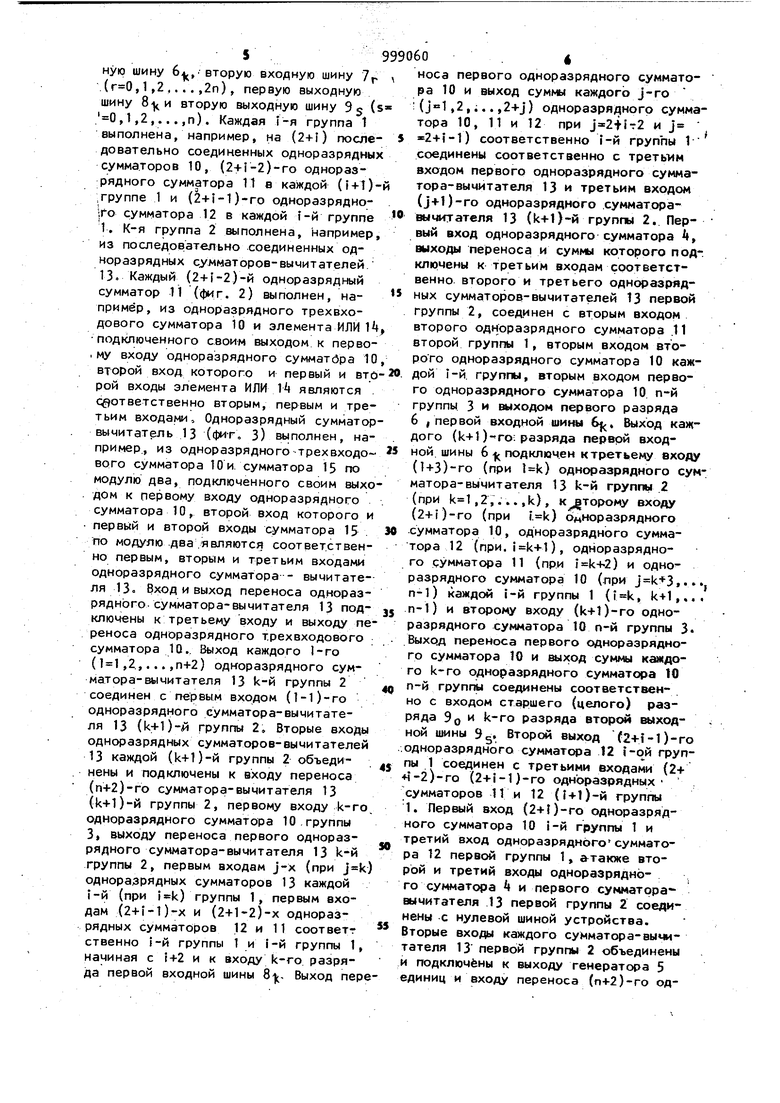

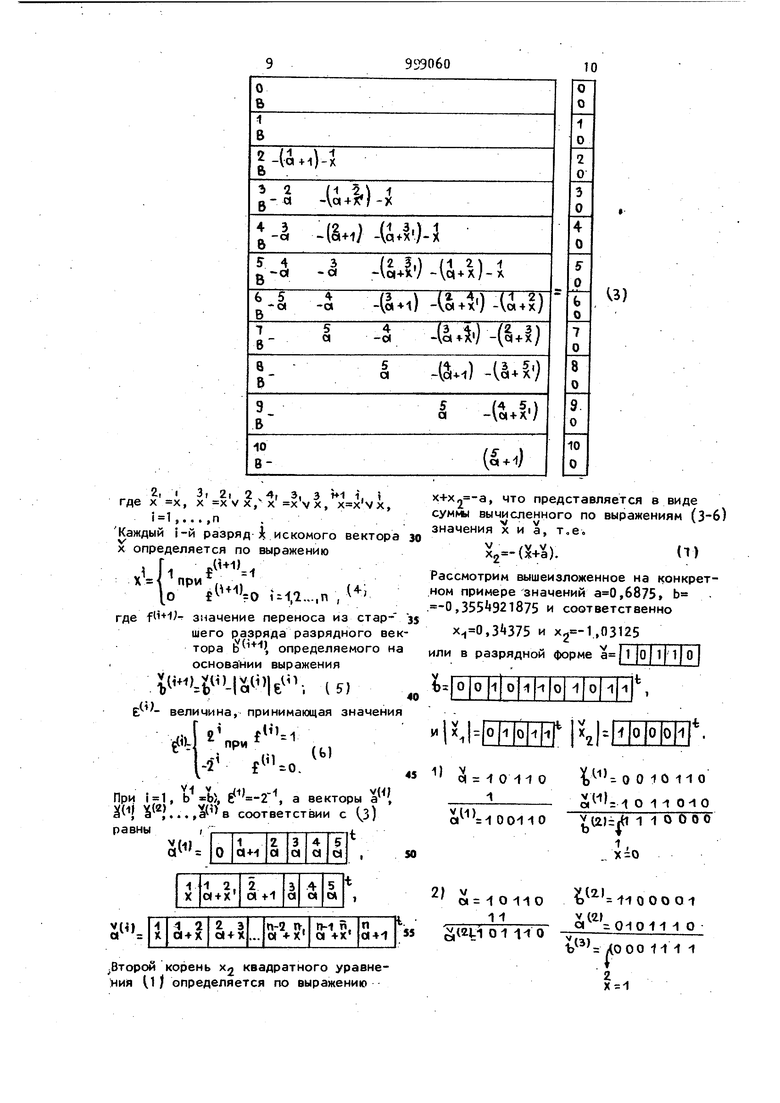

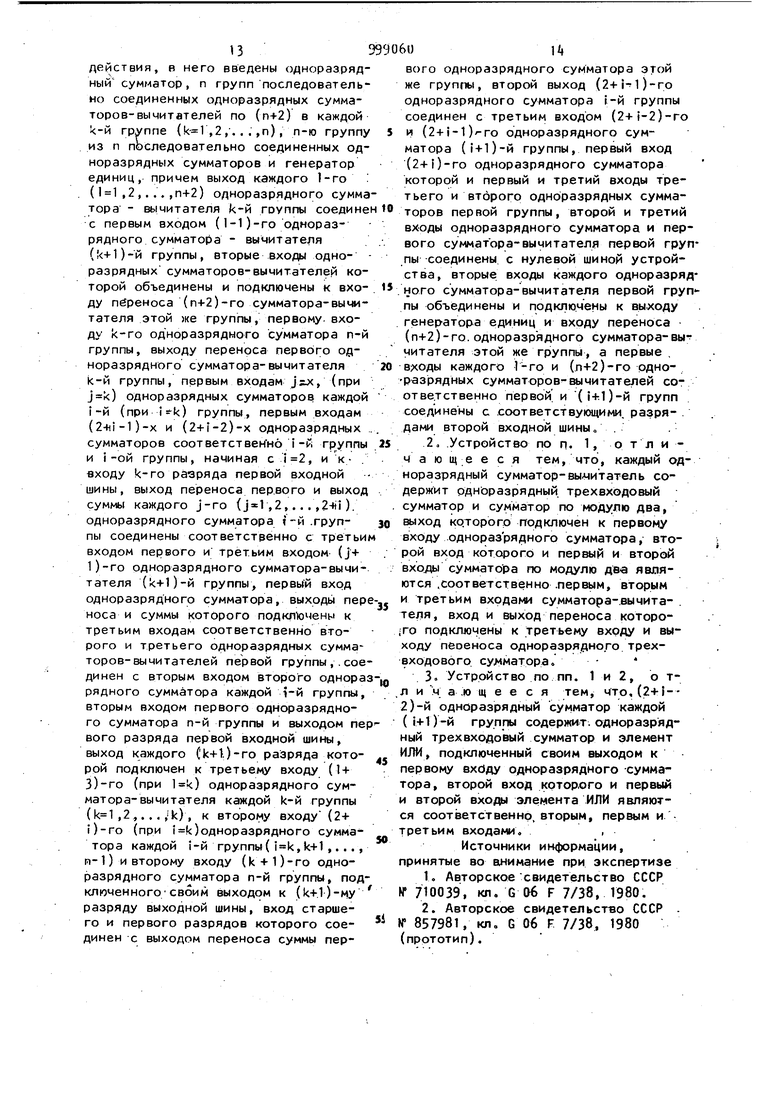

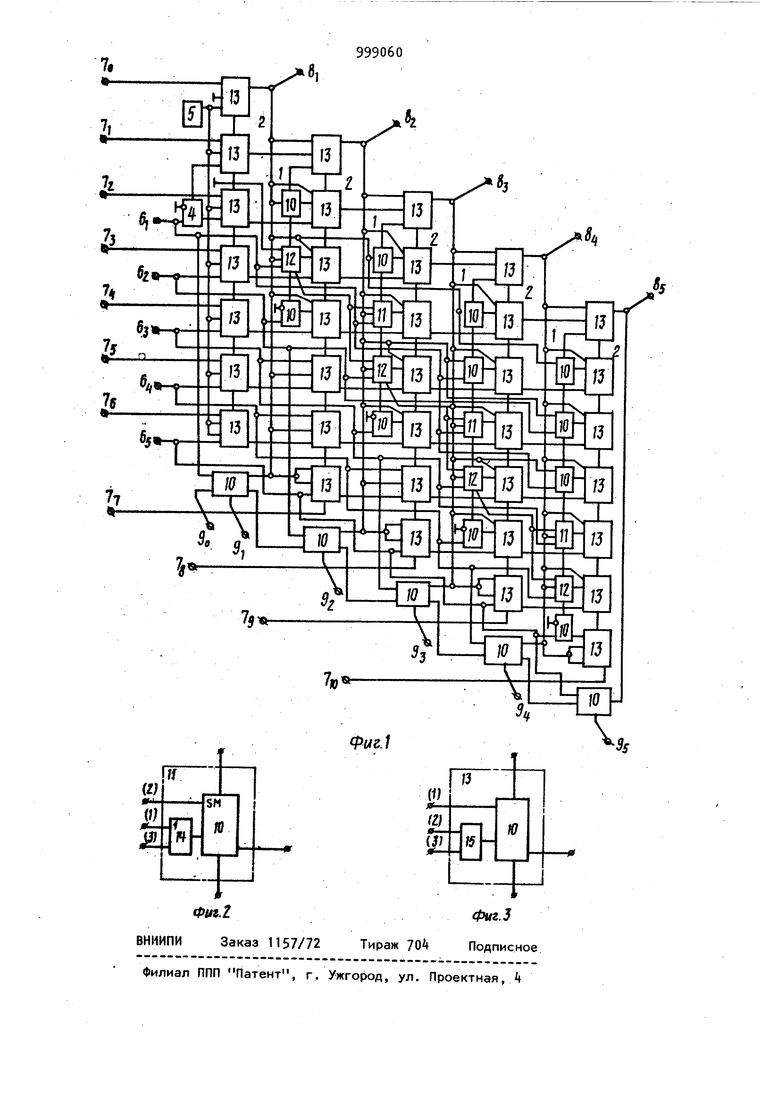

Изобретение относится,к вычислительной технике и может быть применено автономно ив системах автоматического управления динами чески объектами или технологическими процессами , Известно устройство для вычислени корней, содержащее счетчик результата, ключ, генератор импульсов, три гер, делитель, элементы И, ИЛИ и дво ичные умножители С Недостатком этого устройства явля ется низкое быстродействие и огра:ниченные функциональные возможности. Наиболее близким по технической сущности к изобретению является устройство, содержащее (п-1)-ю группу последовательно соединенных одноразрядных сумматоров, где п - разрядность выходного кода, группу сумматоров по модулю два, группу элементов ИЛИ, группу элементов НЕ ,(п-2) дополнительных групп из i сумматоров по модулю два, причем выход каждого j-ro одноразрядного сумматора ( группы соединен с первым входом (j1)-го одноразрядного сумматора t-й группы, а выходы сумматоров по модулю два i-й дополнительной группы соединены со вторыми входами j-x одно-, разрядных сумматоров i-и группы С2J Недостатком известного устройства является относительно низкое быстродействие. Целью изобретения является повышение быстродействия. Указанная цель достигается тем, что в устройство для вычисления корней квадратного уравнения ,г содержащее (п-1)-ю группу последовательно соединенных одноразрядных сумматоров, где п - разрядность выходного кода, по (2+i) в каждой i-й группе (,2,...jh-1), дополнительно вве-дены одноразрядный сумматор, пгрупп последовательно соединенных одноразрядных сумматоров-вычитателей по (п+2) в каждой k-й группе (,2,.., n), n-ю группу из n последовательно соединенных одноразрядных сумматоров и генератор единиц, причем выход каждого 1-го (,2,.,,,п+2) одноразрядного сумматора - вычитателя k-й группы соединен с первым входом {}-1)-го одноразрядного сумматора- вычитателя (k+1)-й группы, вторые входы одноразрядных сумматоров- вычитателей которой объединены и подключены к входу переноса (п+ 2)-го сумматрра-вычитателя этой же группы, первому входу k-го одноразрядного сумматора п-й группы, выходу переноса первого одноразрядного сумматора-вычитателя k-й группы, пер вым входам J-X . (при ) одноразрядных сумматоров i-й (при ) группы, первым входам (2+i-l)-x и (2+i-2)-x одноразрядных сумматоров соответственно i-й группы и i-ой группы, начиная с , и.к входу k-ro разряда первой входной шины, выход переноса-первого и выход суммы каждого JTO (,2 ,.. . ,2+i) одноразрядного сумматора i-й группы соединены соответственно .с третьим входом первого и третьим входом (j+l)-ro однораз рядного сумматора-вычитателя (k41)-й группы, первый вход одноразрядного сумматора, выходы переноса и суммы которого подключены к третьим входам - соответственно второго и третьего одноразрядных сумматоров-вычитателей первой группы, соединен с вторым,вхо дом второго одноразрядного .сумматора каждой Г-й группы, вторым входом первого одноразрядного сумматора п-о группы и выходом первого разряда первой входной шины, выход каждого (k+1)-го разряда которой подключен к третьему входу (+3)-го (при ). одноразрядного сумматора-вычитателя каждой k-й груп™ ( ,2.-,. .. ,k) , к второму входу ()-го. (при ) одноразрядного .сумматора каждой i-й группы (, k-H,..,n-l) и второму входу (k-bT)-ro одноразрядного сумма тора п-й группы, подключенного своим выходом к (k+l)-My разряду выходной шины, вход старшего и первого разрядов которого соединен-с выходом переноса суммы первого одноразрядного сумматора этой же группы, второй выход (2+i-l)-ro одноразрядного сумматора i-й группы соединен с третьим входом ()-ro и (24-|-1)-го одноразрядного сумматора (1+1)-й гру пы, первый вход (2+1)-го одноразряд904 Horn сумматора которой и первый и третий входы третьего и второго одноразрядных сумматоров первой группы,, второй и третий входы одноразрядного сумматора и первого сумматора-вычитателя первой группы соединены с ну левой шиной устройства, вторые входы каждого одноразрядного сумматоравычитателя первой группы объединены и подключены к выходу генератора единиц и входу переноса (п+2)-го одноразрядного сумматора-вычитателя этой же группы, а первые входы каждого 1-го и (п+2)-го одноразрядных сумматоров- вы читателей соответственно пер-вой и ( + 1)-й групп соединены с соответствующими разрядами второй входной шины с Причем каждый одноразрядный сумматор-вычитатель. содержит одноразрядный трехвходовый сумматор и сумматор по модулю два, выход которого подключен к первому входу однрразрядного сумматора, второй вход которого и первый и второй входы сумматора по модулю два являются соответственно первым, вторым и третьим входами сумматора-вычитат;еля, вход и. выход переноса которого подключены к третьему входу и выходу переноса одноразрядного трех входо во го сумматора. Причем (2+1-2)-й одноразрядный сумматор каждой (1+1)-и группы со-, держит одноразряднь1й трехвходовый сумматор и элемент ИЛИ, подключенный своим выходом к первому входу одноразрядного сумматора, второй вход которого и первый и второй входы элеме1Нта ИЛИ являются соответственно вторым,- первым и третьим входами , На фиг, 1 приведена схема устрой.ства для вычисления корней квадратного уравнения, для случая , .когда , на фиГо 2 - схема (2+1-2)-го одноразрядного сумматора каждой (1+ 1)-й группы; на фи.г. 3 схема одноразрядного сумматора-вычитателя. .Устройство (фиго 1) содержит (п-1) (руппу 1 последовательно соединенных одноразрядных сумматоров по (2+1) в каждой i-й группе (,2,...,п-1), n групп 2 последовательно соединенных одноразрядных сумматоров вычитателей по (п+2) в каждой k-й группе (,2,,..,п) п-ю группу 3 из n последовательно соединенных одноразрядных сумматоров, одноразрядный сумматор , генератор 5 единиц, первую входную шину 6, вторую входную шину 7г .(,1,2,...,2п), первую выходную шину 8 и вторую выходную шину 95 (s ,1,2,...,п). Каждая Г-я группа 1 выполнена, например, на (2+i) последовательно соединенных одноразрядных сумматоров 10, ()-го одноразрядного сумматора 11 в каждой (|+Т);группе 1 и (2+i-1)-ro одноразрядно fo сумматора 12 в каждой f-й группе 1. К-я группа 2 выполнена, например, из последовательно соединенных одноразрядных сумматоров-вычитателей 13. Каждый (2+1-2)-й одноразрядный сумматор 11 (фиг. 2) выполнен, например, из одноразрядного трехвходового сумматора 10 и элемента ИЛИ 1 подключенного своим выходом.к парво.му входу одноразрядного сумматбра 10 второй вход которого и первый и втб рой входы элемента ИЛИ 1А являются . соответственно вторым, первым и третьим входами. Одноразрядный сумматор вычитатель 13 (фиг. 3) вь1полнен, например, из одноразрядногоТрехаходового сумматора 10 и сумматора 15 по модулю два, подключенного своим выхо дом к первому входу одноразрядного . сумматора 10, второй вход которого и первый и второй входы сумматора 15 по модулю два .являются соответственно первым, вторым и третьим входами одноразрядного сумматора - вычитателя 13. Вход и выход переноса одноразрядного сумматора-т 1читателя 13 подключены к третьему входу и выходу переноса одноразрядного трехвходового сумматора 10.. Выход каждого 1-го (1 1 ,2.,... ,п+2) одноразрядного сумматора-вычитателя 13 k-й группы 2 соединен с первым входом (1 -1)- го одноразрядного сумматора-вычитателя 13 (k+l)-fl группы 2, Вторые входы одноразрядных сумматоров-вычитателей 13 каждой (К+1)-й группы 2 объединены и подключены к входу переноса (п+2)-го сумматора-вычитателя 13 (и+1)-й группы 2, первому входу k-го одноразрядного сумматора 10.группы 3 выходу переноса первого одноразрядного сумматора-вычитателя 13 k-й группы 2, первым входам j-x (при ) одноразрядных сумматоров 13 каждой |-й (при ) группы 1, первым входам (2+1-1)-х и (2+1-2)-х одноразрядных сумматоров 12 и 11 соответг ственно i-й группы 1 и i-й группы 1, начиная с i+2 и к входу k-ro разряда первой входной шины S-j-, Выход пере носа первого одноразрядного сумматора 10 и выход суммы каждого J-го (j 1,2,;..,2+j) одноразрядного сумматора 10, 11 и 12 при j 2tiT2 и j , 2-fi-1) соответственно i-й группы 1 соединены соответственно с треть 1м входом первого одноразрядного сумматор а -вы читателя 13 и третьим входом (j+l)-ro одноразрядного .сумматоравычитатеяя 13 (k-ft)-и группы 2. Пер- вый вход одноразрядного сумматора 4, выходы переноса и суммы которого подключены к третьим входам соответственно второго и третьего одноразрядных сумматоров-вычитателей 13 первой группы 2, соединен с вторым входом второго одноразрядного сумматора .11 второй группы 1, вторым входом второго одноразрядного сумматора 10 каждой 1-й. группы, вторым входом первого одноразрядного сумматора 10 п-й группы 3 и выходом первого разряда 6 , первой входной шины 6, Выход каждого (k+1)-го: разряда первой входной шины 6 подключен ктретьему входу (+3)-го (при ) одноразрядного сумматора- вычитателя 13 k-й группы .2 (при ,2,... ,k), которому входу (2+Г)-го (при i.k) бмноразрядного .сумматора 10, одноразрядного сумматора 12 (при, ), одноразрядного сумматора 11 (при ) и одноразрядного сумматора 10 (лри j k-3f..., n-l) каждой i-й группы 1 (, k+1,.,. n-1) и второму входу (k+t)-ro одноразрядного сумматора 10 п-й группы 3« Выход переноса первого одноразрядного сумматора 10 и выход суммы какдого k-ro одноразрядного сумматора 10 п-й групгл соединены соответственно с входом старшего (целого) разряда 9о и k-ro разряда второй выходной шины 9д. Второй выход f2+i-l)-ro одноразрядного сумматора 12 С-ой группы 1 соединен с третьими входами (2+ и-2)-го (2+i-lJ-ro одноразрядных сумматоров 11 и 12 (}+1)-й группы 1. Первый вход (2+1)-го одноразрядного сумматора 10 I-и группы 1 и третий вход одноразрядногосумматора 12 первой группы 1, атакже второй и третий входы одноразрядного сумматсч а 4 и первого сумматрравычитателя 13 первой группы 2 соединены с нулевой шиной устройства. Вторые входы каждого сумматора-вычитателя 13 первой группы 2 объединены и подключены к выходу генератора 5 единиц и входу переноса (п+2)-го одноразрядного сумматора-вычитателя 13 этой же группы Первые входы каждого 1-го и (п+2)-го одноразрядных сумматоров-вычитателей 13 соответственно первой и )-й групп соединены с выходами соответствующих разрядов 7oi 7,0,, ,,... ,72пвторой входной шины 7f-. Первые входы (2-ь)-го одноразрядного сумматора 10 -й группы 1 и второй вход одноразрядного сумматора выполнены в виде инверсных Работу предлагаемого устройства для вычисления корней квадратного . уравнения X +ах+Ь 0 при а о, Ь О , представленного в разрядной форме в виде b-()6, поясним на конкретном примере,

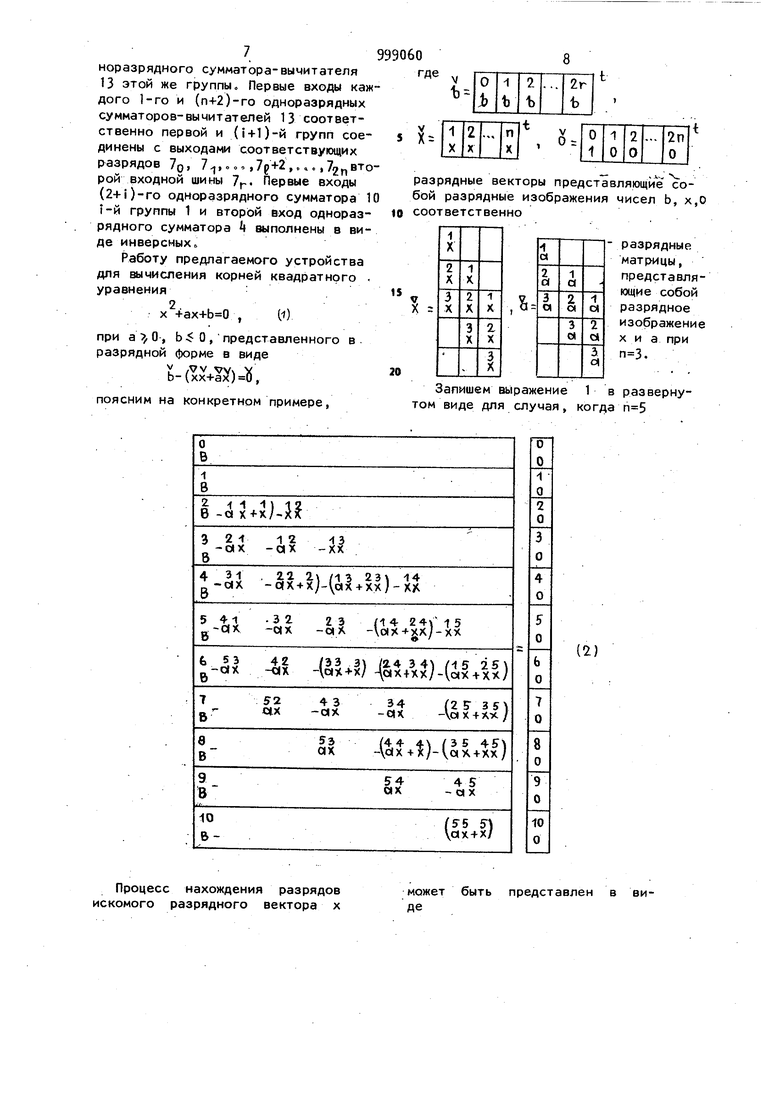

Процесс нахождения разрядов искомого разрядного вектора х 999060 где раз бой to соо том

может быть представлен в видеядные векторы представляющие соразрядные изображения чисел Ь, х,0 ветственно - разрядные матрицы, представляющие собой разрядное изображение X и а при . апишем выражение 1 в развернувиде для случая, когда 2, I 3, 2, 2 ,4, 3, 3 t+1 i, где X x, X xvx,x xvx, , i 1,,.. ,n.. Каждый i-й разряд искомого вектора X определяется по выражению 1„...1 . ;.-«о п Нл -о iM,7....n , где fH+lP-r змачение переноса из старшего разряда разрядного век тора , определяемого на основании выражения ;iUH, () величина, принимающая значения Ц при .0.

При i 1, , -2, а векторы а( ...Д(в соответствии с U)

SdJ.

S

.Второй корень Х2 квадратного уравнения 1) определяется по выражению

so

1100001

)

« 10110 V Ш

11

q -010111 о (гп 01 11 о

ХООО 1111

f

, что представляется в виде суммы вычисленного по выражениям (3-6) значения х и а, т.е. )- Рассмотрим вышеизложенное на конкретном примерезначений ,6875 Ь -0,355 921875 и соответственно , и ,03125 1 I nlxj. у (3) fy-.. - (х Ъ Я 10-11 о 1 01 1010110 101010 ,l4)-(i F 1 01 0 0 4) V d 10110 1101001 0 0 1 1 0 0 OO (.i 10000 5ЬдО 011001 011 0011 01 10 110 10101 1010101 1011 7 )- ко 00 1 000 в соответствии с (8/полуЗнамение х, чим а Z 1 011 о X-J-0 1011 (У 1,0 0001 Устройство для вычисления корней квадратного уравнения работает следу ющим образом. При подаче на первук) входную шину 6 значения разрядов а а,..,,а век тора и на вторую входную шину 7р .соответственно разрядов Ь,, Ь, ...,Ь вектора b и после око;нчания переходного процесса в схеме на выходах одноразрядных сумматоров-вычитателей 13 первой группы 2 в соответствии с ( 5) образуется значение вектора-Ь, поступающее на первые входы одноразрядных сумматоров-вычит.ателей 13 вто рой группы 2. На выходе переноса

первого одноразрядного сумматора-вычитателя 13 первой группы 2 по выражению (k) и соответственно первом разряде 8 первой выходной шины 8-|, образуется ст-аршйй разряд х искомого вектора . В результате суммы в одноразрядных сумматорах-вычитатевторой группы 2 значении веклях 1

(01V(9)

и вектора а,,поступающего тора

из одноразрядных сумматоров 10, 11 и 12 первой группы; 1 , образуется вектор b , а на выходе второго разФормула изобретения

Авторы

Даты

1983-02-23—Публикация

1980-12-18—Подача