1

Изобретение относится к вычислительной технике и может быть использовано автономно или в качестве специализированного процессора в составе многопроцессорньпс вычислительных систем, предназначеных для реализации вычислительного процесса в натуральном масштабе вр мени.

Цель изобретения - сокращение затрат оборудования.

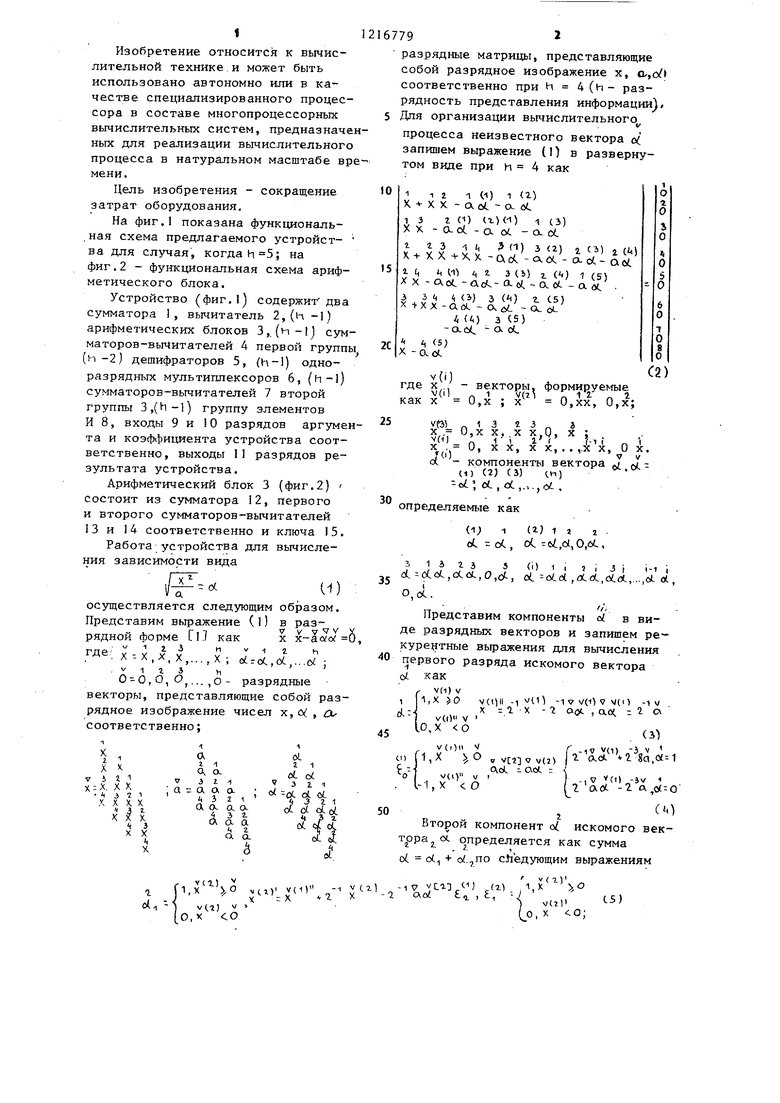

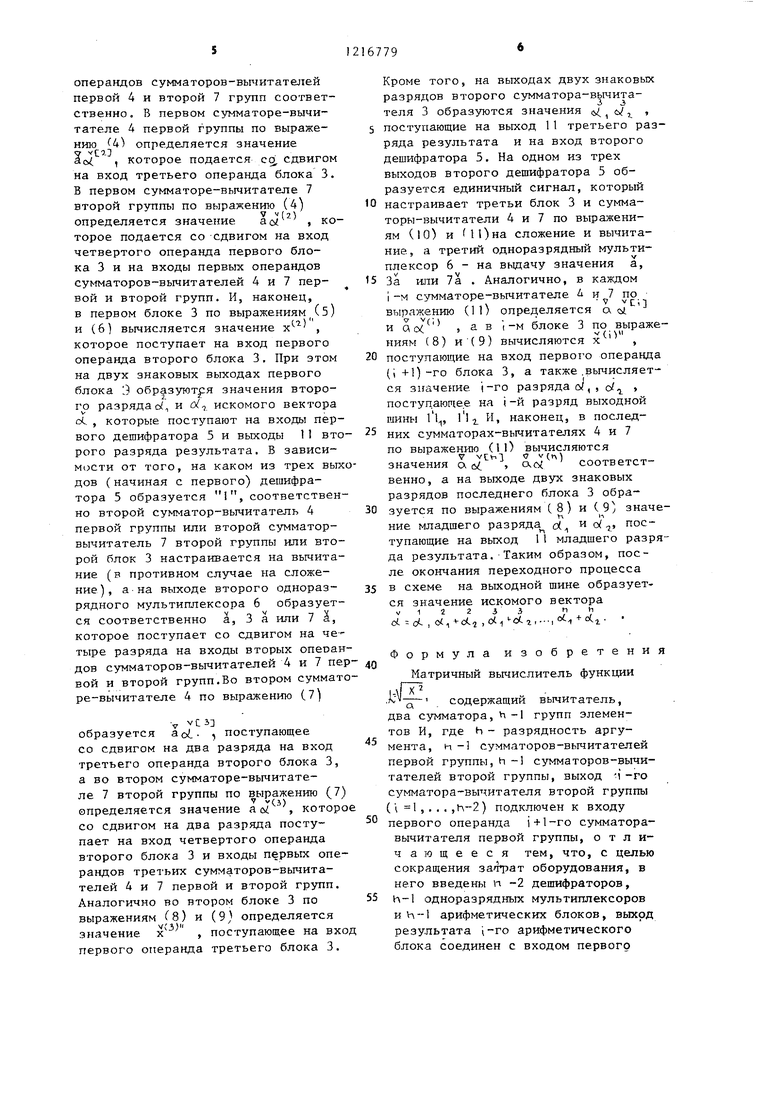

На фиг,1 показана функциональная схема предлагаемого устройст- ва для случая, когда на фиг.2 - функциональная схема арифметического блока.

Устройство (фиг,1) содержит два сумматора , вычитатель 2,(h -) арифметических блоков 3, (и-1J сум маторов-вычитателей 4 первой групп (и -2) дешифраторов 5, (h-1) одноразрядных мультиплексоров 6, (h-l) сумматоров-вычитателей 7 второй группы 3,{h-l) группу элементов И 8, входы 9 и 10 разрядов аргумета и коэф11)ициента устройства соответственно, выходы 1) разрядов результата устройства.

Арифметический блок 3 (фиг.2) состоит из сумматора 12, первого и второго сумматоров-вычитателей 13 и 14 соответственно и ключа 15.

Работа устройства для вычисления зависимости вида

- d.

и)

осуществляется следующим образом. Представим выражение (1) в разрядной форме Г 1.7 как х „.,„, V 1 i 3 и V 1 г h .Де. Х--Х,х,х,...,Х ; o(.oC,ot,...o; ; . г h 00,O,Oj...O- разрядные

векторы, представляющие собой разрядное изображение чисел х, сХ , гЭ соответственно;

i,rS.o

v(2l

0,Х О

V Сг) Ч

V(1) X

разрядные матрицы, представляющие собой разрядное изображение х, o,o(t соответственно при h 4 (h - разрядность представления информации), Для организации вычислительного

процесса неизвестного вектора о( запишем выражение (1) в развернутом виде при и 4 как

1 -12 1 (-1) 1 г) K-V-XK -ао.

13 г (1) tT.(-i) 1 (3) Xx-ad.-aoc-ac

г г 3 t, Д П) 3 (2) 1 сг) , м

K+KX+xx-aoi.-c x-cxo(.-aut

It, LI () г, г 3 (i) г С-) 1 (.5) X X - act.-ud.-ac, - (X ot - а at . 3 3 (, (i) 3 (ii) г. C5) X i-xx -ас. - о.й/. -OL oL

« (A) 3 (S) -OLut, - a oL

t s)

X -0.01,

v(ij X

V(l) ., 1

X 0,x ;

С2)

- векторы, формируе 1ые

У1:ч

v(n

1 2.7

О,XX, 0,х;

Vf31 ,. 1 3 г 33

х, О.х X. X х,0, X :

v(ij Д 1 i l г .1 t X , О, X X, X X, . . ,.х X, О

i.

V V

компоненты вектора л/ лС- (,, (2) СЗ) и)

-ei , 0(. , 0(. ,..,(-,

30

определяемые как (i; -1

оС t:oC,

(г) 1 2 1 оС гь(,,о1,0,бС,

13 г 3

1 I

3 i

1-1 I

d-ctat.,(Xo/.,0,o(., ,ci.d.,oi,cii,...,ci di,

0,oC.

//

Представим компоненты d. в виде разрядных векторов и запишем ре- курентные выражения для вычисления первого разряда искомого вектора

50,

Второй компонент о искомого век- . определяется как сумма Ы о( + Ы.по с тедующим выражениям .гГ.

CS)

) -1 V vca: f) (г) -1 ао г . ,

.1.x

.

vCzl

о,х iO;

V (iV V i1

) у ) (1, ci-, л ОС г -

«tl). V

;о,к o

--Г 1

l-i,ot

совместно с 1

ICXfiL -2(

v(a -/, v i , I : -. bt,

wvr-t--v -- - н:г-: - ч-- -:

Г э v(i -1,4 i- г CKcl, -1 cx,

aoL -t-i 7a , (--u(

И,наконец, каждый последующий к омпонент о( определяется как сумма

9 V(2) ... laoL +г 7а, Ы,Ы ::1.

II I

- оС 1 - d- х следующим выра ям

-

- V I

1,X O

VtO

O, i 0

..,,.c;-.,.,-,,v,n c,,)

1. X

cip

.o

vcl)n O, X 0

(i V V (ill -(i- 1) 7 wci ) , i I X - X - 2 a o(. -,

(1, ci-, л ОС г -

--Г 1

l-i,ot

I : -. bt,

н:г-: - ч-Г э v(i -1,4 i- г CKcl, -1 cx,

н:г-: - ч-9 V(2) ... laoL +г 7а, Ы,Ы ::1.

II I

- оС 1 - d- х следующим выражениям

C8)

C9)

vci ), 1, X 0 r,;

V,.., . г - 0, X 0

(10)

совместно с выражениями

-V v/ti) -(иг) V i act -1 o t оСл-с г-

V v(Ui) Iv Cl) -Ci + Z) V i i

ad. --S - 1 5СЧ, dL,1, , wt O -CUi) V i LO Cl. -l TO.,

Параллельный процессор функционирует следующим образом. В исходном состоянии на первый устрой- ства, разряды с первого 9 noh-й 9, подаются соответственно значения разрядов с первого х по и-и х известного вектора х, а на вторую входную шину 10 подается значение а, и в схеме устройства протекает переходной процесс. После окончания переходного процесса в схеме, на выходах каждой i-и группы элементов И 8 (| 1 ,. . ., h -1) по выражению (, 2) образуется j-и вектор х , который подается со сдвигом на разрядов в сторону младших разрядов, на вход второго оп еранда -го арифметического блока 3. На выходе первого сумматора 1 образуется значение За , которое подается на вторые информационные входы всех одноразрядных мультиплексоров 6, на выходе второг;о сумматора 1 образуя значение 7 а, которое подается на третьи информационные входы

- ч veil )v j

acL +2 a, ct, :c(.-o

q /C;i -(i+l) O, 6L 1

iv t O -(U2)

lo cL +1

Ъл,,о;г-0 Та, (.г-1 .(-fl

одноразрядных мультиплексоров 6, начиная со второго, а на первые входы всех одноразрядных мультиплексоров 6 подается значение а . В вьгчитателе 2 по выражению (3)

2

V(1)

реализуется вычисление х

т ч vfll

i а ы. которое поступает на вход

v,(.1

А

5

первого операнда первого арифметического блока 3. На выходе знакового разряда вычитателя 2 образуется значение й. , которое подается на первый разряд выхода 11 и на вход управления сложением-вычитанием первого блока 3 первого четы- рехвходового сумматора-вычитате- . ля 3 и первых сумматоров-вычитате0 лей 4 и 7 первой и второй групп и управляющий вход первого одноразрядного мультиплексора 6, Если о(. 1 , то блок 3 и первые суммато- ры-вьгаитатели 4 и 7 настраиваются

5 на вычитание, когда о( О - на

сложение. Кроме того, при 01 1 зна„V

чение 3 а подается из выхода первого переключателя 6 на входы вторых

V v(2

ao; , Koоперандов сумматоров-вычитателей первой 4 и второй 7 групп соответственно. В первом сумматоре-вычи- тателе 4 первой группы по выражению ) определяется значение

7- СгЗ

Зс , которое подается со, сдвигом

на вход третьего операнда блока 3.

8первом сумматоре-вычитателе 7 второй группы по выражению (4) определяется значение

торое подается со сдвигом на вход четвертого операнда первого блока 3 и на входы первых операндов сумматоров-вычитателей 4 и 7 первой и второй групп. И, наконец, в первом блоке 3 по выражениям(5) и (6) вычисляется значение , которое поступает на вход первого операнда второго блока 3, При этом на двух знаковых выходах первого блока 3 образуются значения второ- г разряда 0 и oi искомого вектора сС, которые поступают на входы первого дешифратора 5 и выходы 1t второго разряда результата. В зависимости от того, на каком из трех выхдов (начиная с первого) дешифратора 5 образуется 1, соответственно второй сумматор-вьгчитатель 4 первой группы или второй сумматор- вычитатель 7 второй группы или второй блок 3 настраивается на вычитание (в противном случае на сложение), а-на выходе второго одноразрядного мультиплексора 6 образуется соответственно а, 3 а или 7 , которое поступает со сдвигом на четыре разряда на входы вторых опеоан дов сумматоров-вычитателей 4 и 7 певой и второй групп.Во втором сумматре-вычитателе 4 по выражению (7)

-V СЬ образуется ас. , поступающее

со сдвигом на два разряда на вход третьего операнда второго блока 3, а во втором сумматоре-вычитателе 7 второй группы по выражению (7)

Сз) определяется значение а oi , которо

со сдвигом на два разряда поступает на вход четвертого операнда второго блока 3 и входы первых операндов третьих сумматоров-вычитателей 4 и 7 первой и второй групп. Аналогично во втором блоке 3 по выражениям f8) и (9) определяется значение , поступающее на вхо первого операнда третьего блока 3.

Кроме того, на выходах двух знаковых разрядов второго сумматора-вычита- теля 3 образуются значения i uj , поступающие на выход 11 третьего разряда результата и на вход второго дешифратора 5. На одном из трех выходов второго дешифратора 5 образуется единичный сигнал, который

настраивает третьи блок 3 и сумма- торы-вычитатели 4 и 7 по выражениям (Ю) и И Она сложение и вычитание, а третий одноразрядный мультиплексор 6 - на вьщачу значения а,

За или 7а . Аналогично, в каждом 1-м сумматоре-вычитателе 4 и 7 по выражению (11) определяется а ы и Qo( а в |-м блоке 3 по выражениям (8) и (9) вычисляются х ,

поступающие на вход первого операнда (i +1)-го блока 3, а также.вычисляется значение (-го разряда о/,, Ы постуцающее на i-и разряд выходной шины I l, I l. И, наконец, в последних сумматорах-вычитателях 4 и 7 по выражению (П) вычисляются

V vtbl С v(n

значения о, ( , o(Si соответственно, а на выходе двух знаковых разрядов последнего блока 3 образуется по выражениям (8) и (9) значение младшего разряда о( и at,, поступающие на выход 11 младшего разряда результата.Таким образом, после окончания переходного процесса

в схеме на выходной шине образуется значение искомого вектора

V 1 2 2 3 3 пи

ci. : ot-, оС, ,,---,

ормула изобретения

Матричный вьиислитель функции Т

содержащий вычитатель,

два сумматора, i -1 групп элементов И, где h- разрядность аргумента, и -1 сумматоров-вычитателей первой группы, h -1 сумматоров-вычитателей второй группы, выход 1 -го сумматора-вычитателя второй группы ( 1,...,h-2) подключен к входу первого операнда i+l-ro сумматора- вычитателя первой группы, о т л и- ч ающееся тем, что, с целью сокращения оборудования, в него введены п -2 дешифраторов, h-1 одноразрядных мультиплексоров и h-t арифметических блоков, выход результата ;-го арифметического блока соединен с входом первого

операнда i+1-ro арифметического блока, вход первого операнда первого арифметического блока подключен к выходу вычитателя, вход первого разряда аргумента вычислителя соединен с первыми входами элементов И групп, вход аргумента вычислителя соединен со сдвигом на один разряд в х:торону младших разрядов с входом уменьшаемого вычитателя, К.- е входы j -1 -и группы элементов H(,.,.,h; К 2,..., J) являются входами j-ых разрядов аргумента вычислителя соответственно, выходы элементов И j-1 группы подключен со сдвигом на J-1 разряд в сторону младших разрядов к входу второго операнда j -l-ro арифметического блока, выходы первого и второго знаковых разрядов которого подключены к входам j-ro дешифратора, первый выход которого подключен к первому управляющему входу j-го одноразрядного мультиплексора и к управляющему входу J-го сумматора-вычи- тателя первой группы, второй выход i-го дешифратора подключен к второму управляющему входу j-го одноразрядного мультиплексора и к управляющему входу J -го суммптора-вычи- тателя второй группы, третий .выход J-ro дешифратора подключен к третьему управляющему входу j-го одноразрядного мультиплексора и к входу управления сложением-вычитанием j-ro арифметического блока, входы третьего и четвертого операндов j-1-го арифметического блока подключены к выходам J-1-X сумматоров- вычитателей первой и второй групп соответственно, выход i-го сумма- тора-вычитателя второй группы подключен к входу первого операнда i+1-го сумматора-вычитателя второй группы, выход j-1-го одноразрядного мультиплексора подключен со сдвигом на 0+1 разряд в сторону младших разрядов к входам вторых операндов j-х сумматоров-вычита- телей первой и второй групп, выход знакового разряда вычитателя подключен к входу управления сложением-вычитанием, входу первого арифметического блока и к управляющим входам первого одноразрядного мультиплексора, первых сумма- торов-вычитателей первой и второй групп, вход первого операнда первого сумматора соединен со сдви216779°

ГСМ на один разряд в сторону старших разрядов с входом второго операнда первого сумматора, со сдвигом на два разряда в сторону старших

g разрядов - с входом первого операнда второго сумматора, со сдвигом на два разряда в сторону младших разрядов - с входом вычитаемого вычнтателя и с входами вторых рандов сумматоров-вычитателей первой и второй групп, с первыми информационными входами всех одноразрядных мультиплексоров и являете- ся входом значения коэффициента уст15 ройства, выход первого сумматора подключен к входу второго операнда второго сумматора и к вторым информа ционным входам всех одноразрядных мультиплексоров, выход второго сум2Q матора подключен к третьим информационным входам с второго по И-1-й одноразрядных мультиплексоров, выход знакового разряда вьЕчитателя является выходом первого разряда значе25 НИН результата устройства, выходы первого и второго знаковых разрядов ,j-l-ro арифметического блока является выходом о-го разряда значения результата устройства, при30

чем каждый арифметический блок

содержит сумматор, входы первого и второго операндов которого являются одноименными входами блока, первый сумматор-вычитатель, выход знакового разряда которого является выходом первого знакового разряда блока, ключ, второй сумматор- вычитатель, вход управления сложе- нием-вьмитанием которого соединен с выходом знакового разряда первого сумматора-вычитателя и управляющим входом ключа, выход которого подключен к входу первого операнда второго сумматора-вьгаитателя, выход знакового разряда и результата которого являются выходом второго знакового разряда и результата блока соответственно, вход второго операнда второго сумматора-вычитателя подключен к выходу первого сумматора-вычитателя, вход первого операнда которого подключен к выходу сумматора, вход управления сложением-вычитанием и вход второго операнда первого сумматора-вычитателя и информационный вход ключа являются входом управления сложением-вычитанием и входами третьего и четвертого операндов блока соответственно.

11:

фиг.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой функциональный преобразователь | 1989 |

|

SU1686438A1 |

| Устройство для поворота вектора | 1983 |

|

SU1132285A1 |

| Матричное вычислительное устройство | 1984 |

|

SU1233141A1 |

| Устройство для извлечения квадратного корня | 1981 |

|

SU1015378A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1315971A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Устройство для вычисления зависимости @ = @ + @ + @ | 1981 |

|

SU1019446A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1119009A1 |

| Матричный преобразователь координат | 1988 |

|

SU1559343A1 |

| Устройство для умножения с накоплением | 1986 |

|

SU1310810A1 |

| Пухов Г.Е., Евдокимов В.Ф., Синьков М.В | |||

| Разрядно-аналоговые вычислительные системы | |||

| М.: Советское радио, 1978, с.254 | |||

| Устройство для вычисления функций вида у=ах @ и у= @ | 1980 |

|

SU885998A1 |

| Стасюк А.И | |||

| Однородные многофункциональные матричные процессоры | |||

| (Препринт АН УССР | |||

| Институт электродинамики, № 351) | |||

| Киев, 1983, с.13, рис.3. | |||

Авторы

Даты

1986-03-07—Публикация

1984-06-29—Подача