(54) МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ АНАЛИЗА ЭКСТРЕМУМОВ

шается, -срабатывает вторая схема сравнений, которая формирует импульс уменьшающий на единицу содержимое реверсивного счетчика и опрокидывающий триггер знака производной в положение Отрицательная производная. Момент смены знака производной соответствует экстремуму, а его численное значение qHHMaexcH с реверсивного счетчика.

В случае построения многоканальной системы для измерения и анализа экстремумов с использованием принципов вышеописанных устройств неизбежны большие аппаратур1|ые затраты, поскольку в этом случае система реализуется параллельным включением рассматриваемых устройств 2.

Наиболее близкой к предлагаемой является система, которая содержит коммутатор, входы которого являются информационными входами систе1«ш1, аналого-цифровой преобразователь, вход которого соединен с выходом коммутатора, первое запоминающее устройство, вход которого соединен с выходом аналого-цифрового преобразователя, второе запоминающее устройство, устройство сравнения, входы которого подключены соответственно к выходам аналого-цифрового преобразователя, первого и второго запоминающих устройств, регистр, входы которрго подключены к выходам устройства сравнения, счетчик номера канала, выход которого соединен с адресньоми входами коммутатора, первого и второго запоминающих устройств, устройство управления, первый, второй и третий входы которого соединены соответственно с первым, вторым и третьим выходами регистра, второй выход регистра соединен со входом второго запоминающего устройства, выходы устройства управления соединены соответственно с управляющими входами счетчика номера канала, аналого-цифрового преобразователя, п.ервого и второго запоминающих устройств и регистра, четвертый вход устройства управления соединен с выходом генератора тактовых икшульсов.

По тактовому импульсу устройство управления подает импульс на вход счетчика номера канала,тем самым подключает следующий канал. Затем усхрбйство управления осуществляет запуск ангшого-цифрового преобразователя. Первое и второе запоминающее устройства постоянно находятся в режиме считывани я (нуль на управляющем входе), Аналого-цифровой преобраэойатель работает .таким образом, что результат преобразования сохраняется iia его выходе до следующего запуска. Дешее устройство управления подав импульс записи на управляю((ий вход регистра,тем самым записы

вает результат сравнения в регистр. На устройство сравнения поступают код текущего отсчета данного канала с выходов коммутатора кода, код предыдущего отсчета данного канала, с выходов пербого запоминающего устройства и код знака производной предыущего отсчета с выхода второго заоминающего устройства. В результате равнения возможны следующие три ситуации: значение текущего отсчета равно значению предыдущего отсчета, значение текущего и предыдущего отчетов не равны, а знак производной предыдущего отсчета совпадает со знаком прои,зводной текущего отсчета, значения текущего и предыдущего отсчетов не равны, и знаки производной текущего и предыдущего отсчетов не совпадают .

В первом случае никаких операций не производится.

Во втором случае устройство управления формирует импульс на запись текущего отсчета в первое запоминающее устройство, а знака производной текущего отсчета - во второе запоминающее устройство.

В третьем случае устройство управления формирует сигнал на внешнее устройство о наличии экстремума (считывание значения экстремума внешним устройством осуществляется -с выхода первого запоминающего устройства, номер канала считывается с выхода счетчика номера канала, а тип акстремума с выхода второго запоминающего устройства).

Далее, устройство управления формирует импульс на запись значения текущего отсчета в первое запоминающее устройство, а знака производной текущего отсчета - во второе запоминающее устройство ..

Интервалы между импульсами, вырабатываемыми устройством управления, выбираются с учетом времени установления элементов структурной схемы.

Тактовая частота выбрана из услоВИЯ максимального времени обработки экстретлума в одном канале внешними устройствами 3.

Недостатками, известной схемы являются низкая.точность определения значения экстремумов, так как частота дискретизации определяется максималь.ным временем обработки экстремума, вьгсокая вероятность потери экстремумов, особенно в случае их возникновения в близкие моменты времени в нескольких каналах.

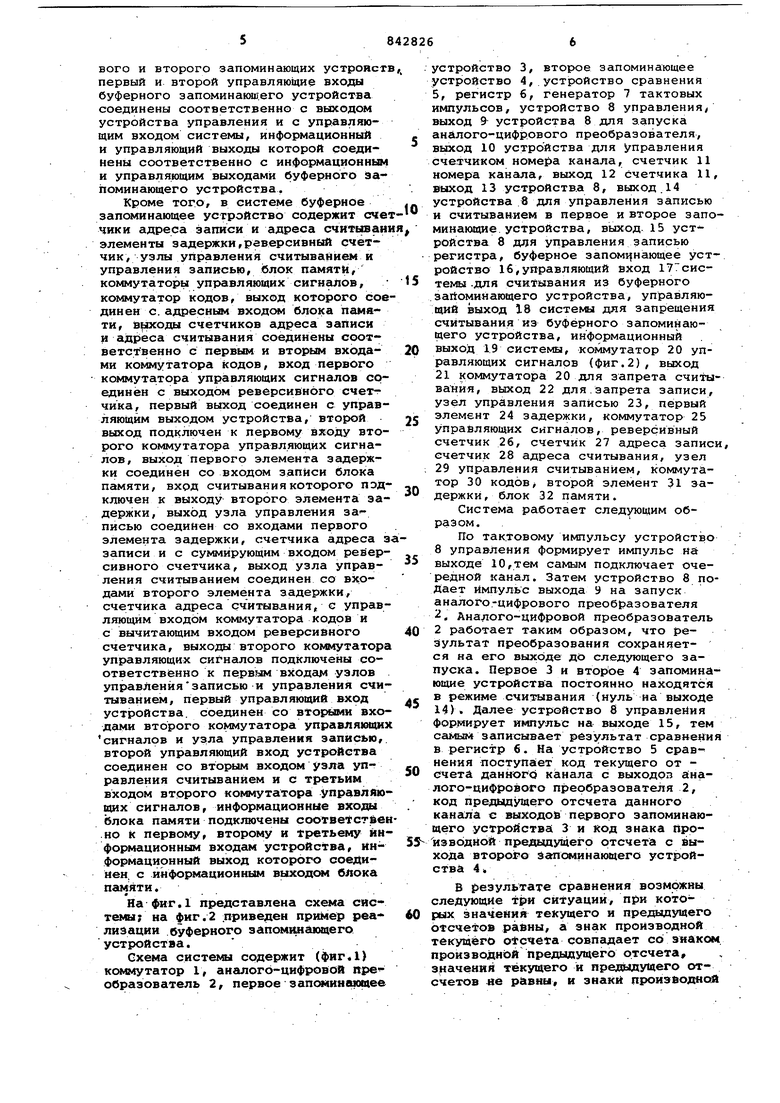

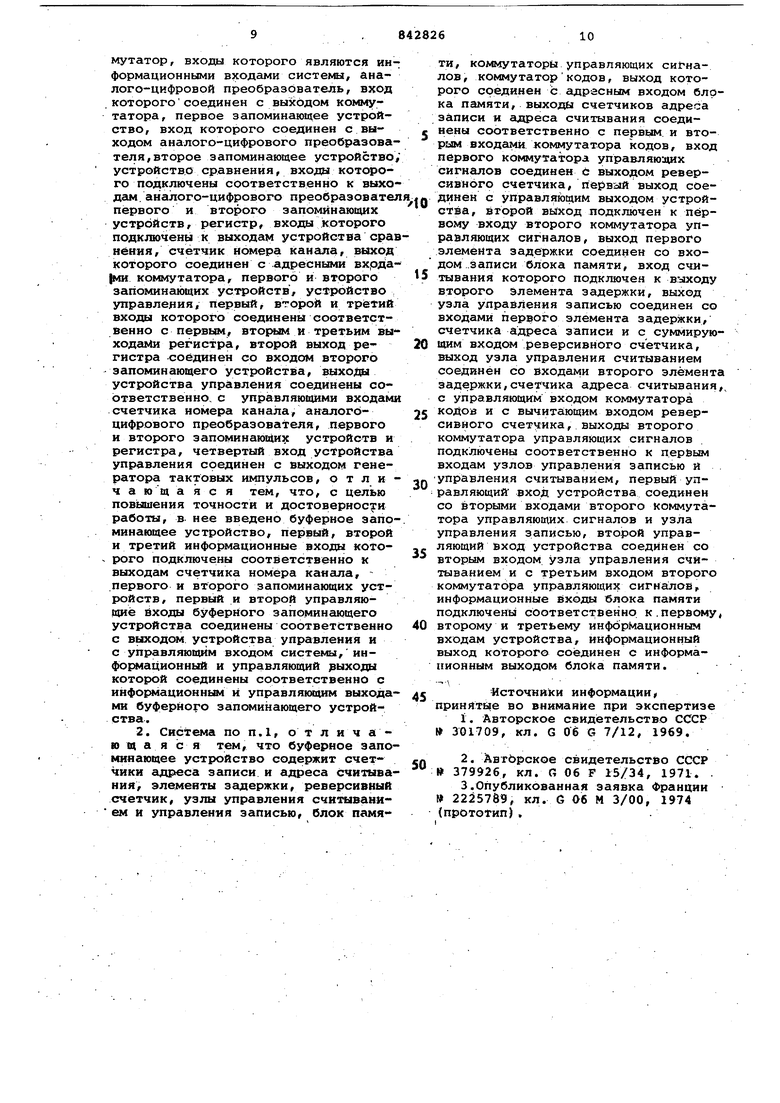

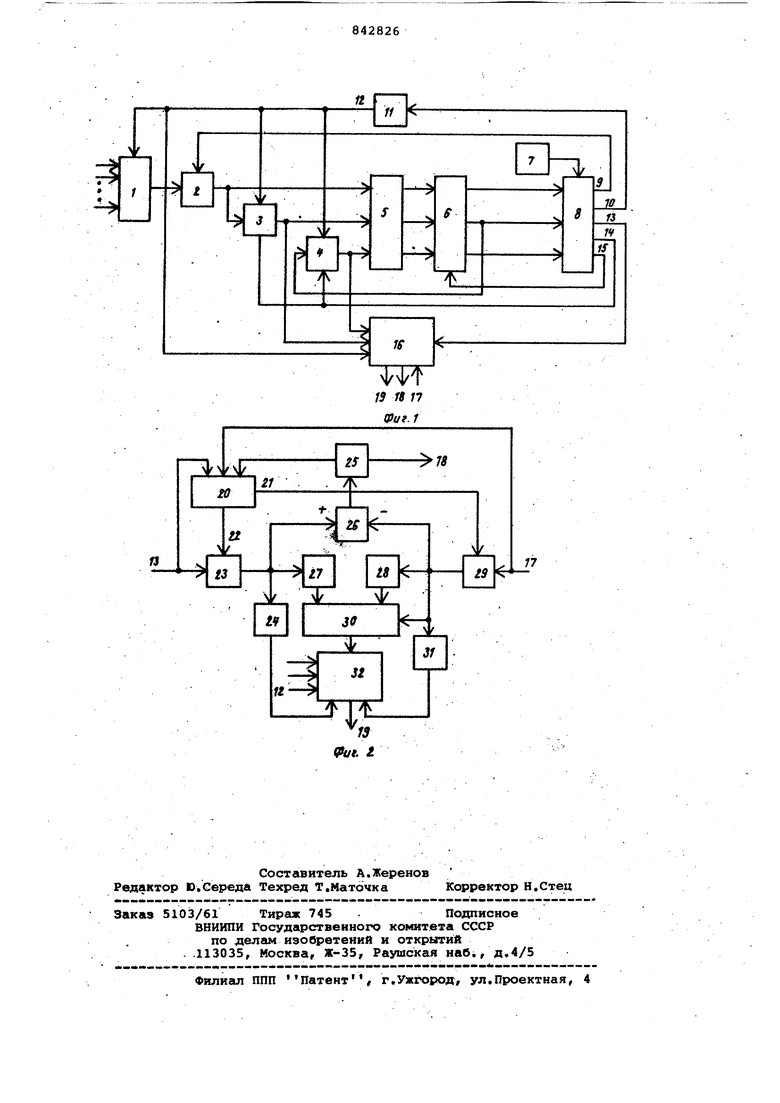

Цепь изобретения - повышение тоЧностн и достоверности работы.: Поставленная цель достигается тем, что в систему введено буферное запоминёнощее устройство, первь|й, второй и третий информационные входы которого подключены соответственно к выходам счетчика номера канала,первого и второго запоминающих устройст первый и второй управляющие входы буферного запоминающего устройства соединены соответственно с выходом устройства управления и с управляющим входом системы, информационный и управляющий выходы которой соединены соответственно с информационным и управляющим выходами eSyфepнoгo Запоминающего устройства. Кроме того, в системе буферное запоминающее устройство содержит сче чики адреса записи и адреса считЕЛван элементы задержки,реверсивный счетчик, узлы управления считыванием и управления записью, блок памяти, коммутаторы управляющих сигналов, коммутатор кодов, выход которого со динен с. адресньош входом блока памяти, в лсоды счетчиков адреса записи и ajapieca считывания соединены соответственно с первым и вторым входами коммутатора кодов, вход первого коммутатора управляющих сигналов со единён с выходом реверсивного счет- чика, первый выход соединен с управ ляю1айм выходом устройства, второй выход подключен к первому входу вто рого коммутатора управляющих сигналов, выход первого элемента задержки соединен со входом записи блока памяти, вход считывания которого под ключен к выходу второго элемента за держки, выход узла управления записью соединен со входё№1и первого элемента задержки, счетчика адреса записи и с суммирующим входом рейер сивного счетчика, выход узла управления считыванием соединен со входами второго элемента задержки, счетчика адреса считывания, с управ ляющим входом коммутатора кодов и с вычитающим входом реверсивного счетчика, выходы второго коммутатор управляющих сигналов подключены соответств1енно к первым входсци узлов управлениязаписью и управления счи тыванием, первый управляющий вход устройства, соединен со вторыми вхо дами второго коммутатора управляющи сигналов и узла управления записью, второй управляющий вход устройства соединен со вторым входом узла управления считыванием и с третьим входом второго коммутатора управляю щих сигналов, информационные входы блока памяти подключены соответстве .но к первому, второму и третьему ин формационным входам устройства, ин формационный выход которогчэ соедимеи, с информационным выходсм блока памяти. , На фиг.1 представлена схема системы; иа фиг.2 .приведен пример peaлиэации буферного запоминающего устройства. Схема системы содержит (фигЛ) коммутатор 1, аиалого-цифровой ирв образователь 2, первое запсжинаюцее 4устройство 3, второе запоминающее устройство 4, устройство сравнения 5, регистр 6, генератор 7 тактовых импульсов, устройство 8 управления, выход 9 устройства 8 для запуска аналого-цифрового преобразователя, выход 10 устройства для управления счетчиком номера канала, счетчик 11 номера канала, выход 12 счетчика 11, выход 13 устройств.а 8, выход. 14 устройства .8 для управления записью и считыванием в первое и второе запоминающие устройства, выход. 15 устройства 8 для управления записью регистра, буферное запом1 нающее устройство 16,управляющий вход 177системы .для считывания из буферного .зайоминающего устройства, управляющий выход 18 системы для запрещения считывания из буферного запоминающего устройства, информационный выход 19 системы, коммутатор 20 управляющих сигналов (Фиг.2), выход 21 коммутатора 20 для запрета считывания, выход 22 для.запрета записи, узел управления записью 23, первый элемент 24 задержки, коммутатор 25 управляющих сигналов, реверсивный счетчик 26, счетчик 27 адреса записи, счетчик 28 адреса считывания, узел 29 управления считыванием, коммутатор 30 кодов, второй элемент 31 задержки, блок 32 памяти. Система работает следующим образом. По так.Товому импульсу устройство 8 управления формирует импульс на выходе 10,тем самым подключает очередной канал. Затем устройство 8 поДает Импульс выхода 9 на запуск аналого-цифрового преобразователя 2, Аналого-цифровой преобразователь 2 работает таким образом, что результат преобразования сохраняется на его выходе до следующего запуска. Первое 3 и второе 4 запоминающие устройства постоянно находятся в режиме считывания (нуль на выходе 14). Далее устройство 8 управления формирует импульс на выходе 15, тем самыг4 записывает результат сравнения в регистр 6. На устройство 5 сравнения nocTynaieT код текущего от счета данного канала с выходов аналого-цифрового преобразователя 2, код предыдущего отсчета данного канала с выходов первого запоминающего устройства 3 и код знака производной предыдущего отсчета с йыхода второго запсядинающего устройства 4 В результате сравнения возможны ледующие три ситуации, при которых значения текущего и предыдущего тсчетов рабны, а знак производной екущего отсчета совпадает со знаком роизводнЬй предыдущего отсчета, начения текущего и предыдущего отчетов не равны, и знаки проиэбоднай

текущего и предыдущего отсчетов не совпадают.

В первом случае никакие операции не производятся.

Во втором случае устройство 8 управления формирует импульс на выходе 14 для записи значения текущего отсчета в первое запоминающее устройство 3 и записи знака производной ти у1цего отсчета во второе запоминающееустройство 4.

В третьем случае устройство управления 8 формирует импульс навыходе 13, который осуществляет запись в буферное : запоминающее устройство 3.6 зна.чения экстремума, его типа (минимум или максимум) и номера канала Далее устройство 8 управления формирует импульс на выходе 14 записи значения текущего отсчета и знака производной текущего отсчета в первое 3 и второе 4 запоминающее устройства соответственно.

Интервалы между импульсс№ и, вырабатываемыми устройством 8 управления, выбираются с учетом времени установления элементов схемы, причем время между записью в Ьуферное запоминающее устройство и записью текущих значений отсчета и знака производной выбирается достаточным для выполнения записи в буферное запоминающее устройство и считывания из него.

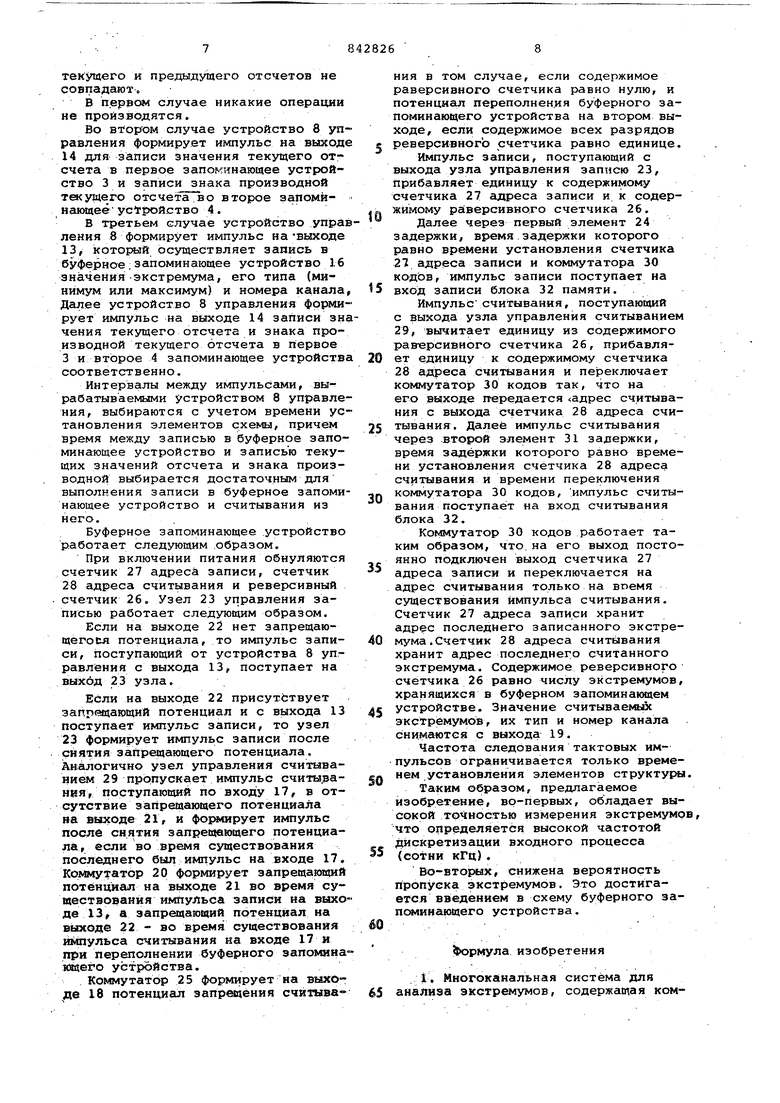

Буферное запоминающее устройство работает следующим .образом.

При включении питания обнуляются счетчик 27 адреса записи, счетчик 28 адреса считывания и реверсивный счетчик 26. Узел 23 управления записью работает следующим образом.

Если на выходе 22 нет запрещающегоья потенциала, то импульс записи, поступающий от устройства 8 управления с выхода 13, поступает на выход 23 узла.

Если на выходе 22 присутствует запрещающий потенциал и с выхода 13 поступает импульс записи, то узел 23 формирует импульс записи после рйятия запрещающего потенциала. Аналогично узел управления считыванием 29 пропускает импульс считывания, поступающий по входу 17, в отсутствие запрегаающего потенциала на выходе 21, и формирует импульс после снятия запрещающего потенциала, если во время существования последнего был импульс на входе 17. Коммутатор 20 формирует запрещающий потенциал на выходе 21 во время существования импульса записи на выходе 13, а запрещающий потенциал на выходе 22 - во время существования импульса считывания на входе 17 и при переполнении буферного запомина нацего устройства.

Коммутатор 25 формирует на выходе 18 потенциал запрещения счйтывания в том случае, если содержимое раверсивного счетчика равно нулю, и поТенцнсШ переполнения буферного запоминающего устройства на втором выходе, если содержимое всех разрядов реверсивного счетчика равно единице.

Импульс записи, поступающий с выхода узла управления записю 23, Прибавляет единицу к содержимому счетчика 27 адреса записи и к содержимому раверсивного счетчика 26.

Далее через первый элемент 24 задержки, время задержки которого равно времени установления счетчика 21 адреса записи и коммутатора 30 кодов, импульс записи поступает на вход записи блока 32 памяти.

Импульссчитывания, поступающий с выхода узла управления считыванием 29, -вычитает единицу из содержимого рав ерсивного счетчика 26, прибавляет единицу к содержимому счетчика 28 адреса считывания и пе|реключает коммутатор 30 кодов так, что на его выходе передается «адрес считывания с выхода счетчика 28 адреса считывания. Далее импульс считывания через второй элемент 31 задержки, время задержки которого равно времени установления счетчика 28 адреса считывания и времени переключения коммутатора 30 кодов, импульс считывания поступает на вход считывания блока 32.

Когдаиутатор 30 кодов работает таким образом, что.на его выход постоянно подключен выход счетчика 27 адреса записи и переключается на адрес считывания только на впемя существования импульса считывания. Счетчик 27 адреса записи хранит адрес последнего записанного экстремума.Счетчик 28 адреса считывания хранит адрес последнего считанного экстремума. Содержимое реверсивного счетчика 26 равно числу экстремумов, хранящихся в буферном запоминающем устройстве. Значение считываекиЛ экстремумов, их тип и номер канала снимаются с выхода 19.

Частота следования тактовых импульсов ограничивается только временем .установления элементов структуры

Таким образом, предлагаемое изобретение, во-первых, обладает высокой точностью измерения экстремумо что определяется высокой частотой дискретизации входного процесса (сотни кГц).

Во-вторых, снижена вероятность пропуска экстремумов. Это достигается введением в схему буферного запоминающего устройства.

Ъормула изобретения

1. Иногоканальная система для анализа экстремумов, содержащая коммутатор, входы которого являются информационными входами системы, аналого-цифровой преобразователь, вход которогосоединен с выходом коммутатора, первое запоминающее устройство, вход которого соединен с вы- ходом аналого-цифрового преобразователя, второе запоминающее устройство; устройство сравнения, входы которого подключены соответственно к выходгил. аналого-цифрового преобразователя, первого и второго запоминающих устройств, регистр, входа которого подключены к выходам устройства сравнения, счетчик номера канала, выход которого соединен с адресными вхрдаии коммутатора, первого и второго 5 запомингцощих устройств, устройство управлеяия, первый, второй и входы которого соединены соответственно с первым, вторым и третьим выходами регистра, второй выход ре- 20 гистра соединен со входом второго запоминающего устройства, выхода устройства управления соединены соответственно, с управляющими входами счетчика номера канала, аналоге- 25 цифрового преобразователя, первого и второго запоминающих устройств и регистра, четвертый вход устройства управления соединен с выходом генератора тактовых импульсов, о т л и - Q чающаяся тем, что, с целью пов1Е 1шения точности и достоверности работы, в нее введено буферное запо-. минающее устройство, первый, второй и третий информационные входы кото- рого подключены соответственно к выходам счетчика номера канала, .первого и второго запоминающих устройств, первый и второй управляющие входы буферного запоминающего устройства соединены соответственно 40 с выходом устройства управления и с управляющим входом системы,информационный и управляющий которой соединены соответственно с информационным и управляющим выходами буферного запоминающего устройства.

2. Система по п.1, от л ич аю ц а я с я тем, что буферное запоминающее устройство содержит счет- -я чики адреса записи и адреса считывания, элементы задержки, реверсивный счётчик, узлы управления считыванием и управления записью, блок памяти, коммутаторы управляющих сигналов, коммутаторкодов, выход которого соединен с адресным входом блока памяти, выходы счетчиков адреса записи и сшреса считывания соединены соответственно с первым и вторым входами, коммутатора кодов, вход первого коммутатора управляющих сигналов соединен с выходом реверсивного счетчика, первый выход соединен с управляющим выходом устройства, второй выход подключен к первому входу второго коммутатора управляющих сигналов, выход первого элемента задержки соединен со входом ..записи блока памяти, вход считывания которого подключен к ваходу второго йламента задержки, выход узла управления записью соединен со входами первого элемента задержки, счетчика адреса записи и с суммирующим входс 1 реверсивного счетчика, выход узла управления считыванием соединён со входами второго элемент задержки,счетчика адреса считывания с управляющим входом коммутатора кодов и с вычитающим входом реверсивного счетчика, выходы второго коммутатора управляющих сигналов подключены соответственно к первым входам узлов управления записью и управления считыванием, первый управляющий вход устройства соединен со вторыми входами второго коммутатора управляющих, сигналов и узла управления записью, второй управляющий вход устройства соединен со вторым входом узла управления считыванием и с третьим входом второго коммутатора управляющих сигналов, информационные входы блока памяти подключены соответственно к.первому второму и третьему информационным входам устройства, информационный выход которого соединен с информационным выходом блока памяти.

---у .

Источники информации, принятые во внимание при экспертизе

1,Авторское свидетельство СССР 301709, кл. G 06 G 7/12, 1969.

2,Автбрское свидетельство СССР 379926, кл. G 06 F 15/34, 1971. .

3.Опубликованная заявка Франции 2225789, кл. G Об М 3/00, 1974 (прототип),.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальная система для анализа экстремумов | 1978 |

|

SU750496A1 |

| Устройство для воспроизведения функций | 1985 |

|

SU1273955A1 |

| Устройство для акустико-эмиссионного контроля дефектов | 1986 |

|

SU1337760A1 |

| Функциональный аналого-цифровой преобразователь | 1985 |

|

SU1260979A1 |

| ПРИЕМНОЕ УСТРОЙСТВО ГИДРОЛОКАТОРА БОКОВОГО ОБЗОРА | 1993 |

|

RU2060516C1 |

| Устройство для воспроизведения псевдообъемного изображения | 1984 |

|

SU1233302A1 |

| Многоканальный функциональный генератор | 1984 |

|

SU1191922A1 |

| Адаптивное устройство для передачи информации | 1989 |

|

SU1735884A1 |

| Осциллограф с матричным экраном | 1983 |

|

SU1129529A1 |

| Устройство для определения углового положения указателя стрелочных приборов | 1987 |

|

SU1532812A1 |

Авторы

Даты

1981-06-30—Публикация

1977-09-23—Подача