Изобретение относится к информационно-измерительной технике и предназначено для сбора и передачи информации от датчиков в цифровом виде.

Известны устройства для передачи информации, обеспечивающие последовательный опрос датчиков информации и передачу ее в канал связи„ Недостатком таких устройств является значительная избыточность передаваемой информации. Это снижает ее достоверность, приводит к нерациональному использованию всех средств) передач данных.

Наиболее близким к предлагаемому является по технической сущности устройство, содержащее регистр теку - щей выборки, выход которого соединен с первым входом блока сравнения, блок оперативной памяти, счетчик записи, вход которого соединен с входом первого элемента задержки, блок буферной памяти, счетчик считывания, второй элемент задержки, элементы И, ИЛИ. Данное устройство, обеспечивает вы- деление существенных отсчетов из входного потока данных и согласование полученного потока с интенсив- J

Q0 СП

оо

00

4

ностью считывания информации в канал связи. Недостатком данного устройства является то, что, возможно переполнение буферной памяти при активном изменении входных сигналов и не формируется информация для восстановления расположения отсчетов во време ни„ Все это в совокупности приводит к тому, что достоверность передаваемой информации невысока, восстановить исходные, сигналы удается весьма приближенное

Целью изобретения является повышение достоверности передаваемой информации о

Указанная цель достигается тем, что в известное устройство вводятся блоки- и связи, позволяющие в зависимости от уровня заполнения блока буферной памяти регулировать частоту опроса входных датчиков и формировать временную информацию от отсчетах, исключая переполнение блока буферной памяти, а именно: блок управления частотой опроса датчиков, на вход которого подается информация об уровне заполнения буферной памяти, а на выходах формируются сигнал управления приемом данных от датчиков и код коэффициента увеличения периода опроса датчиков J-триггер, изменяющий свое состояние перед каждым циклом опроса датчиков, соединенный своим выходом с информационным входом блока буферной памяти, что позволяет каждое слово буферной памяти однозначно отнести к одному из последовательных циклов опроса, счетчик адресов датчиков, формирующий сигналы начала циклов опроса, а также адресную информацию для блока буферной памяти, RS-триггер, инвертор, элементы задержки, И, ИЛИ соответствующими связями обеспечивают принудительную запись последнего счетчм- ка, если за цикл опроса существенных отсчетов не оказалось, реверсивный счетчик, формирующий данные об уровне заполнения буферной памяти

10

20

временная диаграмма, поясняющая работу устройства,

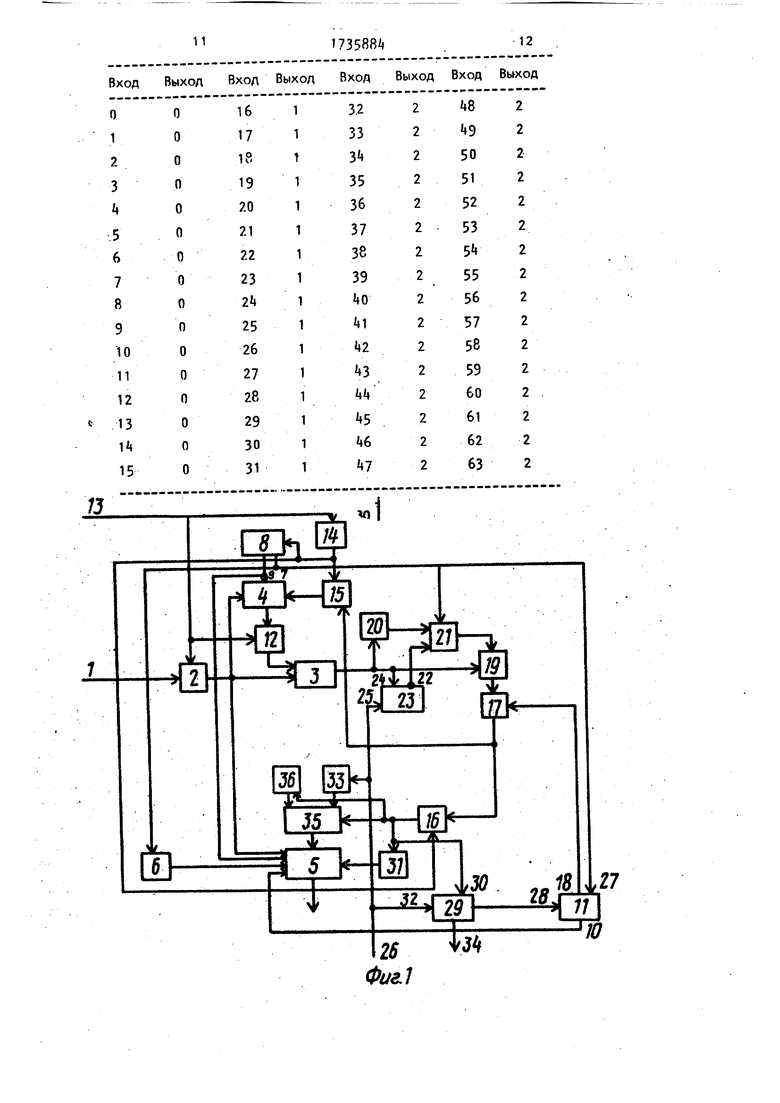

Устройство содержит вход 1 для -ж подачи отсчетов сигналов от датчиков преобразованных в цифровую форму внешним АЦП, регистр 2 текущей выборки, выход которого связан с входом блока 3 сравнения, информационным входом блока k оперативной памят ти и информационным входом блока 5 буферной памяти. Кроме, того, к информационному входу блока 5 подключены выход Т-триггера 6, вход которого связан с выходом 7 переполнения счетчика 8 адреса, информационный выход 9 блока 8 и выход 10 блока 11 управления частотой опроса датчиков. Выход блока k связан с входом регистра 12 памяти, выход которого соединен с вторым входом блока 3, а вход управления - с синхровходом -13 устройства и входом управления блока 2„ Через элемент 1 задержки вход 13 соединяется с первыми входами элементов И 15 и 16, с входом блока 8„ Вторые входы элементов 15 и 16 связаны с входом элемента И 17, первый вход которого соединен с выходом 18 блока 11, второй - с выходом элемента ИЛИ

30 19. Первый вход последнего соединен с выходом блока 3 и через инвертор 20 с первым входом элемента И 21, второй вход которого соединен с выходом 7 блока 8, третий вход - с ин- .

35 версным выходом 22 RS-триггера 23, а выход - с вторым входом блока 19. S-вход 2k блока соединен с выходом блока 3, R-вход 25 - с входом 26 считывания устройства. Выход 7 блока 8 соединен с входом 27 блока 11, вход 28 которого соединен с информационным выходом реверсивного счетчика 29, инкрементный вход 30 которого подключен к выходу элемента 16 и через элемент 31 задержки к управляющему входу блока 5. Декрементный вход 32 блока 29 соединен с входом 26, входом счетчика 33 считывания. Выход 3 переполнения блока 29 является выходом

25

40

45

и сигнал управления считыванием инфор- 50 Разрешения считывания устройства.Вход

управления коммутатора 35 соединен с выходом элемента 16 и входом счетчика 36 записи, выход которого связан с первым информационным входом коммутатора 35, а выход счетчика 33 - с вторым информационным входом коммута- тора 35. Выход блока 5 является выходом устройства.

мации из нее в канал связи,, коммутатор, инвертор, элементы задержки, элементы И, обеспечивают необходимую логику работы устройства в целом.

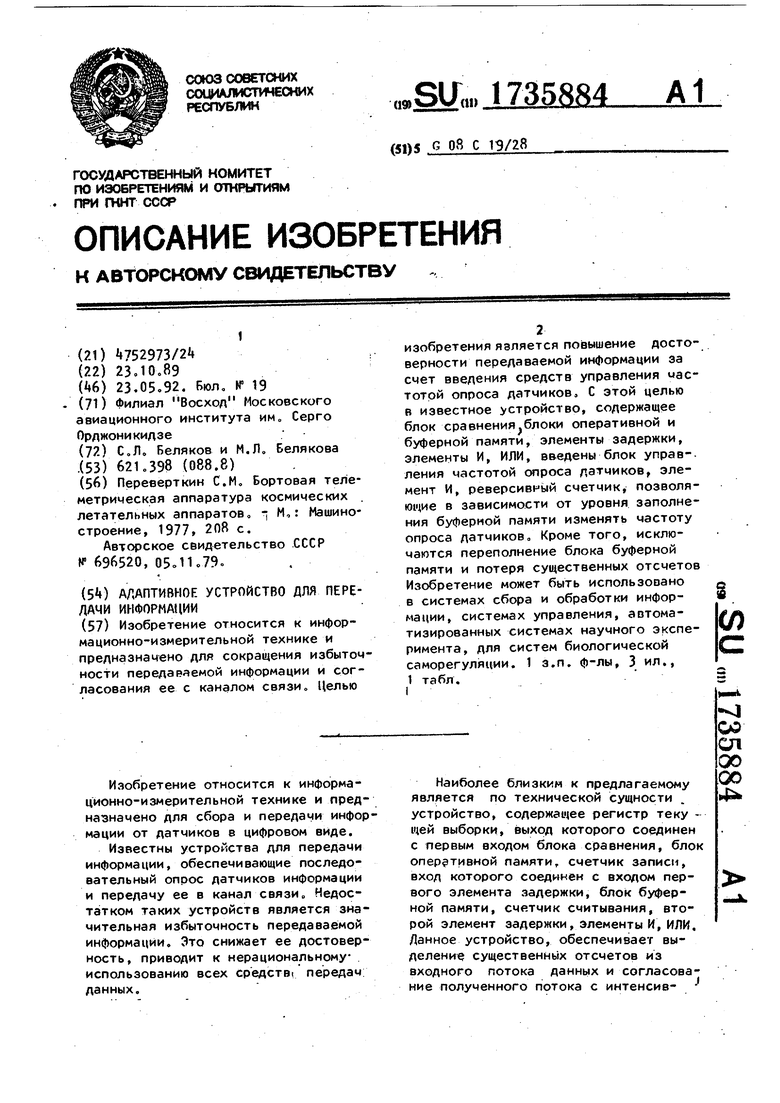

На фиг.1 представлена блок-схема предлагаемого устройства;на фиг.2 - блок-схема возможной реализации блока управления частотой; на фиг.З ,

10

20

7358844

временная диаграмма, поясняющая работу устройства,

Устройство содержит вход 1 для -ж подачи отсчетов сигналов от датчиков преобразованных в цифровую форму внешним АЦП, регистр 2 текущей выборки, выход которого связан с входом блока 3 сравнения, информационным входом блока k оперативной памят ти и информационным входом блока 5 буферной памяти. Кроме, того, к информационному входу блока 5 подключены выход Т-триггера 6, вход которого связан с выходом 7 переполнения счетчика 8 адреса, информационный выход 9 блока 8 и выход 10 блока 11 управления частотой опроса датчиков. Выход блока k связан с входом регистра 12 памяти, выход которого соединен с вторым входом блока 3, а вход управления - с синхровходом -13 устройства и входом управления блока 2„ Через элемент 1 задержки вход 13 соединяется с первыми входами элементов И 15 и 16, с входом блока 8„ Вторые входы элементов 15 и 16 связаны с входом элемента И 17, первый вход которого соединен с выходом 18 блока 11, второй - с выходом элемента ИЛИ

30 19. Первый вход последнего соединен с выходом блока 3 и через инвертор 20 с первым входом элемента И 21, второй вход которого соединен с выходом 7 блока 8, третий вход - с ин- .

35 версным выходом 22 RS-триггера 23, а выход - с вторым входом блока 19. S-вход 2k блока соединен с выходом блока 3, R-вход 25 - с входом 26 считывания устройства. Выход 7 блока 8 соединен с входом 27 блока 11, вход 28 которого соединен с информационным выходом реверсивного счетчика 29, инкрементный вход 30 которого подключен к выходу элемента 16 и через элемент 31 задержки к управляющему входу блока 5. Декрементный вход 32 блока 29 соединен с входом 26, входом счетчика 33 считывания. Выход 3 переполнения блока 29 является выходом

25

40

45

Разрешения считывания устройства.Вход

управления коммутатора 35 соединен с выходом элемента 16 и входом счетчика 36 записи, выход которого связан с первым информационным входом коммутатора 35, а выход счетчика 33 - с вторым информационным входом коммута- тора 35. Выход блока 5 является выходом устройства.

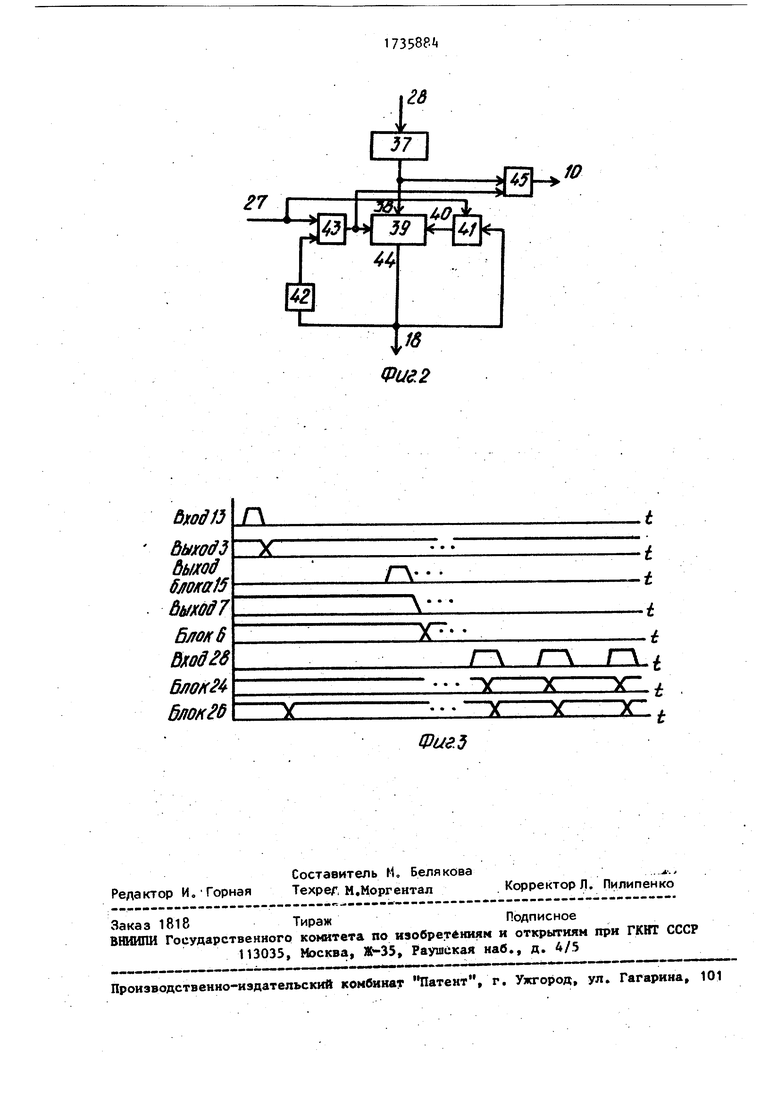

Блок управления частотой на фиг.2 содержит кодер 37, вход которого яв- ляется входом 28 блока 11, и связан с информационным входом 38 вычитающего счетчика 39 Управляющий вхо АО является выходом элемента И 1 , первый вход которого связан с входом 27 блока 11 и через инвертор 42 с первым входом элемента И 43, второй вход которого связан с входом 27, а выход - со сметным входом блока 39. Выход 44 заема счетчика 39 соединен с входом инвертора 42 и выходом 18 блока 11, Вход 38 через регистр 45 памяти связан с выходом 10 блока 1.1«, Управляющий вход блока 45 соединен с выходом элемента 43.

Устройство работает следующим образом,

В исходном состоянии блоки 2,4, 5,12,23,29,33,36,39 установлены в нуль, счетчик 8 содержит единицу, состояние Т-триггера 6 не определено, на выходе блока 3 - нуль, на управляющих входах блоков 4 и 5 уров -ни нуля, соответствующие операции чтения. На выходе 18 - единица, на выходе 7 - нуль, на выходе 34 - единица , При подаче первого отсчета, сопровождаемого синхроимпульсом на входе 13 (фигЛ), он запоминается в регистре 2. Одновременно,в регистр 12 записывается содержимое блока 4 с адресом 1. Элемент 14 задержки обеспечивает блокировку разрешения записи в блоках 4 и 5„ Это необходимо для правильной работы устройства, в противном случае для промежуточного отсчета могла бы выполниться запись по сигналу существенности предыдущего отсчета о Если обозначить через t, задержку i-м блоке, то

-и

t

2 + t3 + t +tz,

н- t,, +

+ t

IT

t3iЕсли отсчет существенный, то на выходе блока 3 единица, которая устанавливает RS-триггер 23 в единицу, и если запись разрешена блоком 11 .(на входе 18 единица), формируются единичные сигналы записи на входах элементов 16 и 15. Если отсчет несущественный, на выходе блока 3 - нуль, но сигнал записи все же может быть сформулирован по второму входу блока 19. Это имеет место в случае, когда за весь цикл опроса не было

35881

, 10

Г5

существенных отсчетов (в блоке 23 - нуль l, последний отсчет не существенен и в блоке 8 адрес последнего датчика (на выходе 7 - единиц). В этом случае несущественный отсчет принудительно записывается в память как существенный, чтобы не потерять информацию о времени расположения отсчетов последовательных циклов опроса Запись существенного отсче- . та в блок 5 осуществляется увеличением счетчика 36 на единицу, настройкой блока 35 и выдачей сигнала записи с задержкой, определяемой элементом 21 „ Ее величина

t

36

+ t

35

2Q По окончании импульса (по заднему фронту) на входе 13 переключается блок 8„ Длительность этого импульса

(t4, ts

)

Таким образом подготавливается адрес следующего датчика,

Временной интервал иежду импульсами (At) должен позволять сформировать, записать результаты, выпол- нить чтение из блока 4 и изменить в конце цикла состояние Т-триггера 6. Поскольку реально tg : t, то

&t t4 + t

ИПо окончании цикла опроса-блок 8 1, триггер 6

содержит , триггер b установлен в инверсное состояние относительно предыдущего цикла„

Блок 11 управления частотой работает следующим образом.

Кодер 37 преобразует код из блока 29, равный числу занятых ячеек в блоке 5, в начальное состояние

счетчика 39 Кодер 37 может быть реализован либо в виде схемы из логических элементов, либо в виде ПЗУ, ПЛМ. Код на выходе кодера 37 число циклов опроса датчиков, в течение котоРЫХ запрещена запись в блоках А и 5. Этот код по выходу 10 записывается в блок 5. Сигнал на выходе й равен единице при нулевом состоянии счетчика 39 и является разрешающим (выход 18)„ Запись код с входом 38 возможна при нулевом состоянии счетчика 39 и выполняется только в конце цикла опроса сигналом с входа 27. Этим же сигналом инициируется вычитание еди

ницы в счетчике 39. Крличество пропущенных циклов заносится в блок 5 с каждым существенным отсчетом нового цикла опроса. Запись в блоках 39 kS выполняется по заднему фронту сигнала на входе 27.

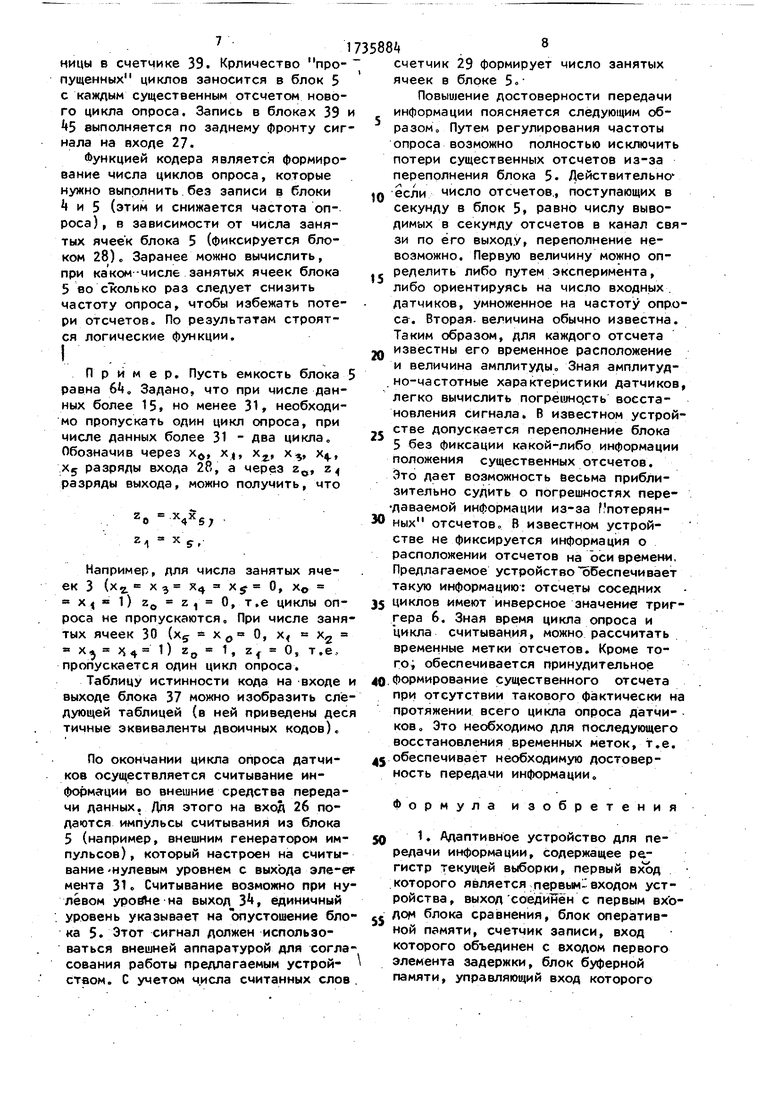

Функцией кодера является формирование числа циклов опроса, которые нужно выполнить без записи в блоки 1 и 5 (этим и снижается частота опроса), в зависимости от числа занятых ячеек блока 5 (фиксируется блоком 28). Заранее можно вычислить, при каком-числе занятых ячеек блока 5 во сколько раз следует снизить частоту опроса, чтобы избежать потери отсчетов. По результатам строятся логические функции.

I

Пример. Пусть емкость блока равна Задано, что при числе данных более 15, но менее 31, необходимо пропускать один цикл опроса, при числе данных более 31 - два цикла. Обозначив через хо, х, хг, х, х., х5 разряды входа 28, а через z0, z разряды выхода, можно получить, что

X4xs;

Например, для числа занятых ячеек 3 (xz х .3 х $- 0 о

1)

Z

1

О, т.е циклы опроса не пропускаются. При числе заня(х,1. z

О,

. О,

т.е.

тых ячеек 30 л5

« Э Х-4 1) zo f

пропускается один цикл опроса.

Таблицу истинности кода на входе и выходе блока 37 можно изобразить следующей таблицей (в ней приведены деся тичные эквиваленты двоичных кодов).

По окончании цикла опроса датчиков осуществляется считывание информации во внешние средства передачи данных. Для этого на вход 26 подаются импульсы считывания из блока 5 (например, внешним генератором импульсов) , который настроен на считывание -нулевым уровнем с выхода эле-ет мента 31 о Считывание возможно при нулевом уройне на выход 3, единичный

45 обеспечивает необходимую достоверность передачи информации.

Формула изобретени

5Q 1. Адаптивное устройство для передачи информации, содержащее регистр текущей выборки, первый вход которого является первым-входом уст ройства, выход соединён с первым вх

уровень указывает на опустошение бло- 55 лом блока сравнения, блок оперативка 5. Этот сигнал должен использоваться внешней аппаратурой для согласования работы предлагаемым устрой- стаом. С учетом числа считанных слов

ной памяти, счетчик записи, вход которого объединен с входом первого элемента задержки, блок буферной памяти, управляющий вход которого

10

15

20

7358848

счетчик 29 формирует число занятых ячеек в блоке 5°Повышение достоверности передачи информации поясняется следующим образом Путем регулирования частоты опроса возможно полностью исключить потери существенных отсчетов из-за переполнения блока 5- Действительно- если число отсчетов, поступающих в секунду в блок 5, равно числу выводимых в секунду отсчетов в канал связи по его выходу, переполнение невозможно. Первую величину можно определить либо путем эксперимента, либо ориентируясь на число входных датчиков, умноженное на частоту опроса. Вторая- величина обычно известна. Таким образом, для каждого отсчета известны его временное расположение и величина амплитуды Зная амплитудно-частотные характеристики датчиков, легко вычислить погрешность восстановления сигнала. В известном устройстве допускается переполнение блока 5 без фиксации какой-либо информации положения существенных отсчетов. Это дает возможность весьма приблизительно судить о погрешностях пере- даваемой информации из-за потерян30 ных отсчетов В известном устройстве не фиксируется информация о расположении отсчетов на оси времени, Предлагаемое устройство обеспечивает такую информацию: отсчеты соседних

35 циклов имеют инверсное значение триггера 6. Зная время цикла опроса и цикла считывания, можно рассчитать временные метки отсчетов. Кроме того; обеспечивается принудительное

40 формирование существенного отсчета при отсутствии такового фактически на протяжении всего цикла опроса датчиков. Это необходимо для последующего восстановления временных меток, т.е.

45 обеспечивает необходимую достоверность передачи информации.

25

Формула изобретения

1. Адаптивное устройство для передачи информации, содержащее регистр текущей выборки, первый вход которого является первым-входом устройства, выход соединён с первым вх олом блока сравнения, блок оперативной памяти, счетчик записи, вход которого объединен с входом первого элемента задержки, блок буферной памяти, управляющий вход которого

91

соединен с выходом первого элемента задержки, счетчик1 считывания, второй элемент задержки, первый элемент И, выход которого соединен с управляющи входом блока оперативной памяти, второй, третий и четвертый элементы И, выход третьего элемента И подключен к первому входу элемента ИЛИ, отличающееся тем, что, с целью повышения достоверности передаваемой информации, в него введены счетчик адреса, регистр памяти, инвертор, Т- и RS-триггеры, коммутатор, реверсивный счетчик и блок управления частотой опроса датчиков, объединенные второй вход регистра текущей выборки, вход второго элемента задержки и первый вход регистра п

мяти являются вторым входом устроист- ю второй выходы блока управления частова, выход второго элемента задержки подключен к входу счетчика адреса .и первым входам первого и второго элементов И, первый выход счетчика адреса соединен с адресным входом блока оперативной памяти и первым информационным входом блока буферной памяти, второй выход подключен к первым входам третьего элемента И и блока управления частотой опроса датчиков и входу Т-триггера, информационный вход блока оперативной памяти и второй информационный вход.блока буферной памяти подключены к выходу регистра текущей выборки, выход Т-триггера соединен с третьим информационн- ным входом блока буферной памяти, адресный вход которого соединен с выходом коммутатора, первый и второй входы которого подключены к выходам счетчика записи и счетчика считывания соответственно, третий вход коммутатора подключен к выходу второго элемента И, вторые входы первого и второго элементов И подключены к выходу четвертого элемента И, выход блока оперативной памяти соединен с вторым входом регистра памяти, вы- ход которого подключен к второму входу блока сравнения, выход которого

30

той опроса датчиков соединены соот-е ветственно с первым входом четвертого элемента И и четвертым информационным входом блока буферной памяти,

25 выход элемента ИЛИ подключен к второму входу четвертого элемента И,

2. Устройство по п.1, о т л и чающееся тем. что блок управле- ния частотой опроса датчиков содержит кодер, регистр памяти, первый и второй элементы И, счетчик и инвертор, вход кодера является первым входом блока управления частотой опроса датчиков, выход которого подключен к первым входам регистра памяти

35 и счетчика, второй вход которого соединен с выходом первого элемента И, третий вход счетчика и второй вход регистра памяти подключены к выходу второго элемента И, первые входы

40 первого и второго элементов. И являются вторым входом блока управления частотой опроса датчиков, второй вход второго элемента И соединен с выходом инвертора, вход которого и

45 второй вход первого элемента И подключены к выходу счетчика, выход счетчика и выход регистра памяти являются соответственно первым и вторым выходами блока управления частотой опроса датчиков.

10

подключен к второму входу элемента ИЛИ, S-входу RS-триггера и через инвертор к второму входу третьего элемента И, третий вход которого соединен с инверсным выходом RS-триггера, объединенные R-вхсд RS-триггера, вход счетчика считывания и первый вход реверсивного счетчика являются третьим входом устройства, выход блока буферной памяти является первым выходом устройства, второй вход реверсивного счетчика соединен с выходом второго элемента И, первый вы- 5 ход реверсивного счетчика подключен к второму выходу блока управления частотой опроса датчиков, второй выход реверсивного счетчика является вторым выходом устройства, первый и

0

той опроса датчиков соединены соот-е ветственно с первым входом четвертого элемента И и четвертым информационным входом блока буферной памяти,

5 выход элемента ИЛИ подключен к второму входу четвертого элемента И,

2. Устройство по п.1, о т л и чающееся тем. что блок управле- ния частотой опроса датчиков содержит кодер, регистр памяти, первый и второй элементы И, счетчик и инвертор, вход кодера является первым входом блока управления частотой опроса датчиков, выход которого подключен к первым входам регистра памяти

5 и счетчика, второй вход которого соединен с выходом первого элемента И, третий вход счетчика и второй вход регистра памяти подключены к выходу второго элемента И, первые входы

0 первого и второго элементов. И являются вторым входом блока управления частотой опроса датчиков, второй вход второго элемента И соединен с выходом инвертора, вход которого и

5 второй вход первого элемента И подключены к выходу счетчика, выход счетчика и выход регистра памяти являются соответственно первым и вторым выходами блока управления частотой опроса датчиков.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для передачи информации | 1981 |

|

SU1012311A1 |

| Устройство для измерения параметров жидкости | 1990 |

|

SU1830460A1 |

| Устройство для ввода информации | 1982 |

|

SU1056175A1 |

| Устройство для передачи измерительной информации | 1982 |

|

SU1062753A1 |

| Адаптивный коммутатор | 1988 |

|

SU1536425A1 |

| Устройство для управления считыванием и вводом информации | 1990 |

|

SU1751786A1 |

| Передающее устройство адаптивной телеизмерительной системы | 1988 |

|

SU1499389A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ В АДАПТИВНЫХ ТЕЛЕМЕТРИЧЕСКИХ СИСТЕМАХ | 1995 |

|

RU2103745C1 |

| Устройство для ввода информации | 1982 |

|

SU1049893A1 |

| Устройство для измерения и регистрации частоты вращения вала скважинного забойного двигателя | 1984 |

|

SU1265294A1 |

Изобретение относится к информационно-измерительной технике и предназначено для сокращения избыточности передаваемой информации и согласования ее с каналом связи. Целью изобретения является повышение достоверности передаваемой информации за счет введения средств управления частотой опроса датчиков, С этой целью в известное устройство, содержащее блок еравнения блоки оперативной и буферной памяти, элементы задержки, элементы И, ИЛИ, введены блок управ-- ления частотой опроса датчиков, элемент И, реверсивный счетчик, позволяющие в зависимости от уровня заполнения буферной памяти изменять частоту опроса датчиков. Кроме того, исключаются переполнение блока буферной памяти и потеря существенных отсчетов Изобретение может быть использовано в системах сбора и обработки информации, системах управления, автоматизированных системах научного эксперимента, для систем биологической саморегуляции. 1 з.п. ф-лы, 3 ил., 1 табл. § л

ФигЗ

| Перееерткин С.М | |||

| Бортовая телеметрическая аппаратура космических летательных аппаратов, М,: Машиностроение, 1977, 208 с | |||

| Адаптивное устройство для передачи информации | 1977 |

|

SU696520A1 |

| ( АДАПТИВНОЕ УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ | |||

Авторы

Даты

1992-05-23—Публикация

1989-10-23—Подача