(54) ИНТЕГРАТОР С ЗАПОМИНАНИЕМ

выходом устройства, а его другой вход подключен к выходу генератора пилообразного напряжения, соединенного также с одним из входов вспомогательного компаратора, другой вход которого соединен с шиной опор ного напряжения, а выход - со входом блокировки генератора корректирующих импульсов. Входы синхронизации генераторов соединены с выходом операционного усилителя 3.

Это устройство достаточно сложно из-за, наличия в цепи коррекции двух коммутирующих элементов, необходимости иметь разнополярный выход у генератора корректирующих импульсов и использования в каждом интеграторе своего генератора пилообразного напряжения и генератора корректирую щих импульсов, так как они синхронизируются от выходного напряжения устройства. Это затрудняет использование устройства в блоках долговременных аналоговых запоминающих устройств с применением современнь1Х логических микросхем, которые в большинстве случаев являются однополярными. Кроме того, устройст во отличается повышенньом потреблением, энергии в цепи коррекции, так как, с одной стороны, мощность гене ратора корректирующих импульсов должна быть достаточно большой для обеспечения требуемой коррекции (заряда конденсатора-В коротких промежутках времени), а, с другой стороны, выход этого генератора большую часть периода коррекции заземлен через коммутирующий элемент.

Цель изобретения - упрощение устройства и снижение потребляемой энергии.

Поставленная цель достигается тем, что в интегратор с запоминанием, содержащий операционный усилит ль, вход которого через интегрирующий конденсатор подключен к его выходу, через последовательно соединенные первый коммутирующий элемент и входной импеданс соединен со входом интегратора и через последовательно соединенные второй коммутирующий элемент и ограничивающий элемент подключен к выходу компаратора и входу одновибратора, управляющий вход первого коммутирую щего элемента подключен к входу управления режимом работы интегратора, генератор пилообразного напряжения и генератор корректирующих импульсов, введен элемент И, причем выход одновибратора соединен с управляющим входом второго коммутирующего элемента и первым входом элемента И, второй вход которого подключен к выходу генератора корректирующих импульсов, выходы элемента И и генератора пилообразного напряжения соединены соответственно с первым и вторыг/ входами компаратора, третий вход которого подключен к выходу операционного усилителя, вход блокировки одновибратора подключен к входу управления режимом работы интегратора, а к входу синхронизации генератора пилообразного напряжения подключен выход генератора корректирующих импульсов.

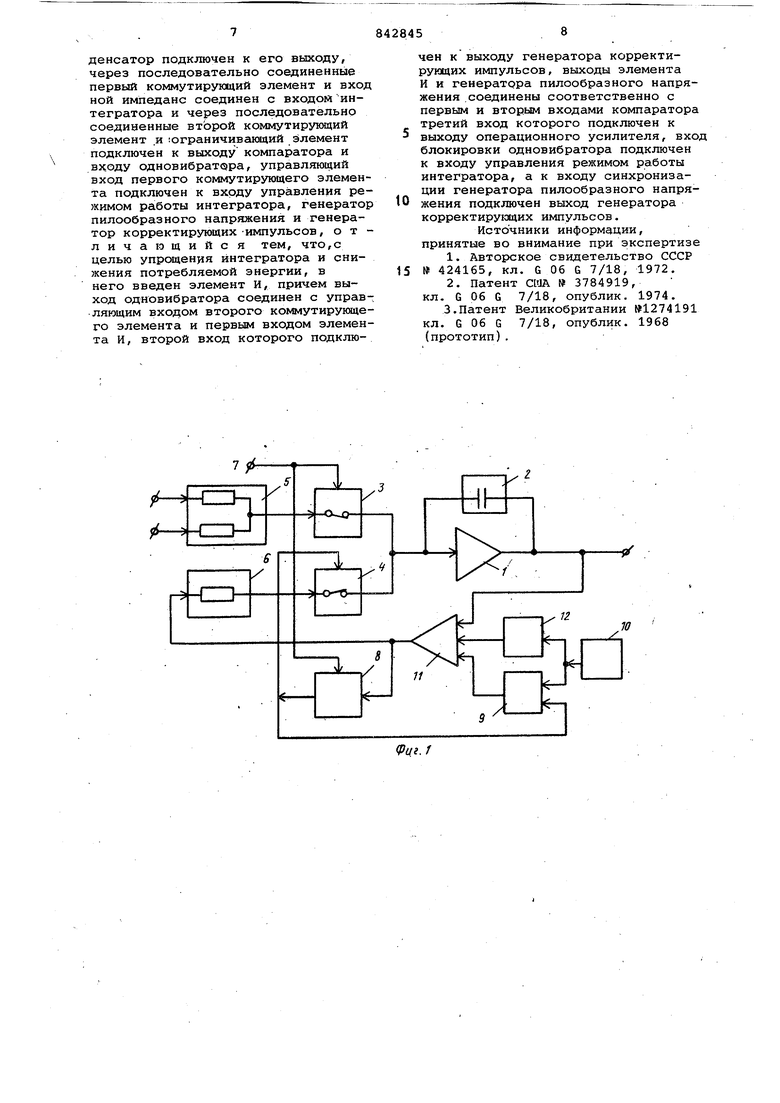

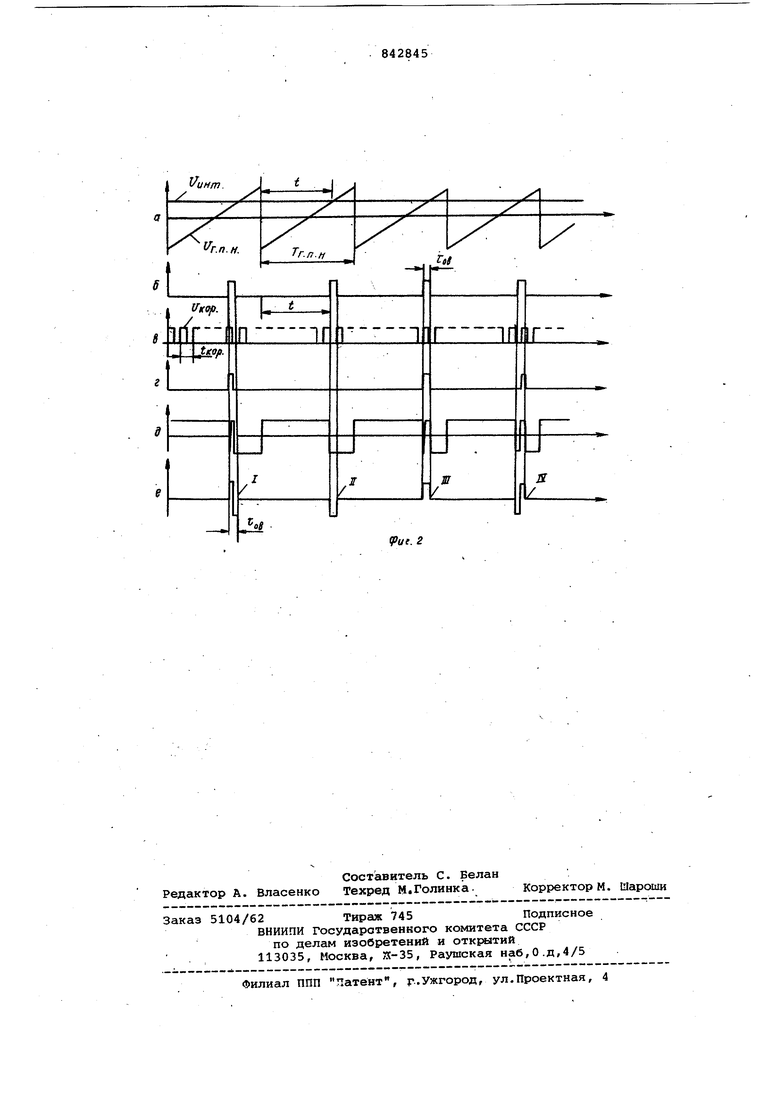

На фиг.1 приведен интегратор, структурная схема, на фиг.2 - временная диаграмма,, поясняющая его работу.

Интегратор с запоминанием (фиг.1 содержит операционный усилитель 1 с интегрирующим конденсатором 2 в цепи отрицательной обратной связи. На входе операционного усилителя 1 установлены коммутирующие элементы 3 и 4, к первому из которых подключен входной импеданс 5 (эта цепь может иметь несколько входов) а ко второму подсоединен выход ограничив элемента б цепи коррекции. Управляющий вход первого коммутирующего элемента 3 подключен к входу 7 управления режимом работы интегратора, а второго 4 - к выходу одновибратора 8, соединенному также с одним из входов элемента И 9, другой вход которого соединен с выходом генератора корректирующих импульсов 10. Вход ограничив вающего элемента 6 цепи коррекции и вход одновибратора 8 подключены к выходу компаратора 11, одий вход которого соединен с выходом интегратора, другой вход соединен с вы-, ходом генератора 12 пилообразного напряжения, а третий - с выходом элемента И 9. Вход блокировки одновибратора 8 соединен с входом 7 управления режимом раЬоты интегратора, а вход синхронизации генератора 12 пилообразного напряжения подключен к выходу генератора 10 корректи руюгдих импульсов.

Интегратор с запоминанием работает следующим образом.

В исходном положении, соответствующем режиму интегрирования входных сигналов, коммутирующий элемент 3 находится в замкнутом состоянии, а коммутирукхций элемент 4 - в разомкнутом, так как одновибратор 8 блокируется командным сигналом с входа 7 управления режимом работы интегратора. При этом устройство работает как обычный емкостный интегртор суммарного тока, поступающего на вход операционного силителя 1 через входной имп.еданс 5. Заметим, что при подключении одного из входов этой цепи к выходу операционного усилителя 1, устройство реализует функции инерционного звена. Такое включение применяется при использовании предлагаемого интегратора в функции аналогового запоминаюцего устройства и позволяет повысить его быстродействие в режиме записи входных сигналов.

При подаче команды с входа 7 на запоминание заинтегрированного (записанного) напряжения коммутиру ющий элемент 3 размыкается, а одновибратор 8 деблокируется и периодически замыкает коммутирующий элемент 4, обеспечивая прохождение на вход операционного усилителя 1 корректирующих импульсов из цепи коррекции, включающей элементы б, 8... 12. Формирование импульсов коррекции представлено на временной диаграмме (фиг.2).

Компаратор 11 сравнивает напряжение Upf, с выхода генератора пилообразного напрях ения 12 и выходное напрюкение интегратора и (фиг.2а). Последнее под действием дрейфовых токов на входе операционного усилителя 1 может изменяться в ту или иную сторону от запоминаемого уровня. При этом изменяется момент времени t (фиг.26) когда выполняется равенство и,-,, U, и компаратор 11 изменяет свое состояние, запуская одновибратор 8, который выдает импульс определенной длитель-ностиС -,(фиг2б) . Этот импульс замыкает коммутирующий элемент 4, сое ДИНЯЮ1ЧИЙ выход элемента 6 цепи коррекции со входом операционного усилителя 1, и одновременно разрешает проходить на выход элемента И 9 корректирующим импульсам от генератора 10 (фиг.2в) . Длительность импульса одновибратора выбрана равной или меньшей полупериода напряжения корректирующих импульсов с генератора 10 Ь2 )., Период напряжения генератора 12 синхронизирован импульсами с генератора .10, т.е. выполняется Т n. . где п - число ступенчатой коррекции, определя;ющих точность поддерживания запоминаемого напряжения (обычно п 250-500, что соответствует погрешности 0,2-0,1%). Поэтому при изменении момента t появления импульса одновибратора (фиг.26) изменяется его взаимное расположение относительно импульсов генератора 10 и на выходе элемента И 9 возможны четыре различных случая наложения импульсов одновибратора 8 и генератора 10, показанные на фиг.2г.

Импульсы с выхода элемента И 9 поступают на компаратор 11, например, на неинвертирующий вход его дифференциального усилителя с разнополярным выходом, на основе которого обычно выполняется компаратор, сравнивающий разнополярные входные сигналы. Таким образом, после изменения состояния компаратора в

момент t (фиг.2д) из + в - он может снова вернуться в предшествующее состояние по команде импульса с выхода элемента ,И 9. Различные случаи изменения напряжения на выходе компаратора на интервале V. показаны на фиг.2д, а форма импульсов коррекции на входе операционного усилителя 1 (т.е. импульсов тока с выхода компаратора 11 через элемент б и замкнутый ключ 4) по-.

казана на фиг.2е. Как видно в случаях I и IV результирующая коррекция близка к нулю, в случае II импульс корректирующего тока отрицательный, а в случае Ml - положительный. Точка равновесия в случае. I является неустойчиво, а в случае IV - устойчивой.

Таким образом, бласодаря включению на входе компаратора элемента И

Q определяющего изменение взаимного расположения импульсов одновибратора и генартора корректирующих импульсов, более эффектно используются функциональные и технические воз можности компаратора - он выполня5ет как функции элемента сравнения, так и формирователя импульсов коррекции требуёмой полярности без усложнения схемы и тьри снижении потребляемой общей энергии, так как

0 отбор мощности компаратора производится в очень короткие промежутки времени () . Отметим также, что импульсы на выходе одновибратора, генератора корректирующих импульсов

5 и элемента И являются однополярными что упрощает реализацию этих элементов в предлагаемом устройстве,, в частности, для этого могут быть использованы современные интегральQ ные микросхемы однополярной логики Блокировка одновибратора в режиме интегрирования входных сигналов устройства также позволяет упростить его, так как из схемы исключается один коммутирукядий элемент, ис пользовавшийся в известном устройстве.

Синхронизация генератора пилообразного напряжения от генератора корректирующих импульсов позволяет использовать эти генераторы как общие элементы для нескольких интеграторов С .запоминанием, что также упрощает их реализацию.

Предлагаемый интегратор с запоминанием используется в устройстве ввода данных анализаторов для обработки и запоминания хроматографических сигналов.

60

Формула изобретения

Интегратор с запоминанием, содержащий операционный усилитель, вход 65 которого через интегрирующий конденсатор подключен к его выходу, через последовательно соединенные первый коммутирующий элемент и вход ной импеданс соединен с входом интегратора и через последовательно соединенные второй коммутирующий элемент .и юграничиваквдий элемент подключен к выходу компаратора и входу одновибратора, управляющий вход первого коммутирующего элемента подключен к входу управления режимом работы интегратора, генератор пилообразного напряжения и генератор корректирующих -импульсов, о т личающийся тем, что,с целью упрсяцения интегратора и снижения потребляемой энергии, в него введен элемент И, причем выход одновибратора соединен с управляющим входом второго коммутирующего элемента и первым входом элемента И, второй вход которого подключен к выходу генератора корректирующих импульсов, выходы элемента И и генератора пилообразного напряжения .соединены соответственно с первым и вторым входами компаратора третий вход которого подключен к выходу операционного усилителя, вход блокировки одновибратора подключен к входу управления режимом работы интегратора, а к входу синхронизации генератора пилообразного напряжения подключен выход генератора корректирующих импульсов,

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР

5 № 424165, кл. G Об G 7/18, 1972.

2.Патент США № 3784919,

кл. G Об G 7/18, опублик. 1974.

3.Патент Великобритании №1274191 кл. G Об G 7/18, опублик. 1968 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1972 |

|

SU342296A1 |

| Измеритель нелинейности импульсовпилООбРАзНОгО НАпРяжЕНия | 1979 |

|

SU805207A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU868838A1 |

| Интегрирующий аналого-цифровой преобразователь | 1988 |

|

SU1681384A1 |

| Функциональный генератор | 1981 |

|

SU993287A1 |

| Противоблокировочная тормозная система автомобиля | 1990 |

|

SU1781107A1 |

| Интегратор с автокоррекциейКОэффициЕНТА пЕРЕдАчи | 1978 |

|

SU805346A1 |

| Устройство для управления регулируемым мостовым инвертором | 1988 |

|

SU1548830A1 |

| Устройство контроля пробивного напряжения МДП-структур | 1980 |

|

SU958986A1 |

| Функциональный преобразователь | 1985 |

|

SU1363185A1 |

Авторы

Даты

1981-06-30—Публикация

1979-07-16—Подача