(54) АНАЛОГО-ЦИФРОВОЙ ИНТЕГРАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой фильтр | 1980 |

|

SU873387A1 |

| Аналого-цифровой интегратор | 1982 |

|

SU1037280A1 |

| ДВУХФАЗНЫЙ ГЕНЕРАТОР ГАРМОНИЧЕСКИХ СИГНАЛОВ | 1990 |

|

RU2033684C1 |

| ЦИФРОВОЙ СЧЕТЧИК ЭЛЕКТРОЭНЕРГИИ КСР-ТИПА | 1991 |

|

RU2061243C1 |

| Интегрирующий аналого-цифровой преобразователь | 1988 |

|

SU1594695A1 |

| Режекторный фильтр | 1986 |

|

SU1417180A2 |

| Устройство для решения систем линейных алгебраических уравнений | 1984 |

|

SU1187157A1 |

| СИГМА-ДЕЛЬТА-АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1998 |

|

RU2145149C1 |

| Аналого-цифровое множительное устройство | 1983 |

|

SU1124346A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1336237A1 |

I

Изобретение относится к вычислительной технике и может быть использовано для точного интегрирования как быстроизменяющихся, так и медленноизменяющихся величин.

Известны интеграторы аналого-цифровые, сочетающие высокую точность с возможностью интегрировать функции как быстроизменяющиеся, так и медленноизменяющиеся, содержащие преобразователи цифровой информации в аналоговую, аналоговый интегратор и сумматор 1 и 2.

Наиболее близким по технической сущности к предлагаемому является аналогоцифровой интегратор, содержащий цифроаналоговый преобразователь (ЦАП) во входной цепи, последовательно соединенный с ним аналоговый интегратор (ИА), два компаратора К1 и К2, подключенных своими первыми входами к выходу ИА, выходы компараторов подключены ко входам счетчика-сумматора (Сч-См), выход которого является выходом всего устройства. На -второй вход компаратора К1 подано напряжение сравнения Uef , на второй вход компаратора К2 - напряжение Ue , полученное при помощи инвертора Ин. Для обнуления

интегратора ИА при срабатывании любого из компараторов служит сумматор См, входы которого подключены к выходам компараторов К1 и К2, а выход - к управляющему входу интегратора ИА 3.

В исходном состоянии на вход ЦАП поданы нули во всех разрядах. На точность интегрирования, помимо других факторов, влияют отличие от расчетных величин и временная и температурная нестабильность параметров аналоговой части схемы: постоянной времени аналогового интегратора, величин напряжений Ucp и Don- Если принять, что Уср и Uon высокостабильны и равны расчетным, то ощибка при интегрировании из-за указанных причин равна

-iV

ж„ t-л-х / -1

15

Ucp -ТТ

относительная ощибка определяется выражением

20

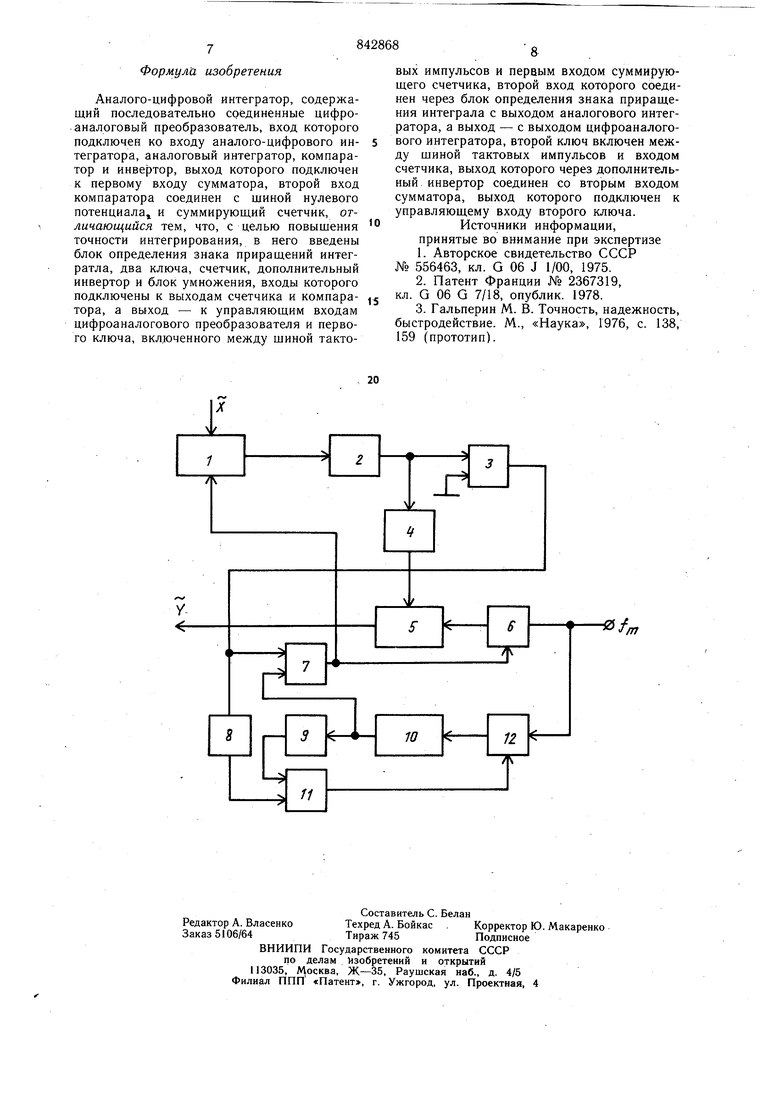

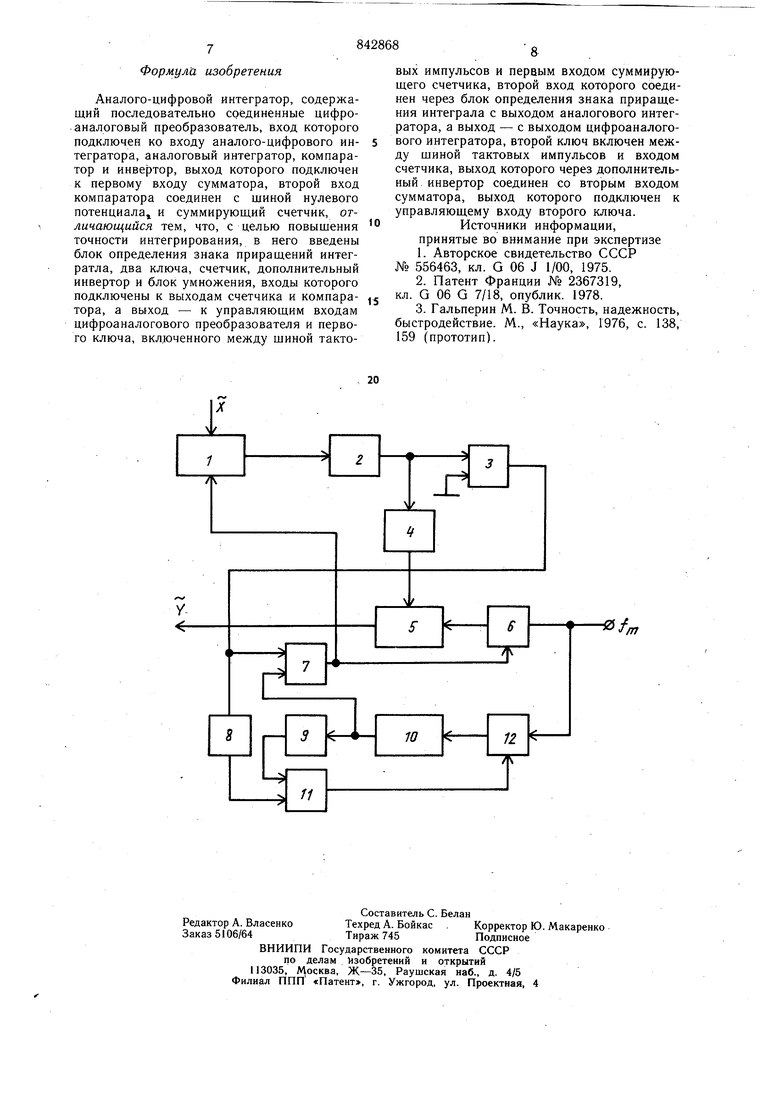

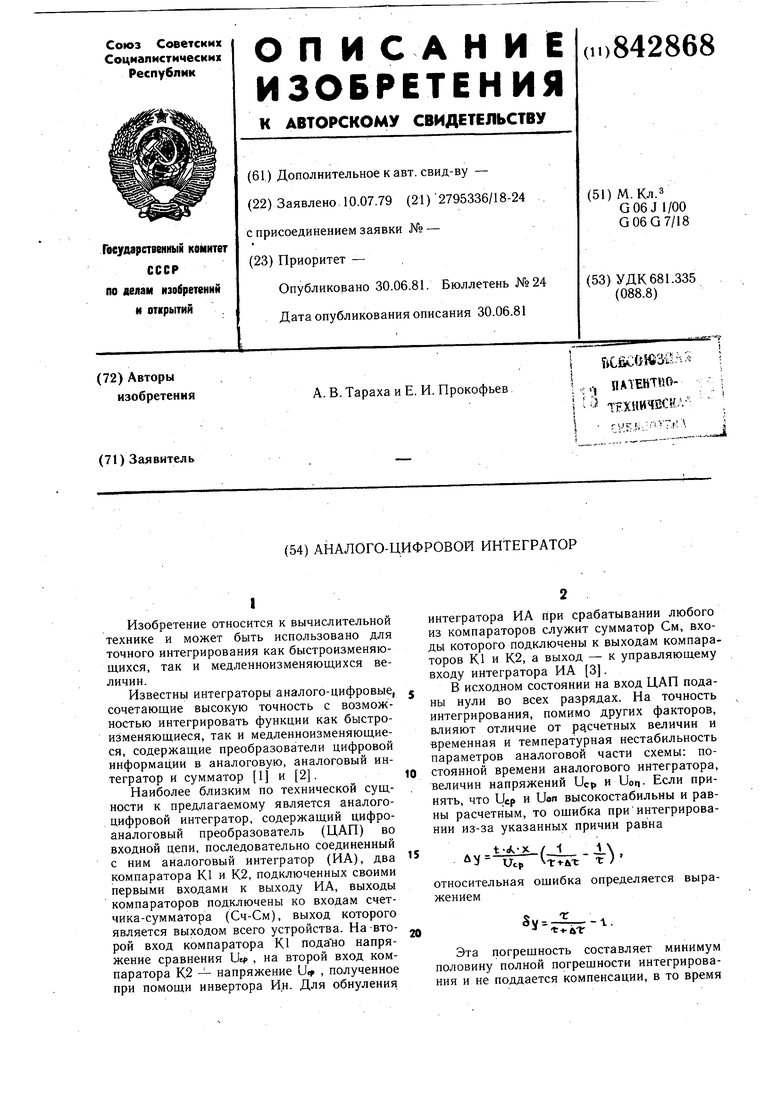

Эта погрещность составляет минимум половину полной погрещности интегрирования и не поддается компенсации, в то время как другие составляющие полной погрешности интегрирования можно хотя бы частично компенсировать. Точность такого интегратора невысока и составляет несколько десятых долей процента, что делает невозможным применение в нем многоразрядных (больше сети - восьми разрядов) кодов. Цель изобретения - повышение точности интегрирования аналого-цифрового интегратора. Поставленная цель достигается тем, что аналого-цифровой интегратор, содержащий последовательно соединенные цифроаналоговый преобразователь, вход которого подключен ко входу аналого-цифрового интегратора, аналоговый интегратор, компаратор и инвертор, выход которого подключен к первому входу сумматора, второй вход компаратора соединен с щиной нулевого потенциала, и суммирующий счетчик, введены блок определения знака приращений интеграла, два ключа, счетчик, дополнительный инвертор и перемножитель, входы которого подключены к выходам счетчика и компаратора, а выход - к управляющим входам цифроаналогового преобразователя и первого ключа, включенного между щиной тактовых импульсов и первым входом суммирующего счетчика, второй вход которого соединен через блок определения знака приращения интервала с выходом аналогового интегратора, а выход - с выходом цифроаналогового интегратора, второй ключ включен между шиной тактовых импульсов и входом счетчика, выход которого через дополнительный инвертор соединен со вторым входом сумматора, выход которого подключен к управляющему входу второго ключа. На чертеже представлена схема предлагаемого устройства (пример конкретного выполнения). Аналого-цифровой интегратор содержит ЦАП 1 со в.ходной цепи, выход которого соединен со входом аналогового интегратора 2, а выход интегратора 2 - с первым входом компаратора 3 и входом блока 4 определения знака приращений интеграла. Выход блока 4 соединен с управляющим входом суммирующего счетчика 5, выход суммирующего счетчика 5 является выходом всего устройства, а вход соединен через первый ключ 6 с щиной тактовых импульсов. Выход компаратора 3 подключен к первому входу блока 7 умножения и ко входу инвертора 8. Второй вход блока 7 умножения соединен со входом дополнительного инвертора 9 и выходом счетчика 10, а выход с управляющими входами первого ключа 6 и цифроаналогового преобразователя 1. Выходы инвертора 8 и инвертора 9 соединены со входами сумматора 11, а выход сумматора 11 - с управляющим входом второго ключа 12. Вход второго ключа 12 соединен с шиной тактовых импульсов, а выход - со входом счетчика 10. В исходном состоянии напряжение на выходе аналогового интегратора 2 равно нулю, на входы ЦАП 1 поданы нули во всех разрядах входного кода и напряжения на его выходе также равно нулю. Сигнал на выходе компаратора 3 - ноль, суммирующий счетчик 5 и счетчик 10 обнулены, поэтому сигнал на выходе блока 7 умножения «О, что соответствует такту «Интегрирование, при этом первый ключ б заперт, а цифроаналоговый преобразователь 1 преобразует в выходной сигнал входной код х. На выходах инвертора 8 и инвертора 9 - ригнал «1, на выходе сумматора 11 - также сигнал «1, вследствие чего второй люч 12 .открыт. Состояние выхода определителя 4 знака приращения интеграла на этом безразлично. В начальный момент на вход ЦАП 1 и на щину тактовых импульсов одновременно подаются код, не равный нулю, и последовательность тактовых импульсов от генератора. При этом на выходе ЦАП 1 появляется напряжение, определяемое следующим выражением -JJPn-K.-JC где и«- -напряжение внутреннего опорного источника напряжения цифроаналогового преобразователя 1; JC -текущее значение входного кода; . максимальное значение входного кода; К, - коэффициент передачи ЦАП 1 при X Хям Введем обозначение Напряжение на выходе аналогового интегратора 2 изменяется по следующему закону11,-1 fU;dt -:ll7,t, - постоянная времени аналогового интегратора 2. Когда выходное напряжение интегратора 2 превыщает порог срабатывания компаратора 3, на выходе компаратора 3 действует сигнал «1, сигнал на выходе инвертора 8 равен нулю. Счетчик 10 через открытый второй ключ 12 заполняется тактовыми импульсами, следующими с периодом Т. Когда счетчик 10 заполнен, на его выходе появляется сигнал «1. а на выходе инвертора 9 сигнал- «0. Таким образом, на обоих входах сумматора 11 - нули, состояние его выхода - также нулевое. Второй ключ 12 заперт. На оба входа блока умножения 7 подаются «единицы - с выхода коммпаратора 3 и с выхода счетчика 10, на выходе которого также появляется сигнал «1, который открывает первый ключ 6 и переводит ЦАП 1 в состояние, когда на его выходе действует напряжение, соответствующее х... IT /f № Q - IT-и, -cfx,., Знак и, противоположен U, на такте интегрирования. Такт интегрирования закончен, начался второй такт - считывание. К моменту начала считывания напряжение на выходе интегратора 2 равно J2a. - 4 и. t«. , где ty-время интегрирования. Учитывая, что , а время интегрирования определяется выражением (),(2) где m - разрядность счетчика 10, перепишем (1) в виде иг.(2 -1) Во время такта считывания напряжение на выходе интегратора 2 изменяется по закону , u- -u-«- 47b;c(t )) И в определенный момент времени становится равным нулю. В этот момент сигнал на выходе компаратора 3 изменяется на «О, что вызывает через блок 7 умножения запирание первого ключа б и переключение цифроаналогового преобразователя 1 в такое состояние, когда напряжение на его выходе определяется текущим значением входного кода X. Этот же сигнал через инвертор 8 и сумматор 11 вызывает отпирание второго ключа 12, через который тактовые импульсы поступают на вход счетчика 10. На этом заканчивается такт считывания и начинается второй такт интегрирования. Длительность такта считывания определяется из выражения (3) при Uj О t,,.i:nK: () ЗСмАКС Во время такта интегрирования через открытый первый ключ б на вход суммирующего счетчика 5 поступают тактовые импульсы, которые заполняют его. Их поступаетt, t,, Это число равно приращению интеграла М AY С учетом (4( получаем выражение ,у.)(5) tnaice В результате суммирования приращений AY, определяемых выражением (5), получается полное значение интеграла за время t Nt. Как известно, приближенное значение интеграла функции определяется следующим образом V-IWii Y .SXiAU AU2:xi., iz.0 гдeXi-значение подынтегральной функции в начале или в конце участка AU; А и - приращение аргумента: , что А и const на всем интервале интегрирования. Принято также, что начальное значение интеграла Y равно нулю. Каждое произведение х1Л U является приращением интеграла функции х на i-ом интервале интегрирования .AYi XiAU В предлагаемом устройстве значение подынтегральной функции xi в начале каждого интервала интегрирования подается в виде двоичного кода х на вход цифроаналогового интегратора. Как видно из последнего выражения, число импульсов, поступающих на вход суммирующего счетчика 5, а фактически это величина, равная приращению интеграла, зависит только от текущего значения входного кода X и не зависит от точности и стабильности параметров элементов, входящих в состав цифроаналогового преобразователя 1 и аналогового интегратора 2. Эквивалентная постоянная времени т аналого-цифрового интегратора находится из выражения (5) при условии Y х(х const) т, cit Y x , 1 . но аТ() Г, таким образом, Тэ Тх Пос тоянная времени аналого-цифрового интегратора также не зависит от параметров элементов аналоговой части устройства. В счетчике-сумматоре 5 накапливается число рРЧ , WH У .IX, --О При сравнении (6) и (7) видно, что число ( 1)/х представляет собой приращение аргумента подынтегральной функции Л I I - - аи - Из выражения (7) следует, что на точность интегрирования не влияют значения какихлибо параметров аналоговой части схемы, а следовательно, и их временные и температурные изменения. Как видно из вышеизложенного, в предлагаемом устройстве эта составляющая ощибки отсутст,вует, что обуславливает точность интегрирования по крайней мере вдвое выше, чем в известном устройстве.

Формула изобретения

Аналого-цифровой интегратор, содержащий последовательно соединенные цифроаналоговый преобразователь, вход которого подключен ко входу аналого-цифрового интегратора, аналоговый интегратор, компаратор и инвертор, выход которого подключен к первому входу сумматора, второй вход компаратора соединен с шиной нулевого потенциала и суммирующий счетчик, отличающийся тем, что, с целью повыщения точности интегрирования, в него введены блок определения знака приращений интегратла, два ключа, счетчик, дополнительный инвертор и блок умножения, входы которого подключены к выходам счетчика и компаратора, а выход - к управляющим входам цифроаналогового преобразователя и первого ключа, включенного между щиной тактовых импульсов и первым входом суммирующего счетчика, второй вход которого соединен через блок определения знака приращения интеграла с выходом аналогового интегратора, а выход - с выходом цифроаналогового интегратора, второй ключ включен между шиной тактовых импульсов и входом счетчика, выход которого через дополнительный инвертор соединен со вторым входом сумматора, выход которого подключен к управляющему входу второго ключа.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1981-06-30—Публикация

1979-07-10—Подача