О-4

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Режекторный фильтр | 1987 |

|

SU1429293A2 |

| УСТРОЙСТВО ЦИФРОВОЙ КОГЕРЕНТНОЙ ОБРАБОТКИ СИГНАЛОВ | 1990 |

|

SU1818989A1 |

| Устройство для подавления помех | 1983 |

|

SU1095419A1 |

| УСТРОЙСТВО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 1992 |

|

RU2042269C1 |

| Цифровой режекторный фильтр | 1988 |

|

SU1608786A1 |

| Устройство для приема сигналов с частотно-фазовой модуляцией | 1989 |

|

SU1600000A1 |

| АВТОМАТИЗИРОВАННОЕ УСТРОЙСТВО ПОВЫШЕНИЯ КАЧЕСТВА КАНАЛА ПЕРЕДАЧИ ДАННЫХ | 2014 |

|

RU2603493C2 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| Синхронный режекторный фильтр | 1987 |

|

SU1427562A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин с мультипликативной автокоррекцией | 1984 |

|

SU1185604A1 |

Изобретение откосится к радиотехнике. Цель изобретения - повышение точности фильтрации при одновременном упрощении. Режекторный фильтр содержит вычитающий усилитель 1,ключи 2 и 3, интеграторы 4 и 5, комм:- татор 6, АЦП 7, сумматор 8, блок памяти (БП) 9, регистр 10, ДАЛ И, фильтр 12 нижних частот, блок управления 13, г-р 14 тактовых импульсов и инверторы 15 и 16. Цель достигается путем уменьшения объема памяти БП 9 с помощью введенных инверторов . 15 и 16. 2 ил.

ГЧ)

Изобретение относится к радиотехнике и может быть использовано для подавления узкополосной гармонической помехи в информационном сигнале и является дополнительным к авт.- св. № 1187242.

Цель изобретения - повышение точности фильтрации при о новременном упрощении путем уменьшения объема памяти блока.памяти.

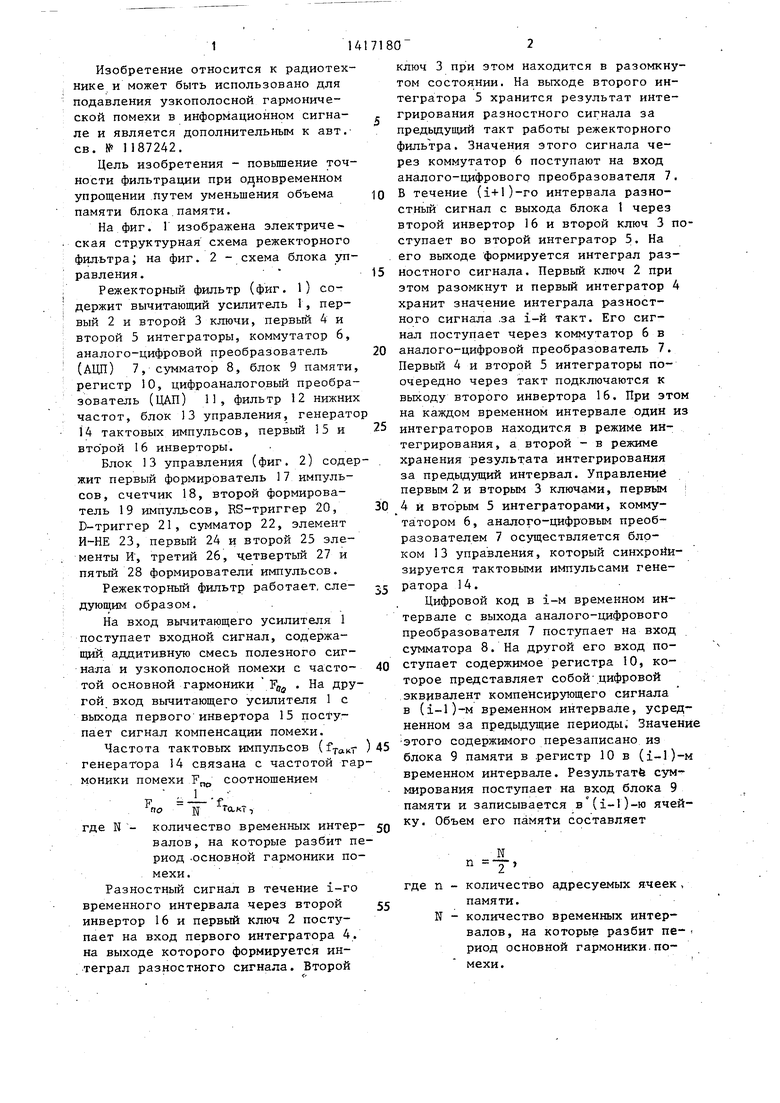

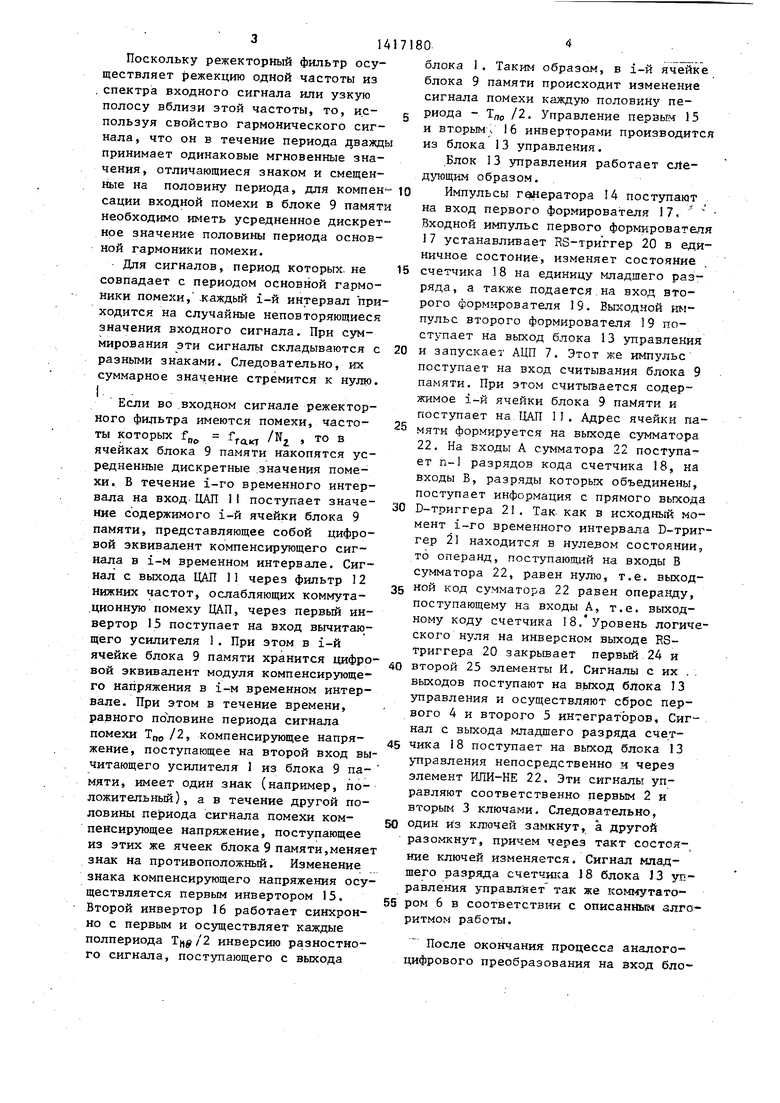

На фиг. Г изображена электрическая структурная схема режекторного фильтра; на фиг. 2 - схема блока управления.

Режекторный фильтр (фиг. 1) содержит вычитающий усилитель 1, первый 2 и второй 3 ключи, первый 4 и второй 5 интеграторы, коммутатор 6, аналого-цифровой преобразователь (АЦП) 7, сумматор 8, блок 9 памяти регистр 10, цифроаналоговый преобразователь (ЦАП) 11, фильтр 12 нижних частот, блок 13 управления, генерато 14 тактовых импульсов, первьй 15 и вто рой 16 инверторы.

Блок 13 управления (фиг. 2) содержит первый формирователь 17 импульсов, счетчик 18, второй формирователь 19 импульсов, RS-триггер 20, D-триггер 21, сумматор 22, элемент И-НЕ 23, первый 24 и второй 25 элементы И, третий 26, четвертьй 27 и пятый 28 формирователи импульсов.

Режекторный фильтр работает, следующим образом.

На вход вычитающего усилителя 1 поступает входной сигнал, содержащий аддитивную смесь полезного сигнала и узкополосной помехи с частотой основной гармоники Fj . На другой вход вычитающего усилителя 1 с выхода первого инвертора 15 поступает сигнал компенсации помехи.

Частота тактовых импульсов (Гт-акТ генератора 14 связана с частотой гамоники помехи Fj соотношением

f.

р :--L . по и ,

где N - количество временных интервалов, на которые разбит приод .основной гармоники по . мехи.

Разностный сигнал в течение i-ro временного интервала через второй инвертор 16 и первый ключ 2 поступает на вход первого интегратора 4. на выходе которого формируется интеграл разностного сигнала. Второй

, хор

р) ре-

71802

ключ 3 при этом находится в разомкнутом состоянии. На выходе второго интегратора 5 хранится результат инте, грирования разностного сигнала за предыдущий такт работы режекторного фильтра. Значения этого сигнала через коммутатор 6 поступают на вход аналого-цифрового преобразователя 7.

10 В течение (i+l)-ro интервала разностный сигнал с выхода блока 1 через второй инвертор 16 и второй ключ 3 поступает во второй интегратор 5. На его выходе формируется интеграл раз15 ностного сигнала. Первый ключ 2 при этом разомкнут и первый интегратор 4 хранит значение интеграла разностного сигнала .за i-й такт. Его сигнал поступает через коммутатор 6 в

20 аналого-цифровой преобразователь 7. Первый 4 и второй 5 интеграторы поочередно через такт подк.х1ючаются к выходу второго инвертора 16. При этом на каждом временном интервале один из

25 интеграторов находится в режиме интегрирования, а второй - в режиме хранения результата интегрирования за предьщущий интервал. Управление первым 2 и вторым 3 ключами, первым i

30 4 и вторым 5 интеграторами, коммутатором 6, аналого-цифровым преобразователем 7 осуществляется блоком 13 управления, который синхройи- зируется тактовыми импульсами гене25 ратора 14.

Цифровой код в i-M временном интервале с выхода аналого-цифрового преобразователя 7 поступает на вход сумматора 8. На другой его вход по40 ступает содержимое регистра 10, которое представляет собой-.цифровой эквивалент компенсирующего сигнала в (i-l)-M временном интервале, усредненном за предыдущие периоды Значение

дс ЭТОГО содержимого перезаписано из

блока 9 памяти в .регистр 10 в (1-1 )-м временном интервале. Результате суммирования поступает на вход блока 9 памяти и записывается в°(1-1)-ю ячейку. Объем его памяти составляет

50

п

JL

2

где п - количество адресуемых ячеек ,

памяти.

N - количество временных интервалов, на которые разбит период основной гармоники.помехи.

3141

Поскольку режекторный фильтр осуществляет режекцига одной частоты из спектра входного сигнала или узкую полосу вблизи этой частоты, то, используя свойство гармонического сигнала, что он в течение периода дважды принимает одинаковые мгновенные значения, отличающиеся знаком и смещенные на половину перно/ а, для компен сации входной помехи в блоке 9 памяти необходимо иметь усредненное дискретное значение половины периода основной гармоники помехи.

Для сигналов, период которых, не совпадает с периодом основной гармоники помехи, .каждый 1-й интервал приходится на случайные неповторяющиеся значения входного сигнала. При суммирования эти сигналы складываются с разньши знаками. Следовательно, их суммарное значение стремится к нулк1.

Если во .входном сигнале режектор- ного фильтра имеются помехи, часто ты которых fpj, f /Nj , то в ячейках блока 9 памяти накопятся усредненные дискретные .значения помехи. В течение i-го временного интервала на вход ЦАП 1I поступает значение содержимого i-й ячейки блока 9 памяти, представляющее собой цифровой эквивалент компенсирующего сигнала в i-M временном интервале. Сигнал с выхода ЦАП 11 через фильтр 12 нижних частот, ослабляющих коммута- .ционную помеху ЦАП, через первый инвертор 15 поступает на вход вычитающего усилителя I. При этом в i-й ячейке блока 9 памяти хранится цифровой эквивалент модуля компенсирующего напряжения в i-м временном интервале. При этом в течение времени, равного по ловине периода сигнала помехи Т /2, компенсирующее напряжение, поступающее на второй вход вычитающего усилителя 1 из блока 9 памяти, имеет один знак (например, положительный), а в течение другой половины периода сигнала помехи компенсирующее напряжение, поступающее из этих же ячеек блока 9 памяти,меняе знак на противоположный. Изменение знака компенсирующего напряжения осуществляется первым инвертором 15. Второй инвертор 16 работает синхронно с первым и осздцествляет каждые полпериода инверсию разностного сигнала, поступающего с выхода

0

блока 1. Таким образам, в i-й ячейке блока 9 памяти происходит изменение сигнала помехи каждую половину периода - Т„о /2, Управление первым 15 и втхэрымч 16 инверторами производится из блока 13 управления.

Блок 13 управления работает сле- д тощим образом.

Импульсы генератора 14 поступают на вход первого формирователя 17, - .Входной импульс первого формирователя 17 устанавливает RS-триггер 20 в единичное состоние, изменяет состояние

счетчика 18 на единицу младшего разряда, а также подается.на вход второго формирователя 19. Выходной км- пульс второго формирователя 19 поступает на выход блока 13 управления

и запускает АЦП 7. Этот же импульс поступает на вход считывания блока 9 памяти. При этом считывается содержимое i-й ячейки блока 9 памяти и поступает на ЦАП П. Адрес ячейки памяти формируется на выходе сумматора 22. На входы А сумматора 22 поступает п-1 разрядов кода счетчика 18, на входы Б, разряды которых объединены, поступает информация с прямого выхода

D-триггера 21, Так. как в исходный момент i-ro временного интервала D-триг- гер 21 находится в нулевом состоянии, то операнд, поступающий на входы В сумматора 22, равен нулю, т.е. выходной код сумматора 22 равен операнду, поступающему на входы А, т.е. выходному коду счетчнка 18. Уровень логического нуля на инверсном выходе RS- триггера 20 закрьгоает первый 24 и

второй 25 элементы И. Сигна.пьз с их . . выходов поступают на выход блока 13 управления и осуществляют сброс первого 4 и второго 5 интеграторов. Сигнал с выхода младшего разряда счетчика 18 поступает на выход блока 13 управления непосредственно .ч через элемент ИЛИ-НЕ 22. Эти сигналы управляют соответственно первым 2 и вторым 3 ключами. Следовательно,

один из ключей замкнут, а другой

разомкнут, причем через такт состояние ключей изменяется. Сигнал младшего разряда счетчшса 18 блока 13 управления управляет так же комнутато-

ром 6 в соответствии с описанньгм алгоритмом работы.

После окончания процесса аналого- гшфрового преобразования на вход бло

5

ка 13 управления поступает сигнал окончания преобразования. Этот сигнал устанавливает RS-триггер 20 в нулевое состояние, а D-триггер 21 - в единичное. Уровень единицы на инверсном выходе RS-триггера 20 разрешает работу первого 24 и второго 25. элементов И. Если, например, на 1-м такте младший разряд счетчика 18 равен единице, то на выходе первого элемента И 24 формируется сигнал сбрса второго интегратора 5. Первый интегратор 4 при этом находится в режиме интегрирования, поскольку на вход управления первого ключа 2 с выхода блока 13 управления поступает разрешающий сигнал.

Уровень логической единицы с прямого выхода D-триггера 21 поступает на входы В сумматора 22 и на вход третьего формирователя 26. Наличие на всех разрядах входов В уровня логической единицы соответствует значению В, равному минус единице, представленному в дополнительном коде. Таким образом, на выходах блока 13 управления формируется адрес предыдущей (1-1)-й ячейки блока 9 памяти. Положительньй фронт импульса на прямом выходе D-триггера 21 запускает последовательно вклю-. ченные.третий 26, четвертьй 27 и пятый 28 формирователи. Выходной сигнал четвертого формирователя 27 с выхода блока 13 управления поступает на вход записи блока 9 памяти. При этом в (i-1)-ю ячейку блока 9 памяти записывается выходной результат сумматора 22. Выходной сигнал пятого формирователя 28 поступает на управляющий вход регистра 10. В результате этого в регистр 10 переписывается содержимое блока 9i памяти Одновременно выходной сигнал пятого формирователя 28 сбрасывает D-триг- гер 21 в нулевое состояние. Старший разряд счетчика 18 с выхода блока 1 управления поступает на управляющие входы первого 15 и второго 16 инверторов. Половину периода сигнала помехи Tf,o/2 первый 15 и второй 16 инверторы передают поступающие на их входы сигналы без изменений, а половину периода осуществляют инверсию . .поступающих на их входы сигналов. При поступлении на вход блока 13 уп

806

равления .следующего тактового импульса описанные процессы повторяются,.

Для обеспечения нормального функционирования режекторного фильтра необходимо, чтобы сигнал запрета на пер-, вый -24 и второй 25 элементы И поступил до того, как младший разряд счетчика 18 изменит свое состояние. Для этого на выходе первого формировате- теля 17 формируется отрицательный иМ- пульс. По переднему фронту этого импульса RS-триггер 20 устанавливается в единичное состояние, а счетчик 18 изменяет свое состояние по его заднему фронту. Длительность импульса выбирается исходя из максимального времени распространения сигнала от,выхода первого формирователя 17 до выхода первого 24 и второго 25 элементов И. Длительность импульса на выходе BTciporo формирователя 19 должна обеспечить необходимую задержку сигнала считывания по отношению к выбору адреса блока 9 памяти.

Длительность импульса на выходе третьего формирователя 26 должна обеспечить задержку сигнала записи по отношению к сигналу выбора адреса записи блока 9 памяти. Длительность импульса четвертого формирователя 27 определяется исходя из необходимой длительности импульса записи блока 9 памяти. Длительность импульса третьего формирователя 26 определяется временем задержки изменения адреса записи после окончания сигнала записи..

Формула изобретения

Бежекторный фипьтр по авт. ев № Г187242«,о тличающийся . тем, что, с целью повьппения точности фильтрации при одновременном.упрощении путем уменьшения объема памяти блока памяти, дополнительно введены первый инвертор, включенный между выходом фильтра нижних частот и первым входом вычитающего усилителя, и второй инвертор, включенный между выходом вычитающего усилителя и объединенными информационными входами первого и второго ключей, при этом управляющие входы первого и второго инверторов объединены и соединены с дополнительным: выходом блока управления .

Фиг. 2

| Авторское свидетельство СССР № 1187242, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-08-15—Публикация

1986-08-11—Подача