(54) СИНХРОННЫЙ D-ТРИГГЕР

| название | год | авторы | номер документа |

|---|---|---|---|

| Универсальный DV(Т)-триггер | 1987 |

|

SU1552358A1 |

| САМОСИНХРОННЫЙ ОДНОКРАТНЫЙ D-ТРИГГЕР С ВЫСОКИМ АКТИВНЫМ УРОВНЕМ СИГНАЛА УПРАВЛЕНИЯ | 2007 |

|

RU2362266C1 |

| САМОСИНХРОННЫЙ RS-ТРИГГЕР С ПОВЫШЕННОЙ ПОМЕХОУСТОЙЧИВОСТЬЮ (ВАРИАНТЫ) | 2009 |

|

RU2427955C2 |

| САМОСИНХРОННЫЙ ДИНАМИЧЕСКИЙ ДВУХТАКТНЫЙ D-ТРИГГЕР С НУЛЕВЫМ СПЕЙСЕРОМ | 2018 |

|

RU2693321C1 |

| САМОСИНХРОННЫЙ ОДНОТАКТНЫЙ D-ТРИГГЕР С НИЗКИМ АКТИВНЫМ УРОВНЕМ СИГНАЛА УПРАВЛЕНИЯ | 2007 |

|

RU2362267C1 |

| САМОСИНХРОННЫЙ ТРИГГЕР С ОДНОФАЗНЫМ ИНФОРМАЦИОННЫМ ВХОДОМ | 2008 |

|

RU2405246C2 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 1997 |

|

RU2123233C1 |

| САМОСИНХРОННЫЙ ДИНАМИЧЕСКИЙ ДВУХТАКТНЫЙ D-ТРИГГЕР С ЕДИНИЧНЫМ СПЕЙСЕРОМ | 2018 |

|

RU2693319C1 |

| Многофункциональный тактируемый триггер с управлением по срезу тактового сигнала | 1986 |

|

SU1359885A1 |

| Устройство для сопряжения процессора с памятью | 1987 |

|

SU1481779A1 |

.. .

Изобретение относится к автоматике и вычислительной технике и предназначно для использования в быстродействукяцих цифровых микросхемах.

В 1Ц1фровой технике широко используются Синхронные)-триггеры, построе нные на логических элементах Й-НЕ, ЙЛИ-НЕ. Эти триггеры содержат две бистабильные ячейки. Под действием синхрос1«7напа информация из первой бистабильиой ячейки передается во вторую, выходы которой служат выходами триггеров Dj.

Недостатком этих триггеров является большая потребляемая мощность, значительная площадь, занимаемая, на .кристалле при изготовлении в интегралных микросхемах, а также низкое быстродействие.

Наиболее близким техническим решением к предлагаемому является схема синхронного О-триггёра, состоящая из. (вух бистабильных ячеек (БЯ),выходной и управляющей, калэдая из которых

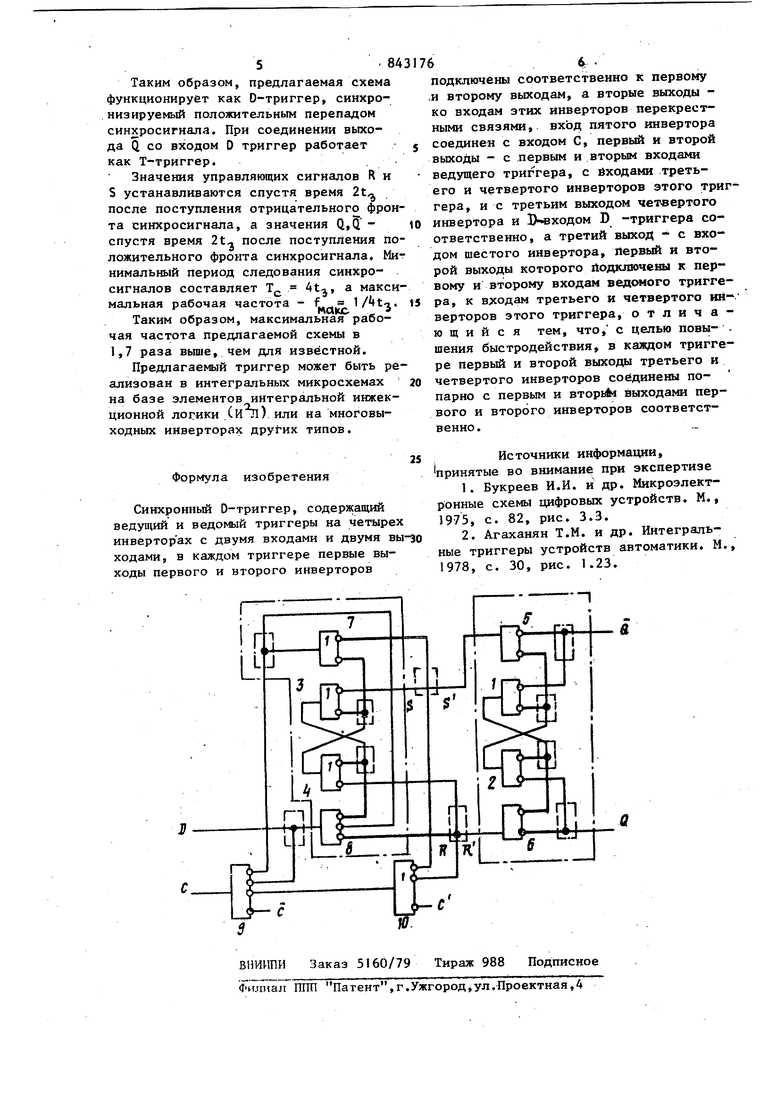

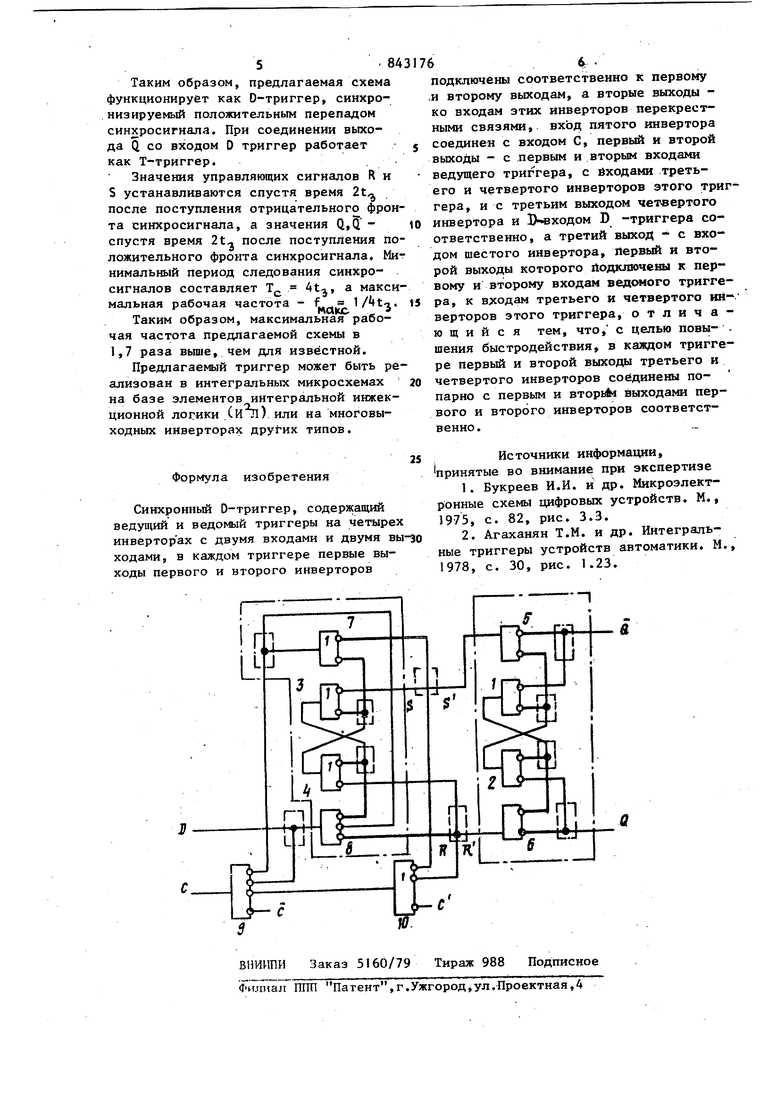

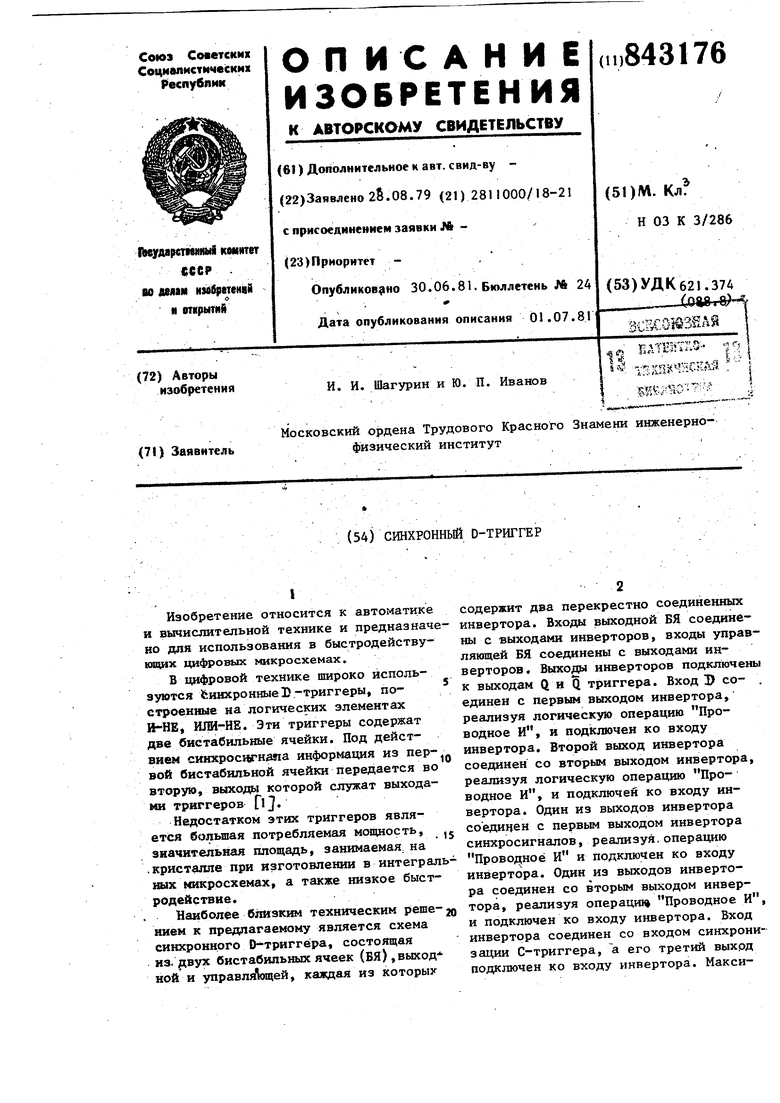

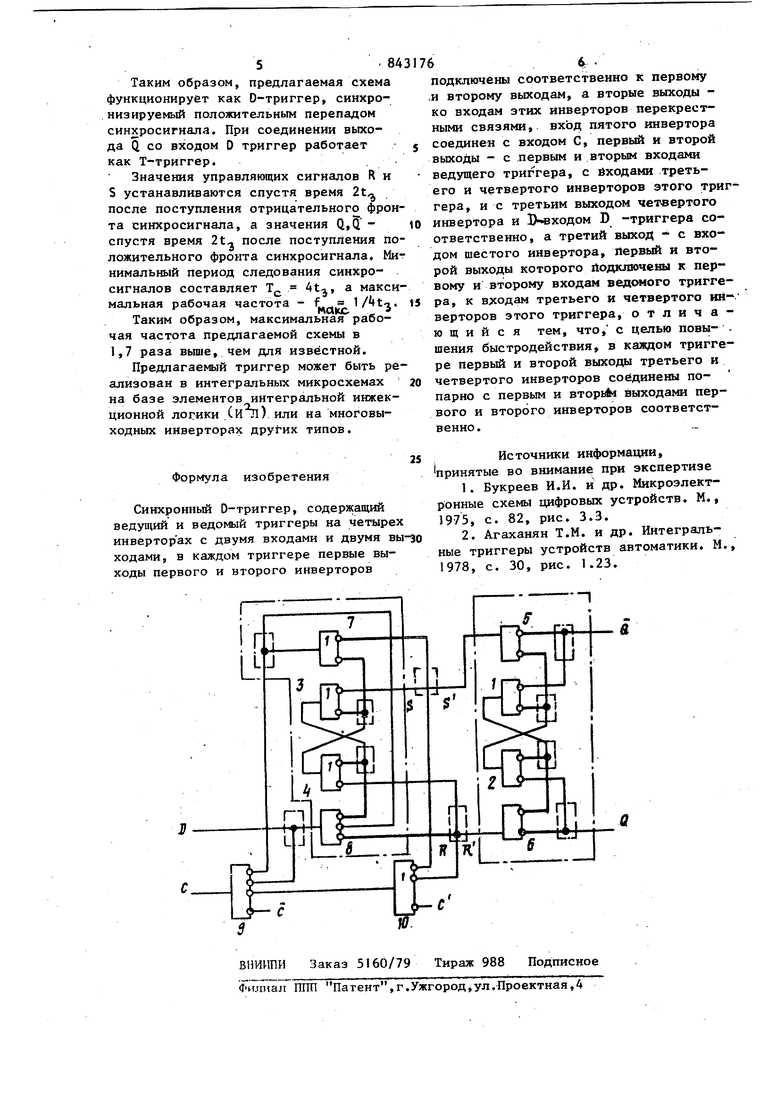

содержит два перекрестно соединенных инвертора. Входы выходной БЯ соединены с выходами инверторов, входы управляющей БЯ соединены с выходами инверторов. Выхода инверторов подключены к выходам Q и Q триггера. Вход 3) со- . единен с первьм выходом инвертора, реализуя логическую операцию Проводное И , и подключен ко входу инвертора. Второй выход инвертора соединен со вторым выходом инвертора, реализуя логическую операцию Проводное И, и подключен ко входу инвертора. Один из выходов инвертора соединен с первым выходом инвертора синхросигналов, реализуя.операцию Проводное И и подключен ко входу инвертора. Один из выходов инвертора соединен со вторым выходом инвертора, реализуя операци Проводное И, и подключен ко входу инвертора. Вход инвертора соединен со входом синхронизации С-триггера, а его третий выхрд подключен ко входу инвертора. Макси. 3 мальная рабочая частота триггера trt 1/7t, где t,,-- задержка инверriMPsc f.i тора L2J. Недостаткам данного триггера является малое быстродействие. Цель изобретения - повышение быст родействия триггера. . Указанная цель достигается тем, что в синхронный 1 -триггер на инверторах, содержащий ведущий и ведомый триггеры с двумя входами и двумя выходами, в каждом триггере первые выходы первого и второго инверторов подключены соответственно к первому |и второму выходам, а вторые выходы входам этих инверторов перекрест.ными связями, вход пятого инвертора соединен с .входом С, первый и второй выходы - Спервым и вторым входами ведущего триггера, с входами третьег и четвертого инвертора этого триггер и с третьим выходом четвертого инвер тора и и-входом)-триггера, соответс венно , а третий выход - с входом шес того инвертора,первый и второй выход которого подключены к первому и втор му входам ведомого триггера, к входа третьего и четвертого инверторов это триггера,в каждом триггере первый и второй выходы третьего и четвертого инверторов соединены попарно с первы и вторым выходами первого и второго инверторов соответственно. Схема.синхронного)-триггера приведена на чертеже. Триггер содержит мно бвыходные ин верторы с 1-10. Выходы О. и О. триггер подключены соответственно к первым выходам инверторов 1, 5,2 и 6, соединенных для.реализации операции Проводное и. Вторые выходы инверто ров 1 и .5, 2 и 6 соединены между собой, реализуя операции Проводное И и подключены соответственно ко входа инверторов 2 и 1. Первые выходы инверторов 3, 7, 10 соединены между Собой, реализуя операцию Проводное и и подключены ко входу инверто ра 5. Первые выходы инверторов 4, 8 и второй выход инвертора 10 аналогич ным образом подключены ко входу инвертора 6. Вторые выходы инверторов и 7, 4 и 8 соединены между собой, ре ализуя операции Проводное И, и под ключены ко входам 4 и 3 инверторов с ответственно. D -триггер работает следующий образом. 64, ЕслиБг, то при поступлении на вход С отрицательного фронта синхросигнала переключаются инверторы 9 и 10 в состояние С 1, с 0. На вход инвертора 8 поступает логическая I, которая устанавливает его в состояние 0. Сигнал с 0 устанавливает инверторы 5 и 6 в состояние I, так что они не оказывают влияние на состояние выходов. Q и Q триггера. Инверторы 3.. и 7, на входы которых поступает логический О, устанавливаются в состояние 1, что приводит к установке инвертора 4 в состояние О, При этом установление управляющих сигналов R, S, выходной БЯ осуществляется за время 2tg.. При поступлении на вход С положительного фронта Синхросигнала переключается инвертор 9, на выходах которого устанавливается си1- нал С О, который переключает инверторы 8 и 10 в состояние I. Состояние инверторов 3, 4 и 7 при этом не меняется. Так как сигнал С 1, то на входы инверторов 5 и (; поступают управляющие сигналы S 1,R 0. Инверторы 5 и 6 устанавливаются в состояние О и 1. соответственно, формируя на выходе триггера сигнал Q 0. Инвертор 2, на вход которого поступает логический О, переходит в состояние 1, при этом на выходе триггера устанавливается сигнал Q I, и переводит инвертор 1.в состояние 0. Состояние выходов триггера окончательно устанавливается за время 2 t после установки С 1. Если , то при поступлении сигнала С О инверторы 9 и 10 устанавливаются в состояние 1 и О соответственно. Инвертор 8 устанавливается в состояние 1, что приводит к установке инвертора 7 в состояние О, а инверторов 4 и 3 соответственно в состояние 1 и 0. Состояние выходов Q и Q триггера при этом не изменяется. При поступлении сигнала С 1 инверторы 9 и 10 устанавливаются в состояние С 0 С 1.. Инвертор 8 сохраняет состояние 1. На входы инверторов 5 и 6 поступают сигналы ОиК RC 1, которые устанавливают инверторы 5 и 6 в состояния 1 и О соответственно, при этом ij 0. Инвертор 1, на вход которого поступает логический О, переключается в состояние 1 , при этом Q 1 , а -затем инвертор 2 переходит в состояние 0.

Авторы

Даты

1981-06-30—Публикация

1979-08-28—Подача