Изобретение относится к вычислительной технике и может быть использовано при построении ЭВМ с магистральной структурой межмодульных связей.

Целью изобретения является повышение производительности устройства.

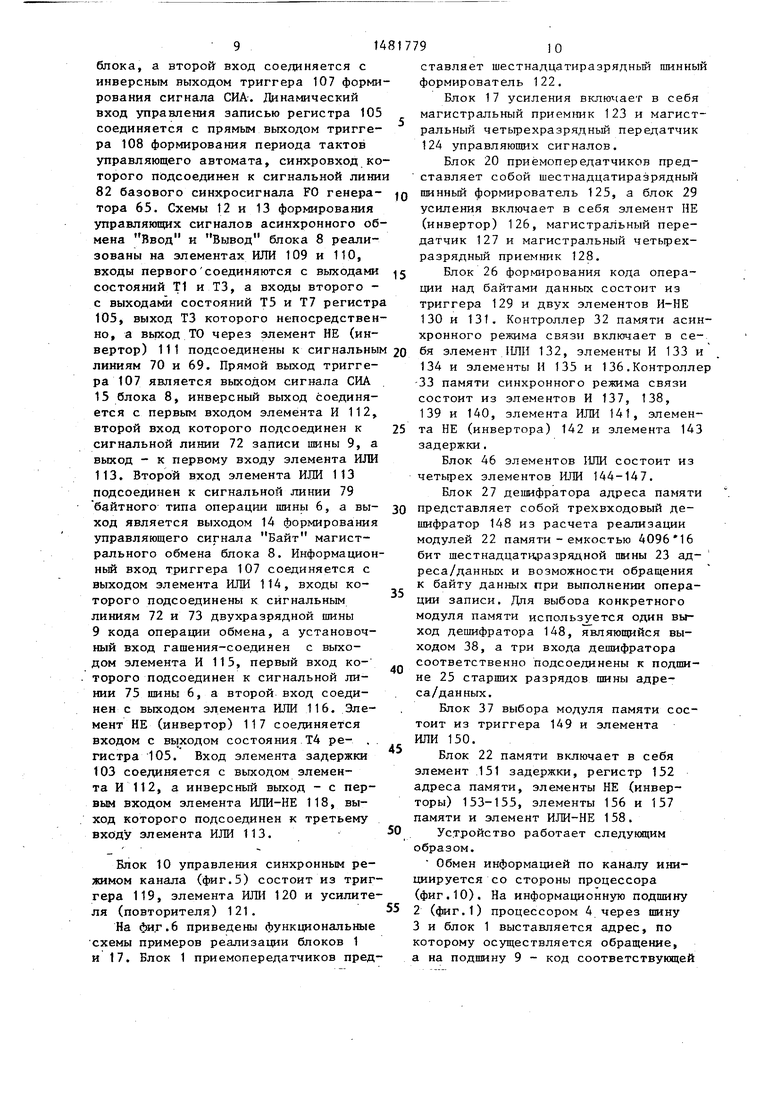

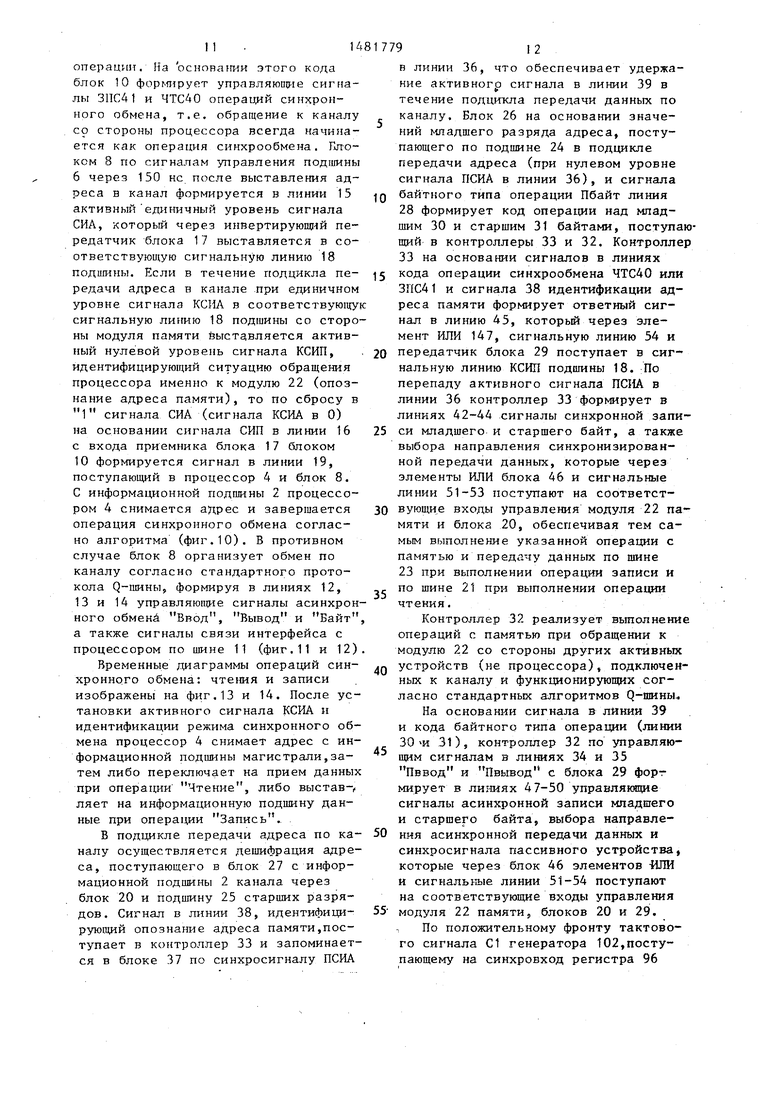

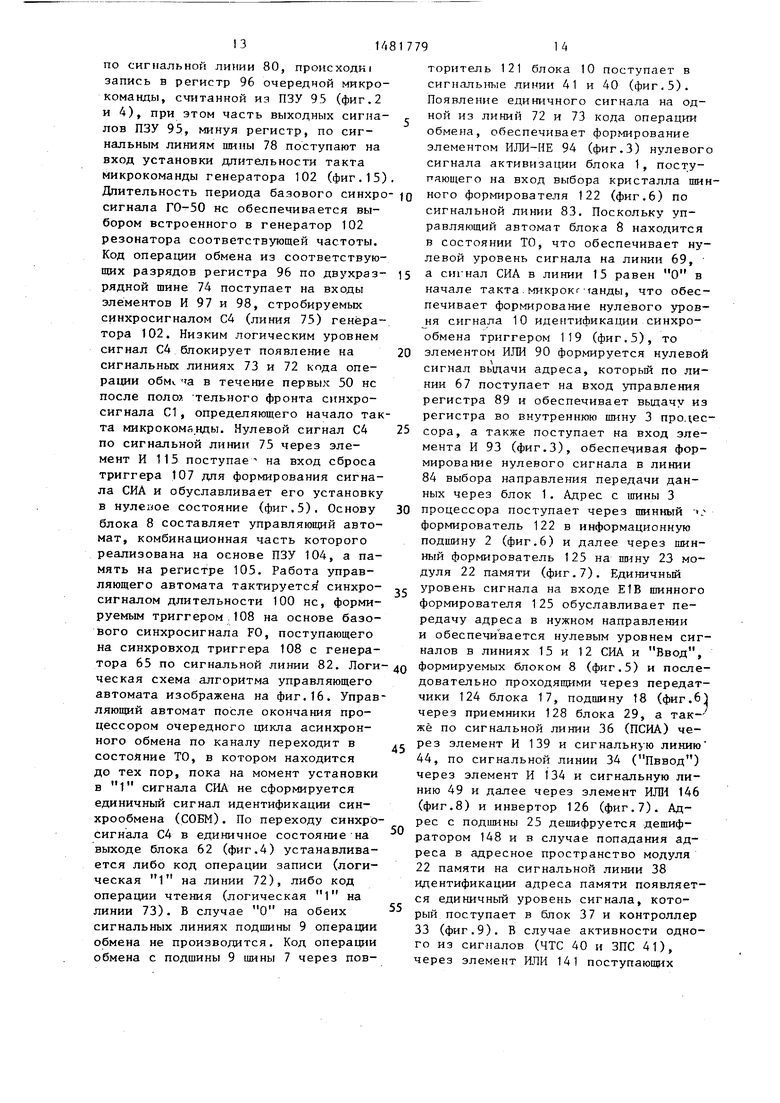

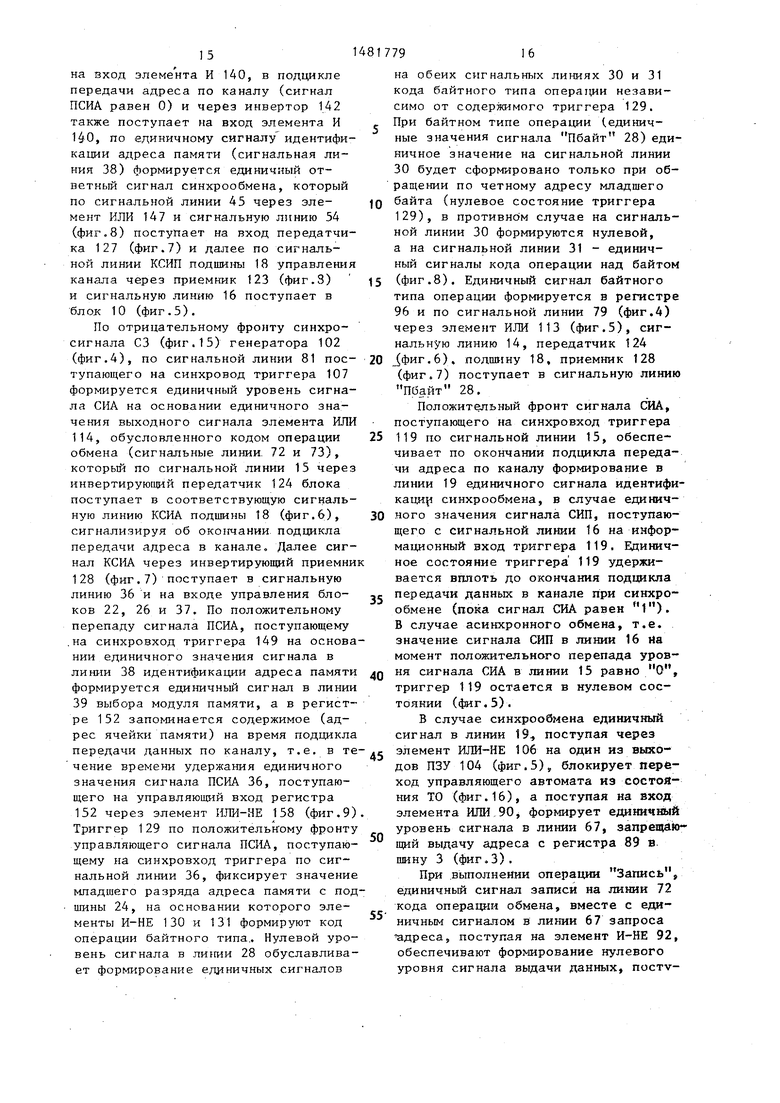

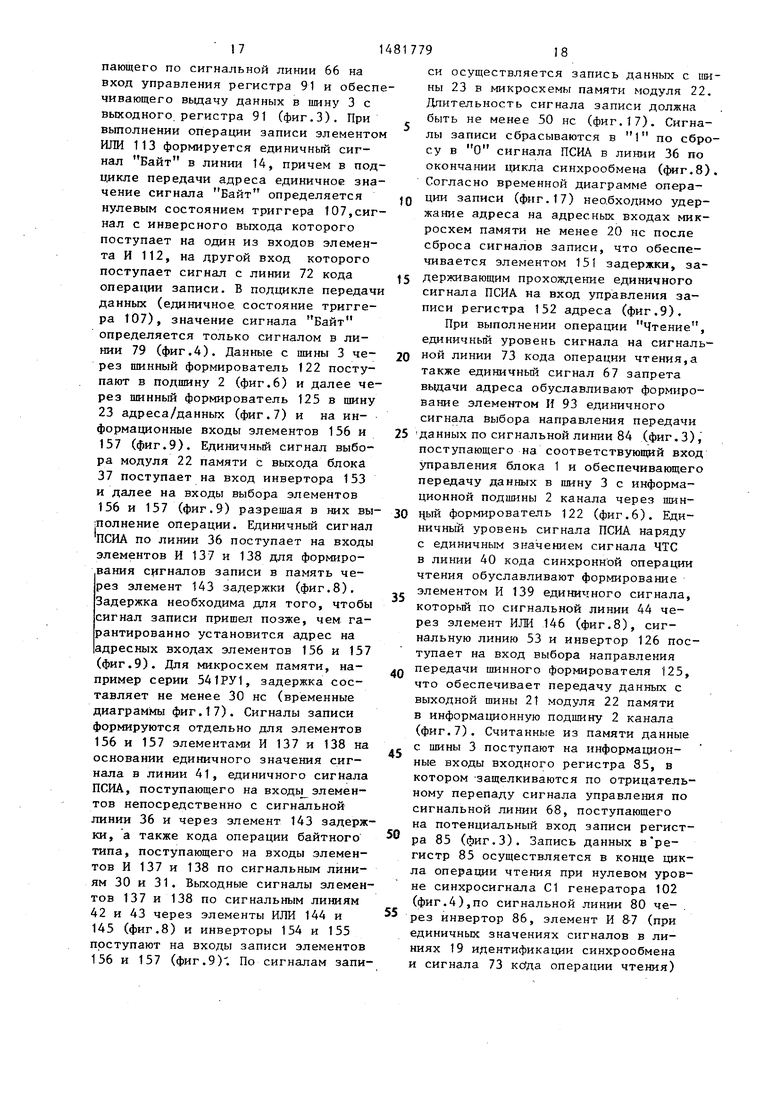

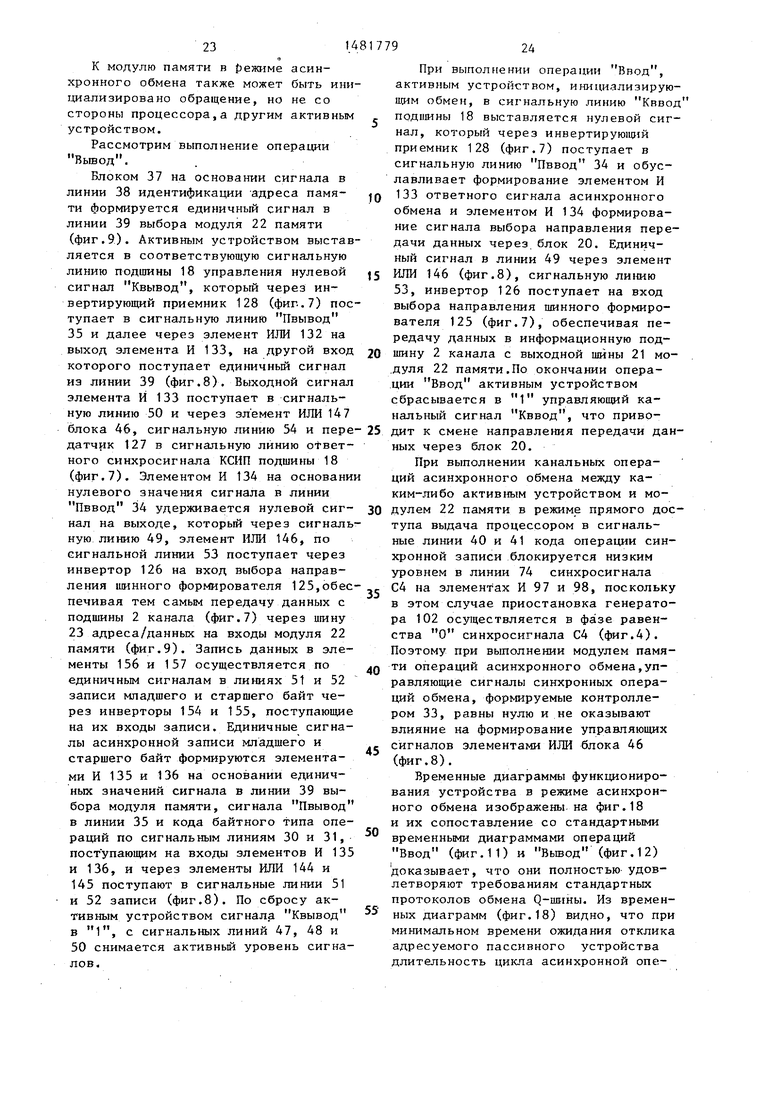

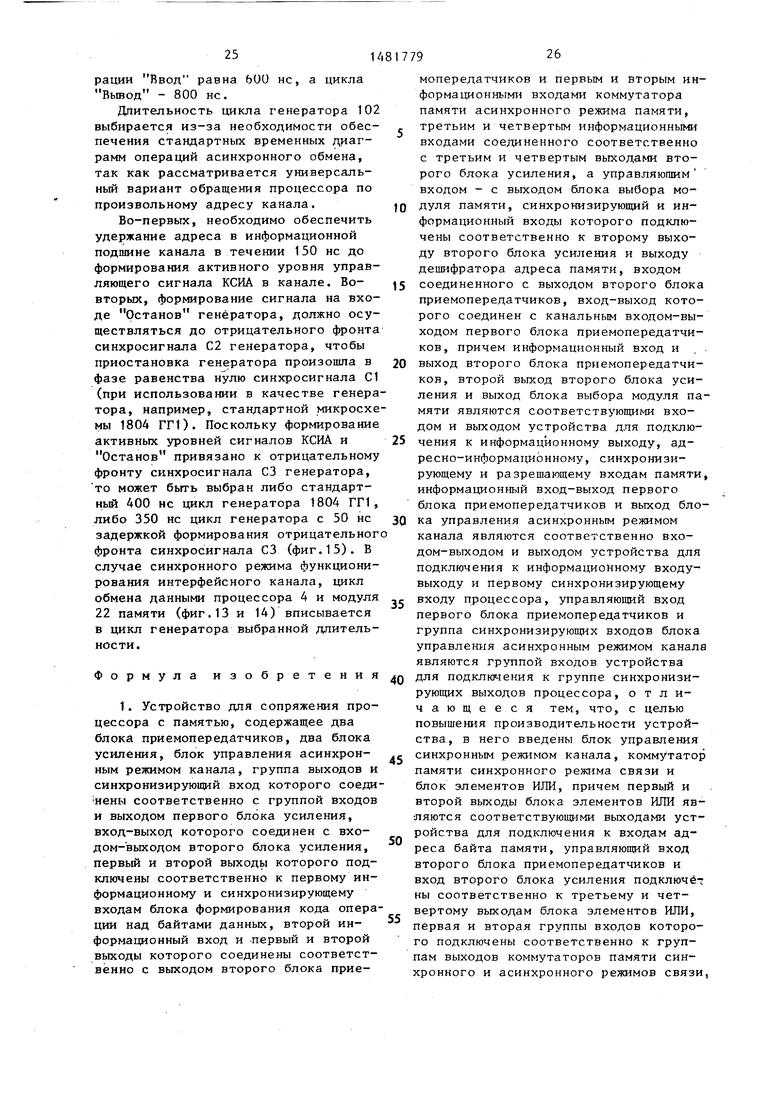

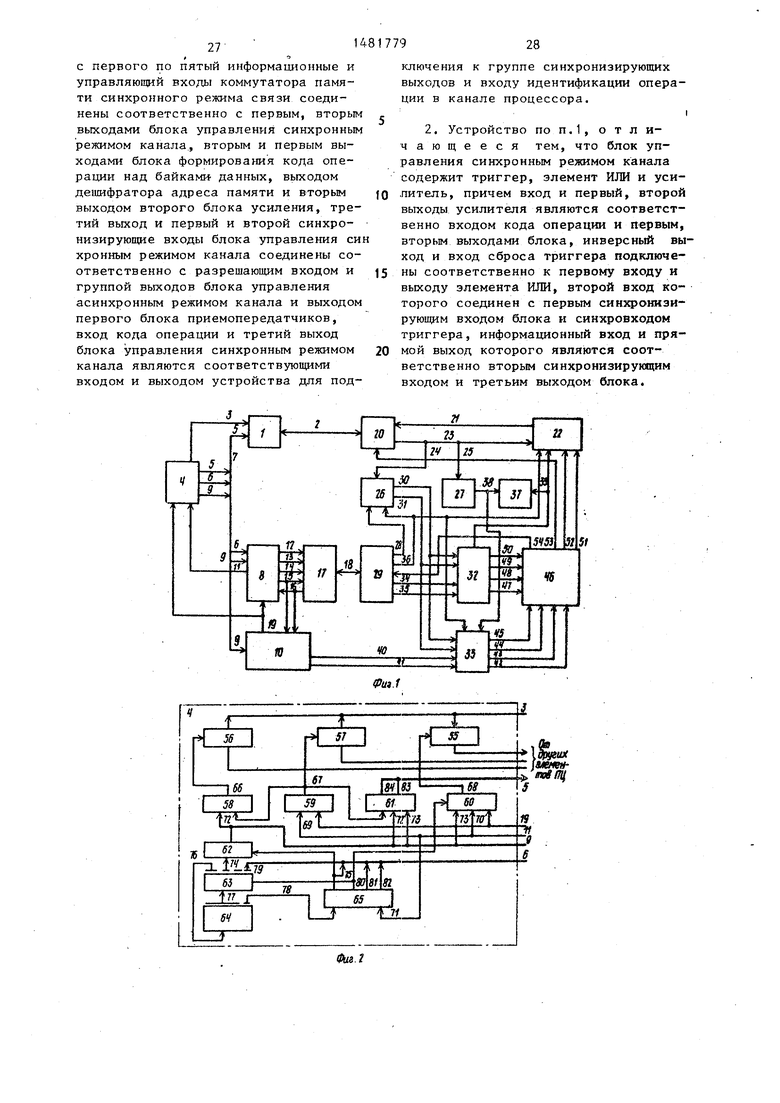

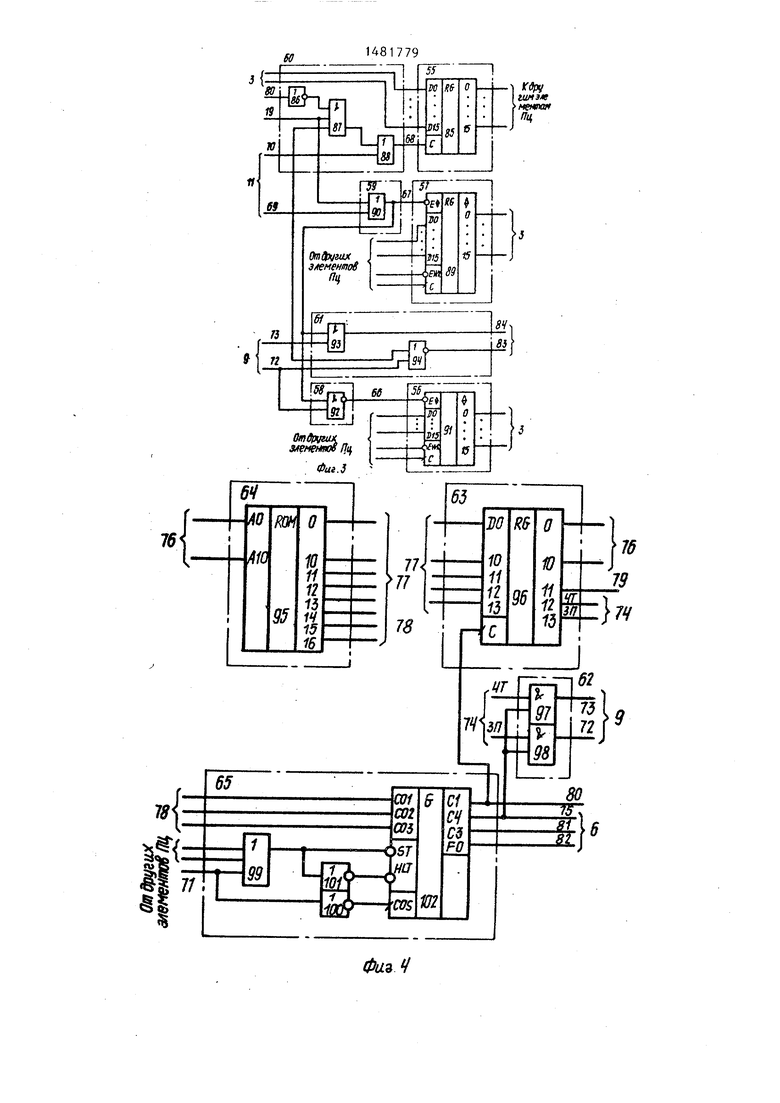

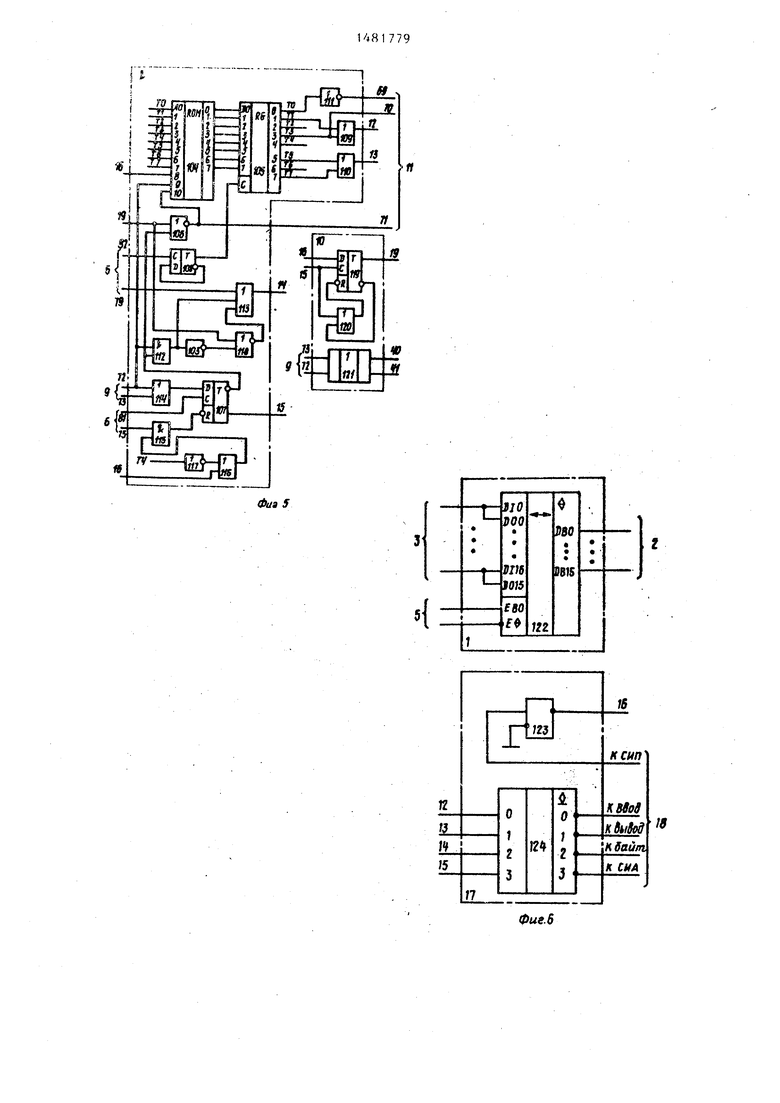

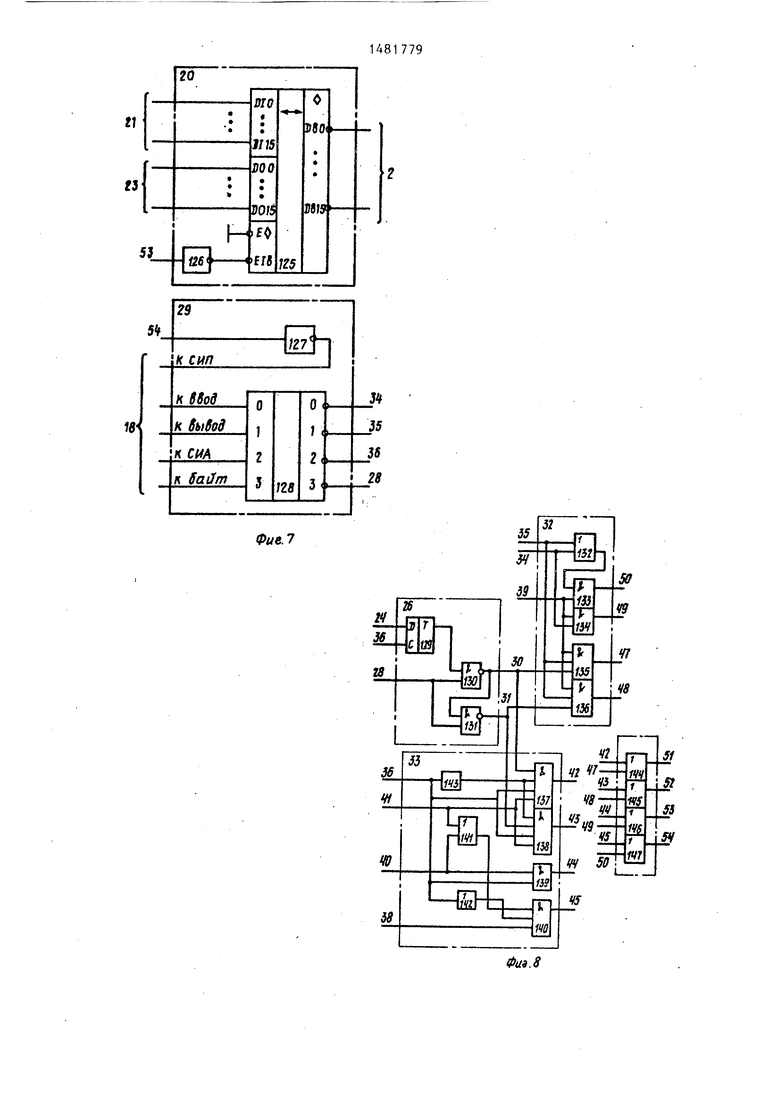

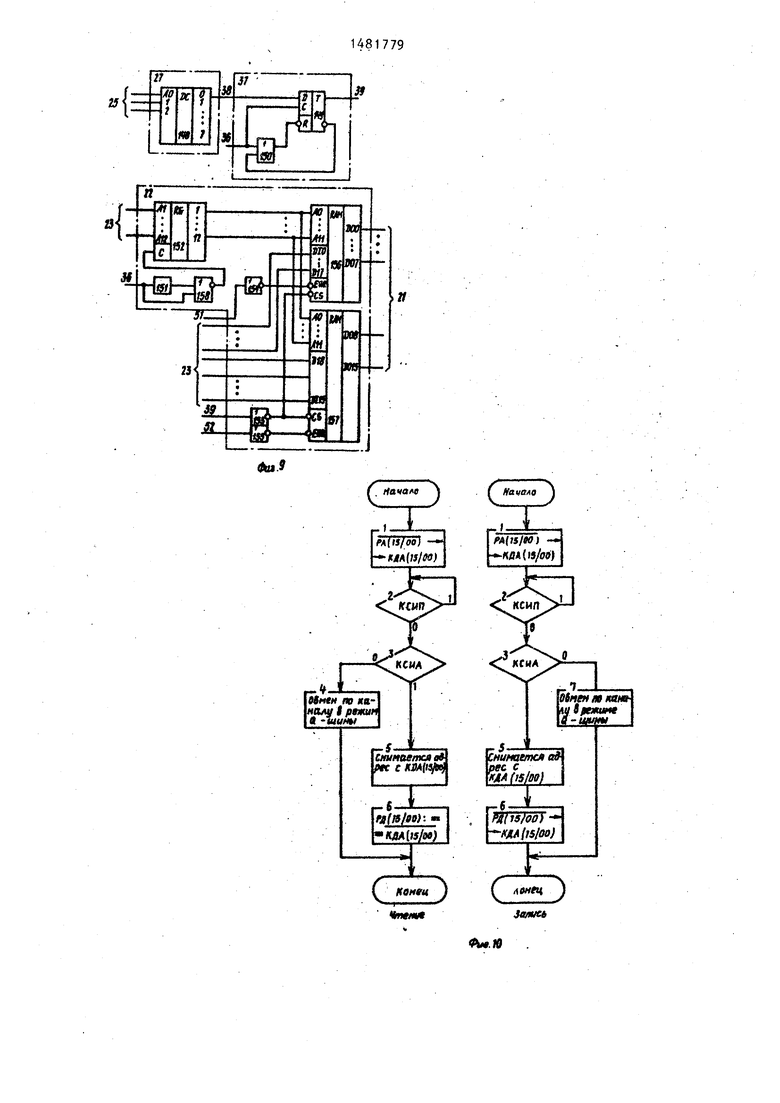

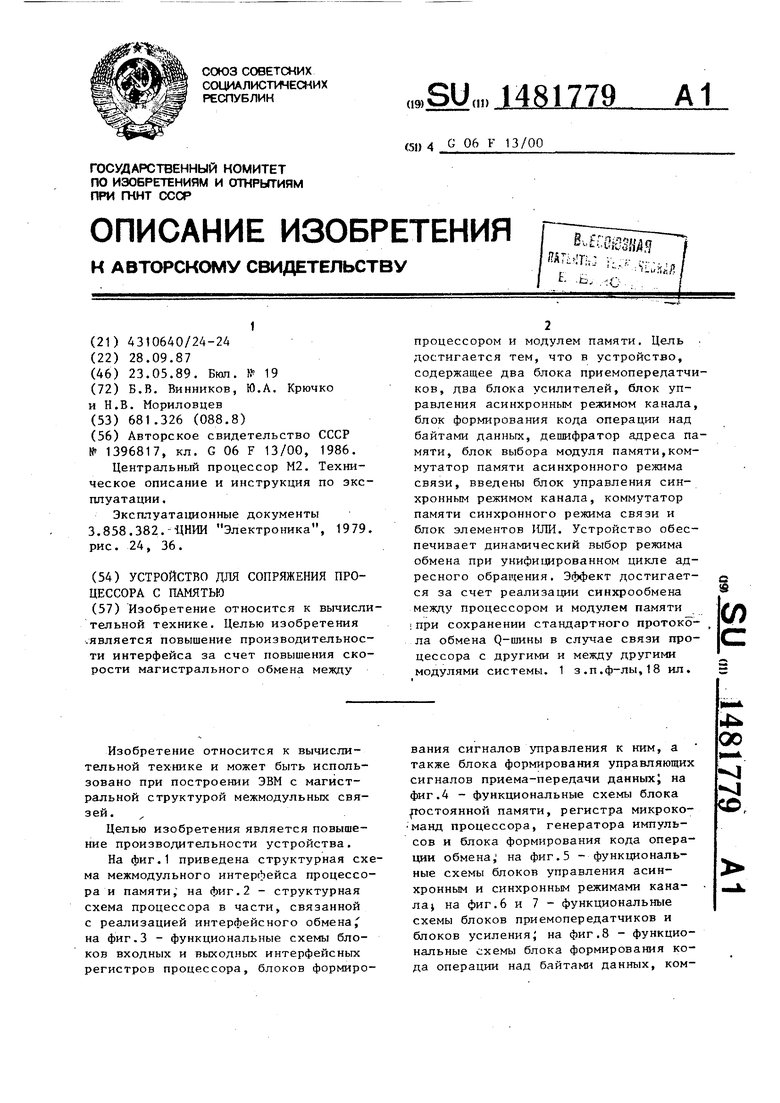

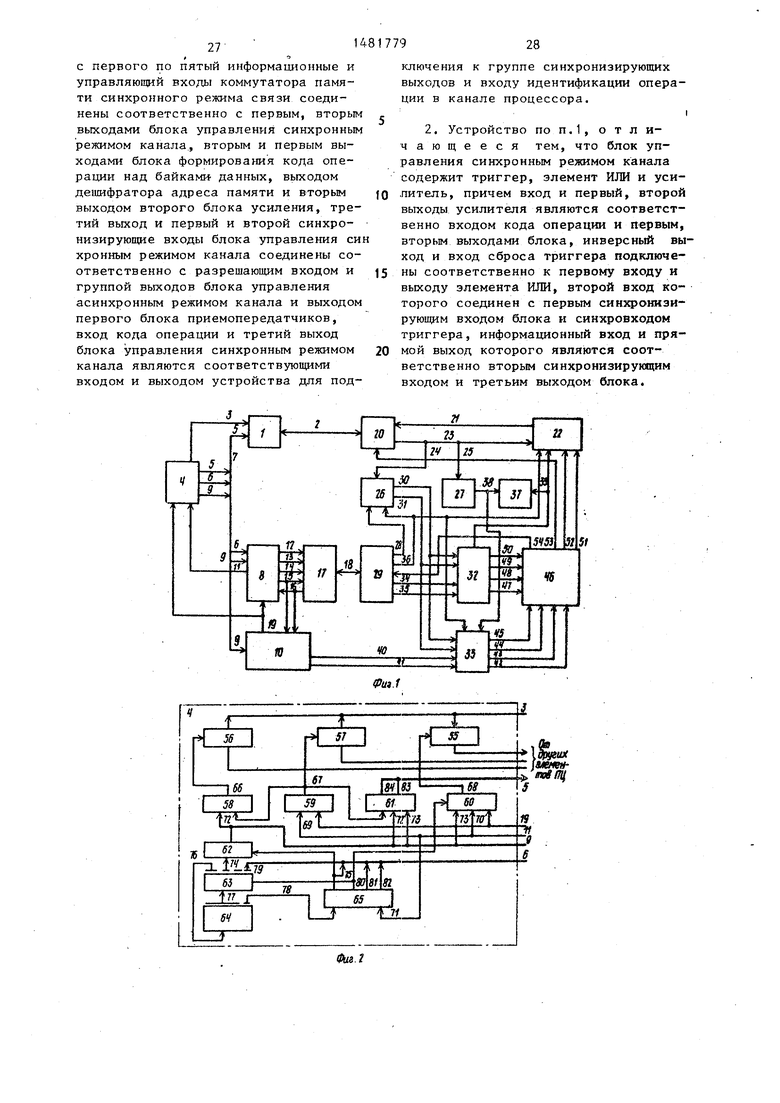

На фиг.1 приведена структурная схема межмодульного интерфейса процессора и памяти; на фиг.2 - структурная схема процессора в части, связанной с реализацией интерфейсного обмена на фиг.З - функциональные схемы блоков входных и выходных интерфейсных регистров процессора, блоков формирования сигналов управления к ним, а также блока формирования управляющих сигналов приема-передачи данных; на фиг.4 - функциональные схемы блока достоянной памяти, регистра микрокоманд процессора, генератора импульсов и блока формирования кода операции обмена; на фиг.З - функциональные схемы блоков управления асинхронным и синхронным режимами канала i на фиг.6 и 7 - функциональные схемы блоков приемопередатчиков и блоков усиления; на фиг.8 - функциональные схемы блока формирования кода операции над байтами данных, ком3

оо

Ј

3148

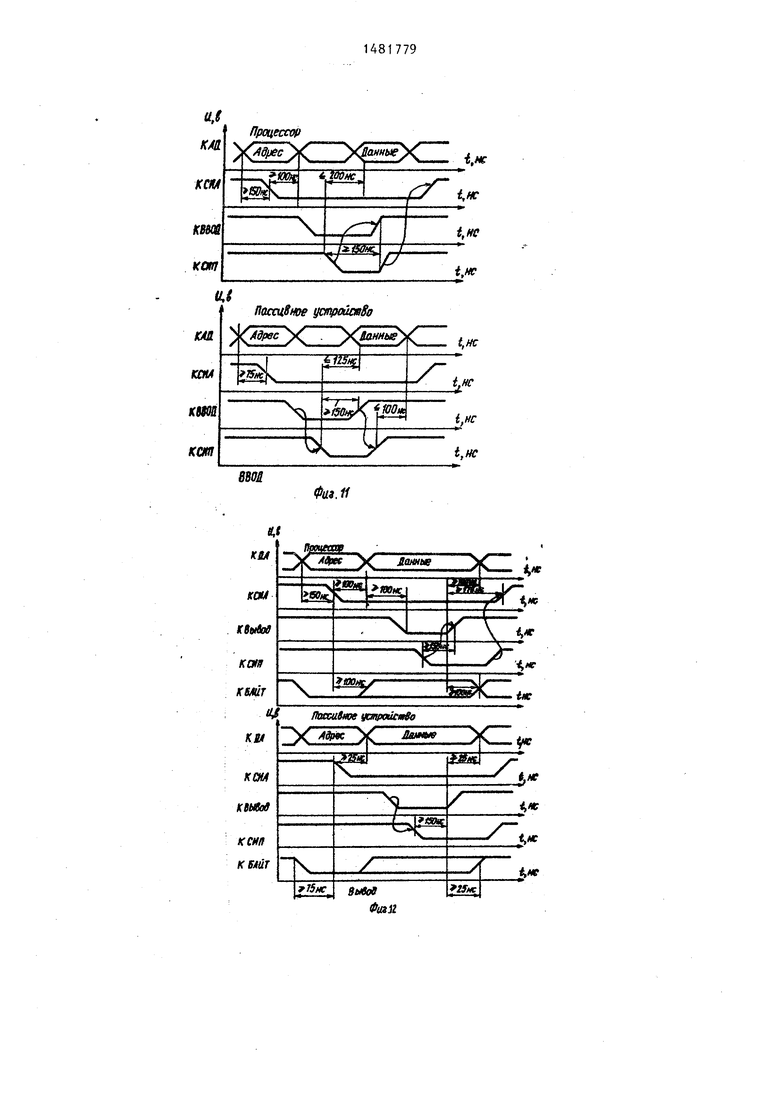

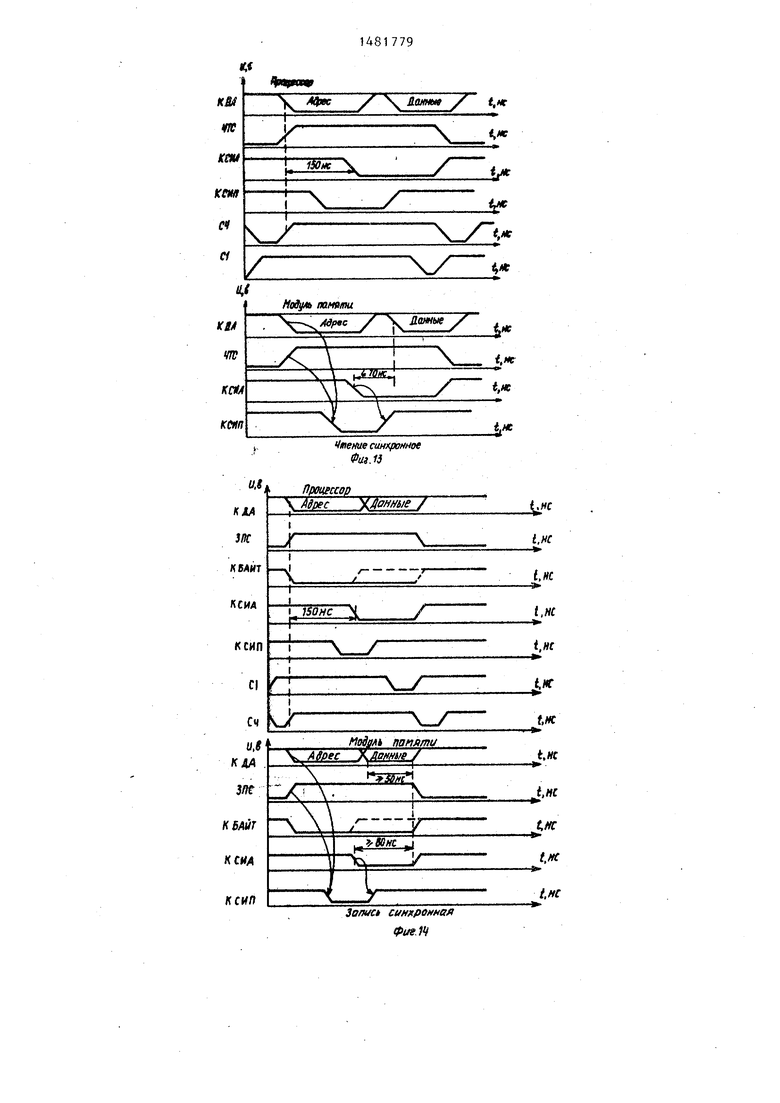

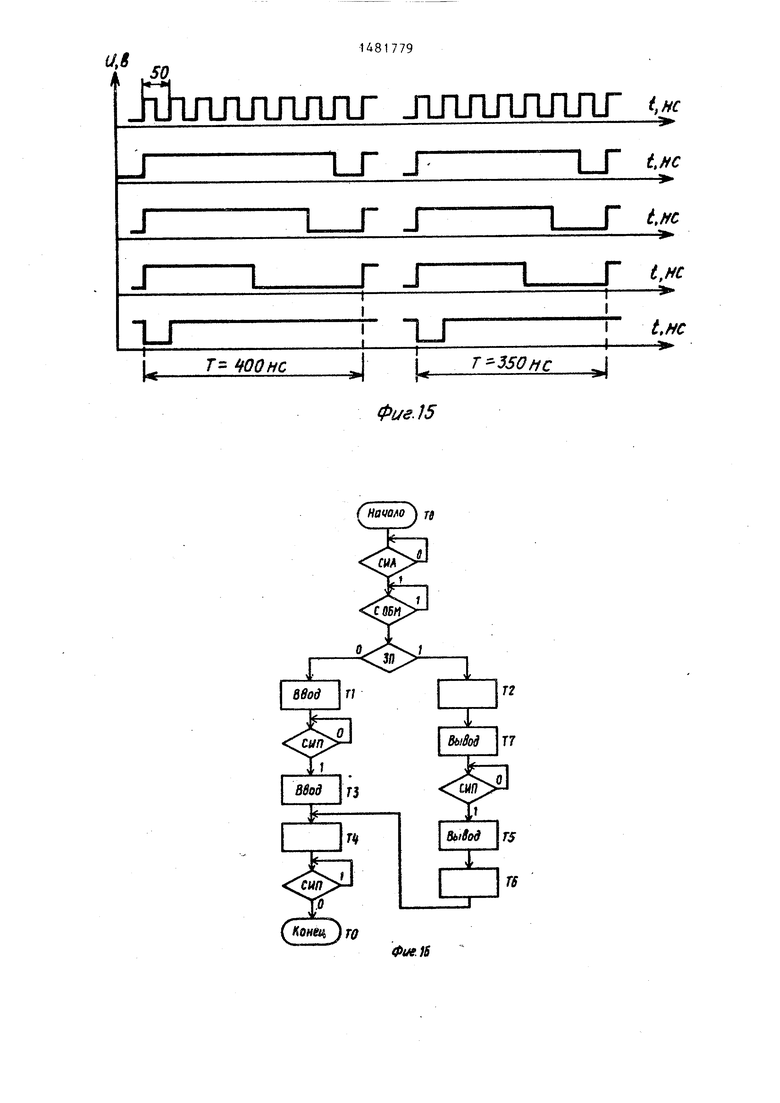

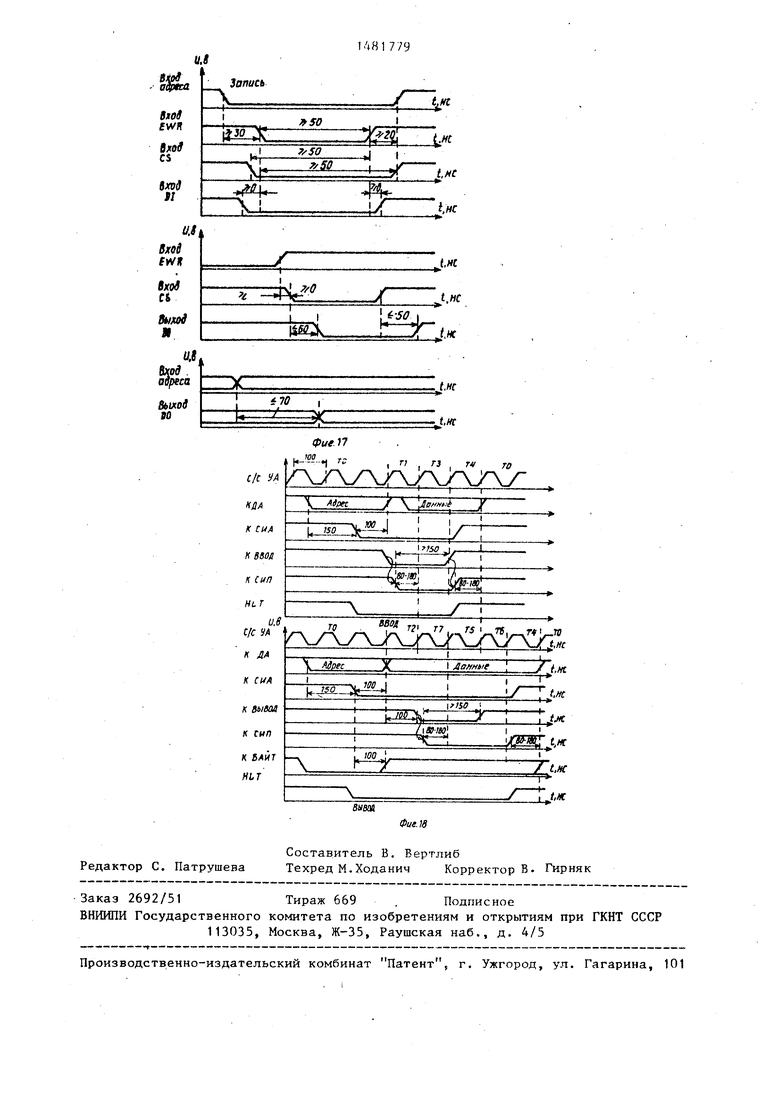

мутаторов памяти асинхронного и синхронного режимов связи, блока элементов ИЛИ1, на фиг. 9 - функциональные схемы блока выбора модуля памяти,дешифратора адреса и модуля памяти ,на фиг. 1 U - обобщенные алгоритмы выполнения процессором операций обмена1, на фиг,11 и 12 - стандартные временные диаграммы операций обмена в Q-шине соответственно ввода и вывода , на фиг. 13 и 14 - временные диаграммы реализации процессором в канале операций синхронного чтения и записи, на фиг.15 - временные диаграммы синхросигналов генератора импульсов для двух циклов микрокоманды различной длительности, на фиг.16 - логическая схема алгоритма управляющего автомата блока управления асинхронным режимом канала, на фиг. 17 - временные диаграммы операций чтения и записи для микросхем ОЗУ 541РУ1, на фиг.18 - временные диаграммы реализации процессором операций асинхронного обмена .

Устройство содержит (фиг.1) первый блок 1 приемопередатчиков, канальный вход/выход которого подсоединен к шестнадцати сигнальным линиям информационной под пины 2 канала, а информационный вход/выход через внутреннюю шину 3 данных соединяется с соответствующим входом/выходом процессора 4. Процессор 4 через линию (подтипу) 5 управления приемопередатчиков, линию (подтипу) 6 управления асинхронным режимом канала управляющей шины 7 соединяется соответственно с блоком 1 приемопередатчиков и блоком 8 управления асинхронным режимом канала, а через линию (подшину) 9 кода операции обмена шины 7 с блоком 8 управления асинхронным и блоком 10 управления синхронным режимами канала. Блок 8 управления асинхронным режимом канала соединен с процессором 4 шиной 11 связи с процессором,сигнальными линиями 12-15 управляющих сигналов асинхронного обмена канала: Ввод, Вывод, Байт, СИА с передатчиками СИП 16 с приемником первого блока 17 усиления, канальный вход/выход которого подсоединен к пяти сигнальным линиям подшины 18 уп- .равляющих сигналов канала. Блок 10 управления синхронным режимом канала через сигнальную линию СИА 15 связан с соответствующим выходом бло779 4

ка 8, через сигнальную линию СИП 16 с выходом приемника соответствующего канального сигнала блока 17, сигнальной линией 19 идентификации операции синхрообмена в канале с соответствующими входами процессора 4 и блока 8. Второй блок 20 приемопередатчиков канальным входом/выходом

Q подсоединен к шестнадцати сигнальным линиям информационной подшины 2 канала, информационным входом через шину 21 данных соединен с выходом блока (модуля) 22 памяти, а выходом

5 через шину 23 адреса/данных, через 1 подшину 24 младшего разряда и через подшину 25 старших разрядов шины 23 блок 20 соединен с входами модуля 22 памяти, блока 26 формирования ко0 Да операции над байтами данных и де- пмфратора 27 адреса памяти. Блок 26 формирования кода операции над байтами данных сигнальной линией Пбайт 28 идентификации байтного типа опера5 ции связан с выходом соответствующего

приемника второго блока 29 усиления, а сигнальными линиями кода операции над младшим байтом 30 и старшим байтом 31 соединен с соответствующими

0 входами коммутатора (контроллера) 32 памяти асинхронного и коммутатора (контроллера) 33 памяти синхронного режимов связи. Второй блок 29 усиления, канальный вход-выход которого подсоединен к пяти сигнальным линиям подшины 18 управляющих сигналов канала, соединяется сигнальными линиями 34 и 35 управляющих сигналов асинхронного обмена Пввод, Пвывод

5

с соответствующими входами контроллера 32 памяти асинхронного режима связи, а ПСИА 36 с блоком 26, блоком 37 выбора модуля памяти, контроллером 33 и модулем 22 памяти. Дешифратор 27 адреса памяти сигнальной линией 38 идентификации адреса памяти соединяется с соответствующими входами контроллера 33 и блока 37, выход которого сигнальной линией 39 выбора модуля соединен с соответствующими

входами модуля 22 памяти и контроллера 32. Контроллер 33 памяти синхронного режима связи двумя сигнальными линиями кода операции синхронного обмена: чтения 40 и записи 41

соединен с соответствующими выходами фблока 10, а четырьмя сигнальными линиями управления синхрообменом: синхронной записи младшего байта 42

синхронной записи старшего байта A3, выбора направления синхронной передачи данных 44 и ответного сигнала /синхронизированного обмена 45 с первыми входами элементов ИЛИ блока 46 элементов ИЛИ, вторые входы которых сигнальными линиями асинхронной записи младшего байта 47, асинхронной записи старшего байта 48, выбора направления асинхронной передачи данных 49 и синхросигнала пассивного устройства 50 соединяется с выходами контроллера 32, а выходы соединены сигнальными линиями записи младшего байта 51 записи старшего байта 52 с соответствующими входами модуля 22 памяти, линией 53 выбора направления передачи данных с блоком 20, линией 54 ответного сигнала обмена модуля памяти ПСИП с передатчиком блока 29.

Блок 8 управления асинхронным режимом канала предназначен для реализации унифицированных алгоритмов Q-шины по обмену информацией процессора с другими модулями системы.

Блок 10 управления синхронным режимом канала предназначен для реализации алгоритмов синхрообмена процессора с модулем 22 памяти.

Дешифратор 27 адреса памяти предназначен для идентификации момента появления на информационной подшине 25 адреса модуля 22 памяти.

Блок 37 выбора модуля памяти обеспечивает активизацию соответствующего модуля памяти 22, адрес которого опознан дешифратором 27.

Контроллер 32 памяти асинхронного режима связи интерпретирует унифицированные сигналы управления асинхронным обменом по Q-шине в сигналы управления модулем 22 памяти.

Контроллер 33 памяти синхронного режима связи обеспечивает формирование сигналов управления модулем памяти при выполнении операций обмена данными с процессором.

Блок 46 элементов ИЛИ осуществляет дизъюнкцию адекватных сигналов управления модуля 22 памяти, формируемых контроллерами 32 и 33.

Блоки 1, 17, 20 и 29 обеспечивают прием и выдачу в сигнальные линии канала информационных и управляющих сигналов обмена.

Блок 26 формирования кода операции над байтами данных формирует уп0

5

0

5

0

5

0

5

5

равляющие сигналы операций над младшими и старшими байтами данных.

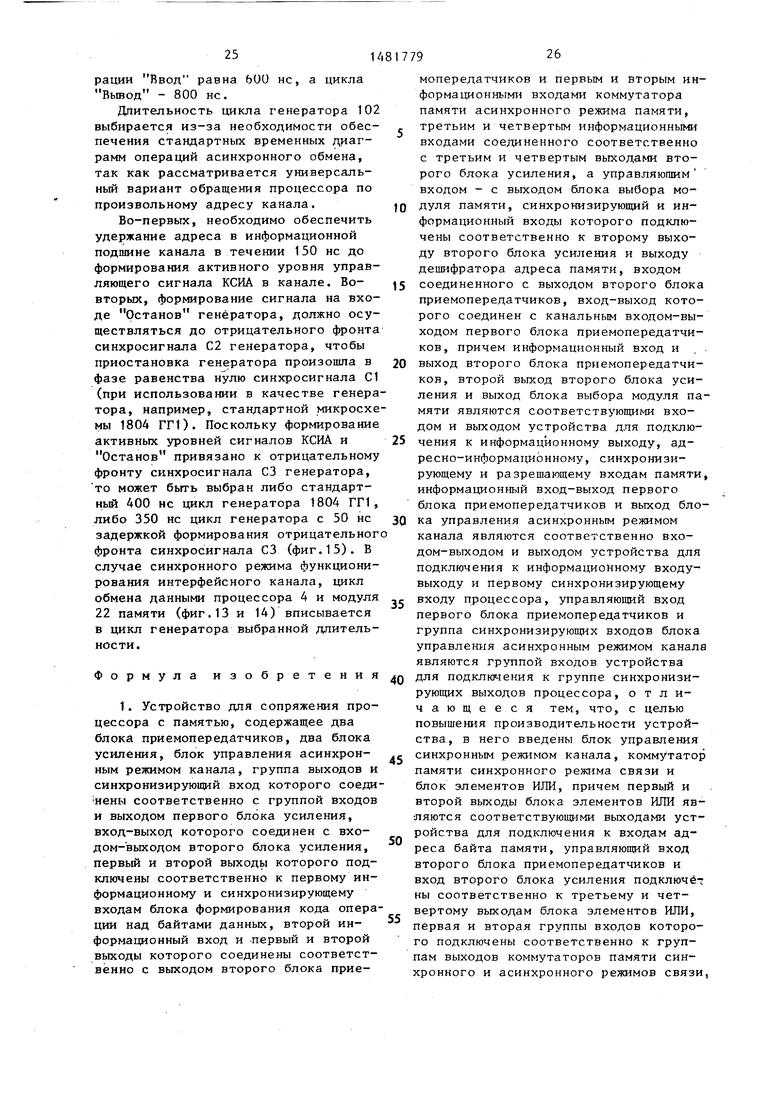

Процессор 4 в части, связанной с реализацией интерфейсного обмена, может быть выполнен в виде типовой структуры, включающей в себя блоки входного регистра 55 данных, выходных регистра 56 данных и регистра 57 адреса, блоки формирования управляющих сигналов выдачи данных 58, выдачи адреса 59, записи 60 данных во входной регистр, приема-передачи данных из канала 61, формирования кода операции обмена 62, а также регистр 63 и блок 64 постоянной памяти (ПЗУ) микрокоманд, генератор 65 импульсой.

Магистральные выходы выходных регистров данных 56 и адреса 57 и вход входного регистра 55 данных подсоединены к магистрали (шине) 3, соединяющей эти регистры с блоком 1, входы управления этих регистров сигнальными линиями 66-68 соединены с выходами регистров 56 и 57 и блока 60.

Входы блоков 59 и 60 подсоединены к сигнальной линии 19 идентификации синхрообмена, вторые входы этих блоков подсоединены соответственно к сигнальным линиям 69 и 70 шины 11 связи процессора и интерфейса,третья сигнальная линия 71 которой подсоединена к управляющему входу режима приостановки генератора 65 импульсов. Блок 62 формирования кода операции обмена сигнальной линией 72 записи шины 9 кода операции обмена соединяется с вторыми входами блоков 58 и 61, а сигнальной линией 73 чтения шины 9 - с третьими входами блоков 60 и 61j вход формирования кода блока 62 через двухразрядную шину 74 соединяется с соответствующим выходом регистра 63 микрокоманд, а вход управления сигнальной линией 75 с первым выходом синхросигналов блока 65 генератора импульсов. Группа разрядов выхода формирования адреса следующей микрокоманды регистра 63 микрокоманд через соответствующую шину 76 соединяется с входом ПЗУ 64 микрокоманд, первый многоразрядный выход которого через шину 77 соединяется с информационным входом регистра 63 микрокоманд, а другой шиной 78 формирования длительности цикла микрокоманды с соответствующим входом генератора 65 импульсов. Выход байтного типа операции регистра 63 подсоединен к сигнальной линии 79 шины б, А выход управления записью соединяется сигнальной линией 80 с вторым выходом синхросигналов генератора 65 импульсов, ко- торьгй в свою очередь через ту же сигнальную линию соединяется с четвертым входом блока 60,.Выходы синхросигналов генератора 65 импульсов (первый, третий и четвертый) подсоединены к сигнальным линиям 75, 81 и 82 управления асинхронным режимом канала.Выходы блока 61 подсоединены к сигнальным линиям активизации 83 блока 1 и

ре 102, обеспечивающем режим приостановки. Выходы синхросигналов С1, С4, СЗ и FO генератора являются соответственно вторым, первым, третьим и четвертым выходами генератора 65, трехразрядный вход формирования длительности цикла микрокоманды генератора 102 является соответствующим входом блокад вход HLT управления режимом Останов генератора соединяется с выходом инвертора 101, вход которого, а также управления режимом Работа генератора 102 соединяются

| название | год | авторы | номер документа |

|---|---|---|---|

| Селекторный канал | 1988 |

|

SU1534465A2 |

| Коммутирующее устройство | 1986 |

|

SU1314348A1 |

| Устройство обработки информации | 1989 |

|

SU1631549A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

| Селекторный канал | 1983 |

|

SU1103218A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для отсчета времени | 1990 |

|

SU1784959A1 |

| СИСТЕМА КОНТРОЛЯ И УПРАВЛЕНИЯ ВЫСОКОВОЛЬТНЫМИ ЯЧЕЙКАМИ РАСПРЕДЕЛИТЕЛЬНОЙ СЕТИ ШАХТЫ | 1990 |

|

RU2037205C1 |

Изобретение относится к вычислительной технике. Целью изобретения является повышение производительности интерфейса за счет повышения скорости магистрального обмена между процессором и модулем памяти. Цель достигается тем, что в устройство, содержащее два блока приемопередатчиков, два блока усилителей, блок управления асинхронным режимом канала, блок формирования кода операции над байтами данных, дешифратор адреса памяти, блок выбора модуля памяти, коммутатор памяти асинхронного режима связи, введены блок управления синхронным режимом канала, коммутатор памяти синхронного режима связи и блок элементов ИЛИ. УСТРОЙСТВО ОБЕСПЕЧИВАЕТ ДИНАМИЧЕСКИЙ ВЫБОР РЕЖИМА ОБМЕНА ПРИ УНИФИЦИРОВАННОМ ЦИКЛЕ АДРЕСНОГО ОБРАЩЕНИЯ. ЭФФЕКТ ДОСТИГАЕТСЯ ЗА СЧЕТ РЕАЛИЗАЦИИ СИНХРООБМЕНА МЕЖДУ ПРОЦЕССОРОМ И МОДУЛЕМ ПАМЯТИ ПРИ СОХРАНЕНИИ СТАНДАРТНОГО ПРОТОКОЛА ОБМЕНА Q -ШИНЫ В СЛУЧАЕ СВЯЗИ ПРОЦЕССОРА С ДРУГИМИ И МЕЖДУ ДРУГИМИ МОДУЛЯМИ СИСТЕМЫ. 1 З.П.Ф-ЛЫ, 18 ИЛ.

выбора 84 направления передачи данных щ с выходом элемента ИЛИ 99, многораз25

30

подтипы 5.

На фиг.3 приведены функциональные ,схемы примеров реализации блоков 55- 61 процессора 4. Регистр 55 данных представляет собой шестнадцатиразряд- 20 ный регистр 85 с потенциальным управлением, блок 60 реализуется на элементе НЕ (инверторе) 86, элементе И 87 и элементе ИЛИ 88. Регистр 57 адреса представляет собой шестнадцатиразрядный регистр 89 с тремя состояниями на выходе. Блок 59 состоит, например, из элемента ИЛИ 90. Регистр 56 данных представляет собой шестнадцатиразрядный регистр 91 с тремя состояниями на выходе. Блок 58 состоит из элемента И-НЕ 92, а блок 61 - из элемента И 93 и элемента ИЛИ-НЕ 94.

На фиг.4 приведены функциональные схемы блоков 62-65 процессора 4. Блок 64 может быть реализован на основе постоянной памяти (ПЗУ) 95, регистр 63 микрокоманд представляет собой четырнадцатиразрядный регистр 96 с динамическим управлением записью, первые одиннадцать разрядов выхода которого составляют группу разрядов выхода формирования адреса следующей микрокоманды, двенадцатый разряд идентифицирует байтных тип операции записи, а тринадцатый и четырнадцатый осуществляют управление операциями соответственно чтения и записиj четырнадцатиразрядный информационный вход регистра 96 является информационным входом, а динамический вход управления записью - входом управления блока 63, блок 62 формирования кода операции обмена состоит из

35

40

45

50

рядный вход которого является при этом входом приостановки генератора 65.

Один из входов элемента ИЛИ 99 подсоединен к сигнальной линии 71 шины 11 связи интерфейса и процессора, к которой также подсоединяется вход инвертора 100, выход которого соединяется с входом СО генератора 10-2, что позволяет обеспечить на этом входе нулевой уровень сигнала при реализации процессором асинхронного обмена в канале, осуществляя тем самым приостановку генерации синхросигналов С1-С4 в фазе равенства О синхросигнала С1, в отличие от приостановки генерации синхросигналов в фазе равенства 0 синхросигнала С4 в других случаях, не связанных с реализацией процессором интерфейсного обмена в канале.

На фиг.5 приведены функциональные схемы примеров реализации блоков 8 и 10.В блок 8 введен элемент 103 задержки, обуславливающий различие в формировании управляющего сигнала Байт при асинхронном и синхронном режимах обмена. Основу блока 8 составляет управляющий автомат, комбинационная часть которого реализуется на основе постоянной памяти (ПЗУ) 104, а память на восьмиразрядном регистре 105, информационные входы которого соединяются с выходами ПЗУ 104, а выходы состояний ТО-Т7 с первыми восьмью входами ПЗУ, девятый вход которого является входом управляющего сигнала СИП 16 блока, десятый вход подсоединен к сигнальной линии 72 записи айны 9 кода

элементов И 97 и 98. Генератор 65 им- операции обмена, и одиннадцатый вход пульсов может быть реализован на эле- --соединен с выходом двухвходового элементе ИЛИ 99, элементах НЕ (инверто- мента ИЛИ-НЕ (06, первый вход которо- рах) 100 и 101, стандартном генерато- го является входом синхрообмена 19

5

0

0

5

0

5

0

рядный вход которого является при этом входом приостановки генератора 65.

Один из входов элемента ИЛИ 99 подсоединен к сигнальной линии 71 шины 11 связи интерфейса и процессора, к которой также подсоединяется вход инвертора 100, выход которого соединяется с входом СО генератора 10-2, что позволяет обеспечить на этом входе нулевой уровень сигнала при реализации процессором асинхронного обмена в канале, осуществляя тем самым приостановку генерации синхросигналов С1-С4 в фазе равенства О синхросигнала С1, в отличие от приостановки генерации синхросигналов в фазе равенства 0 синхросигнала С4 в других случаях, не связанных с реализацией процессором интерфейсного обмена в канале.

На фиг.5 приведены функциональные схемы примеров реализации блоков 8 и 10.В блок 8 введен элемент 103 задержки, обуславливающий различие в формировании управляющего сигнала Байт при асинхронном и синхронном режимах обмена. Основу блока 8 составляет управляющий автомат, комбинационная часть которого реализуется на основе постоянной памяти (ПЗУ) 104, а память на восьмиразрядном регистре 105, информационные входы которого соединяются с выходами ПЗУ 104, а выходы состояний ТО-Т7 с первыми восьмью входами ПЗУ, девятый вход которого является входом управляющего сигнала СИП 16 блока, десятый вход подсоединен к сигнальной линии 72 записи айны 9 кода

операции обмена, и одиннадцатый вход --соединен с выходом двухвходового элемента ИЛИ-НЕ (06, первый вход которо- го является входом синхрообмена 19

блока, а второй вход соединяется с инверсным выходом триггера 107 формирования сигнала СИЛ. Динамический вход управления записью регистра 105 соединяется с прямым выходом триггера 108 формирования периода тактов управляющего автомата, синхровход которого подсоединен к сигнальной линии 82 базового синхросигнала FO генератора 65. Схемы 12 и 13 формирования управляющих сигналов асинхронного обмена Ввод и Вывод блока 8 реализованы на элементах ИЛИ 109 и 110, входы первого соединяются с выходами состояний Т1 и ТЗ, а входы второго - с выходами состояний Т5 и Т7 регистра 105, выход ТЗ которого непосредственно, а выход ТО через элемент НЕ (ин

25

30

вертор) 111 подсоединены к сигнальным 20 бя элемент ИЛИ 132, элементы И 133 линиям 70 и 69. Прямой выход триггера 107 является выходом сигнала СИА 15 блока 8, инверсный выход соединяется с первым входом элемента И 112, второй вход которого подсоединен к сигнальной линии 72 записи шины 9, а выход - к первому входу элемента ИЛИ 113. Второй вход элемента ИЛИ 113 подсоединен к сигнальной линии 79 байтного типа операции шины 6, а выход является выходом 14 формирования управляющего сигнала Байт магистрального обмена блока 8. Информационный вход триггера 107 соединяется с выходом элемента ИЛИ 114, входы которого подсоединены к сигнальным линиям 72 и 73 двухразрядной шины 9 кода операции обмена, а установочный вход гашения-соединен с выходом элемента И 115, первый вход которого подсоединен к сигнальной линии 75 шины 6, а второй вход соединен с выходом элемента ИЛИ 116, Элемент НЕ (инвертор) 117 соединяется входом с выходом состояния Т4 ре- , гистра 105. Вход элемента задержки 103 соединяется с выходом элемента И 112, а инверсный выход - с первым входом элемента ИЛИ-НЕ 118, выход которого подсоединен к третьему входу элемента ИЛИ 113.

35

40

45

50

134 и элементы И 135 и 136.Контролл 33 памяти синхронного режима связи состоит из элементов И 137, 138, 139 и 140, элемента ИЛИ 141, элемен та НЕ (инвертора) 142 и элемента 14 задержки.

Блок 46 элементов ИЛИ состоит из четырех элементов ИЛИ 144-147.

Блок 27 дешифратора адреса памят представляет собой трехвходовый дешифратор 148 из расчета реализации модулей 22 памяти - емкостью бит шестнадцатиразрядной пины 23 ад реса/данных и возможности обращения к байту данных при выполнении опера ции записи. Для выбора конкретного модуля памяти используется один выход дешифратора 148, являющийся выходом 38, а три входа дешифратора соответственно подсоединены к подши не 25 старших разрядов шины адреса/данных.

Блок 37 выбора модуля памяти состоит из триггера 149 и элемента ИЛИ 150.

Блок 22 памяти включает в себя элемент 151 задержки, регистр 152 адреса памяти, элементы НЕ (инверторы) 153-155, элементы 156 и 157 памяти и элемент ИЛИ-НЕ 158.

Устройство работает следующим образом.

Блок 10 управления синхронным режимом канала (фиг.5) состоит из триггера 119, элемента ИЛИ 120 и усилителя (повторителя) 121.55

На фиг.6 приведены функциональные схемы примеров реализации блоков 1 и 17. Блок 1 приемопередатчиков представляет шестнадцатиразрядный шинный формирователь 122.

Блок 17 усиления включает в себя магистральный приемник 123 и магистральный четырехразрядный передатчик 124 управляющих сигналов.

Блок 20 приемопередатчиков представляет собой шестнадцатиразрядный шинный формирователь 125, а блок 29 усиления включает в себя элемент НЕ (инвертор) 126, магистральный передатчик 127 и магистральный четырехразрядный приемник 128.

Блок 26 формирования кода операции над байтами данных состоит из триггера 129 и двух элементов И-НЕ 130 и 131. Контроллер 32 памяти асинхронного режима связи включает в се25

30

20 бя элемент ИЛИ 132, элементы И 133

5

0

5

0

5

134 и элементы И 135 и 136.Контроллер 33 памяти синхронного режима связи состоит из элементов И 137, 138, 139 и 140, элемента ИЛИ 141, элемента НЕ (инвертора) 142 и элемента 143 задержки.

Блок 46 элементов ИЛИ состоит из четырех элементов ИЛИ 144-147.

Блок 27 дешифратора адреса памяти представляет собой трехвходовый дешифратор 148 из расчета реализации модулей 22 памяти - емкостью бит шестнадцатиразрядной пины 23 адреса/данных и возможности обращения к байту данных при выполнении операции записи. Для выбора конкретного модуля памяти используется один выход дешифратора 148, являющийся выходом 38, а три входа дешифратора соответственно подсоединены к подши- не 25 старших разрядов шины адреса/данных.

Блок 37 выбора модуля памяти состоит из триггера 149 и элемента ИЛИ 150.

Блок 22 памяти включает в себя элемент 151 задержки, регистр 152 адреса памяти, элементы НЕ (инверторы) 153-155, элементы 156 и 157 памяти и элемент ИЛИ-НЕ 158.

Устройство работает следующим образом.

Обмен информацией по каналу инициируется со стороны процессора (фиг.10). На информационную подвину

2(фиг.1) процессором 4 через шину

3и блок 1 выставляется адрес, по которому осуществляется обращение,

а на подшину 9 - код соответствующей

II .14

операции. На основании этого кода блок 10 формирует управляющие сигналы ЗПС4 1 и ЧТС40 операций синхронного обмена, т.е. обращение к каналу со стороны процессора всегда начинается как операция синхрообмена. Гшо- ком 8 по сигналам управления подшины 6 через 150 не после выставления адреса в канал формируется в линии 15 активный единичный уровень сигнала СИЛ, который через инвертирующий передатчик блока 17 выставляется в соответствующую сигнальную линию 18 подшины. Если в течение подцикла передачи адреса в канале при единичном уровне сигнала KCI1A в соответствующую сигнальную линию 18 подшины со стороны модуля памяти выставляется активный нулевой уровень сигнала КСИП, идентифицирующий ситуацию обращения процессора именно к модулю 22 (опознание адреса памяти), то по сбросу в 1 сигнала СИА (сигнала КСИА в 0) на основании сигнала СИП в линии 16 с входа приемника блока 17 блоком 10 формируется сигнал в линии 19, поступающий в процессор 4 и блок 8. С информационной подшины 2 процессором 4 снимается адрес и завершается операция синхронного обмена согласно алгоритма (фиг.10). В противном случае блок 8 организует обмен по каналу согласно стандартного протокола Q-шины, формируя в линиях 12, 13 и 14 управляющие сигналы асинхронного обмена Ввод, Вывод и Байт а также сигналы связи интерфейса с процессором по шине 11 (фиг.11 и 12) Временные диаграммы операций синхронного обмена: чтения и записи изображены на фиг.13 и 14. После установки активного сигнала КСИА и идентификации режима синхронного обмена процессор 4 снимает адрес с информационной подшины магистрали,затем либо переключает на прием данных при операции Чтение, либо выстав-, ляет на информационную подшину данные при операции Запись.

В подцикле передачи адреса по каналу осуществляется дешифрация адреса, поступающего в блок 27 с информационной подшины 2 канала через блок 20 и подшину 25 старших разрядов. Сигнал в линии 38, идентифицирующий опознание адреса памяти,поступает в контроллер 33 и запоминается в блоке 37 по синхросигналу ПСИА

77912

в линии 36, что обеспечивает удержание активногр сигнала в линии 39 в течение подцикла передачи данных по каналу. Блок 26 на основании значений младшего разряда адреса, поступающего по подшине 24 в подцикле передачи адреса (при нулевом уровне сигнала ПСИА в линии 36), и сигнала

g байтного типа операции Пбайт линия 28 формирует код операции над младшим 30 и старшим 31 байтами, поступающий в контроллеры 33 и 32. Контроллер 33 на основании сигналов в линиях

кода операции синхрообмена ЧТС40 или ЗПС41 и сигнала 38 идентификации адреса памяти формирует ответный сигнал в линию 45, который через элемент ИЛИ 147, сигнальную линию 54 и

0 передатчик блока 29 поступает в сигнальную линию КСИП подшины 18. По перепаду активного сигнала ПСИА в линии 36 контроллер 33 формирует в линиях 42-44 сигналы синхронной запи5 си младшего и старшего байт, а также выбора направления синхронизированной передачи данных, которые через элементы ИЛИ блока 46 и сигнальные линии 51-53 поступают на соответст0 вующие входы управления модуля 22 памяти и блока 20, обеспечивая тем самым выполнение указанной операции с памятью и передачу данных по шине 23 при выполнении операции записи и

5 по шине 21 при выполнении операции чтения.

Контроллер 32 реализует выполнение операций с памятью при обращении к модулю 22 со стороны других активных

о устройств (не процессора), подключенных к каналу и функционирующих согласно стандартных алгоритмов Q-шиньи

На основании сигнала в линии 39 и кода байтного типа операции (линии 30 и 31), контроллер 32 по управляющим сигналам в линиях 34 и 35 Пввод и Пвывод с блока 29 форт мирует в линиях 47-50 управляющие сигналы асинхронной записи младшего и старшего байта, выбора направле0 ния асинхронной передачи данных и синхросигнала пассивного устройства, которые через блок 46 элементов -ИЛИ и сигнальные линии 51-54 поступают на соответствующие входы управления

5 модуля 22 памяти, блоков 20 и 29.

По положительному фронту тактового сигнала С1 генератора 102,поступающему на синхровход регистра 96

по сигнальной линии 80, происходи запись в регистр 96 очередной микрокоманды, считанной из ПЗУ 95 (фиг.2 и 4), при этом часть выходных сигналов ПЗУ 95, минуя регистр, по сигнальным линиям шины 78 поступают на вход установки длительности такта микрокоманды генератора 102 (фиг.15) Длительность периода базового синхросигнала ГО-50 не обеспечивается выбором встроенного в генератор 102 резонатора соответствующей частоты. Код операции обмена из соответствующих разрядов регистра 96 по двухразрядной шине 74 поступает на входы элементов И 97 и 98, стробируемых синхросигналом С4 (линия 75) генератора 102. Низким логическим уровнем сигнал С4 блокирует появление на сигнальных линиях 73 и 72 кода операции o6Mv. а в течение первых 50 не после поло тельного фронта синхросигнала С1 , определяющего начало такта микрокоманды. Нулевой сигнал С4 по сигнальной линии 75 через элемент И 115 поступав на вход сброса триггера 107 для формирования сигнала СИЛ и обуславливает его установку в нулеиое состояние (фиг.5). Основу блока 8 составляет управляющий автомат, комбинационная часть которого реализована на основе ПЗУ 104, а память на регистре 105. Работа управляющего автомата тактируется синхросигналом длительности 100 не, формируемым триггером 108 на основе базового синхросигнала FO, поступающего на синхровход триггера 108 с генератора 65 по сигнальной линии 82. Логическая схема алгоритма управляющего автомата изображена на фиг.16. Управляющий автомат после окончания процессором очередного цикла асинхронного обмена по каналу переходит в состояние ТО, в котором находится до тех пор, пока на момент установки в 1 сигнала СИА не сформируется единичный сигнал идентификации син- хрообмена (СОБМ). По переходу синхросигнала С4 в единичное состояние на выходе блока 62 (фиг.4) устанавливается либо код операции записи (логическая 1 на линии 72), либо код операции чтения (логическая 1 на линии 73). В случае О на обеих сигнальных линиях подшины 9 операции обмена не производится. Код операции обмена с подшины 9 шины 7 через пов0

5

0

5

торитель 121 блока 10 поступает в сигнальные линии 41 и 40 (фиг.5). Появление единичного сигнала на одной из линий 72 и 73 кода операции обмена, обеспечивает формирование элементом ИЛИ-НЕ 94 (фиг.З) нулевого сигнала активизации блока 1, поступающего на вход выбора кристалла шинного формирователя 122 (фиг.6) по сигнальной линии 83. Поскольку управляющий автомат блока 8 находится в состоянии ТО, что обеспечивает нулевой уровень сигнала на линии 69, а сигнал СИА в линии 15 равен О в начале такта микрокс танды, что обеспечивает формирование нулевого уровня сигнала 10 идентификации синхро- обмена триггером 119 (фиг.5), то элементом ИЛИ 90 формируется нулевой сигнал выдачи адреса, который по линии 67 поступает на вход управления регистра 89 и обеспечивает выдачу из регистра во внутреннюю шину 3 про несера, а также поступает на вход элемента И 93 (фиг.З), обеспечивая формирование нулевого сигнала в линии 84 выбора направления передачи данных через блок 1. Адрес с шины 3 процессора поступает через шинный i.4 формирователь 122 в информационную подшину 2 (фиг.6) и далее через шинный формирователь 125 на шину 23 модуля 22 памяти (фиг.7). Единичный уровень сигнала на входе Е1В шинного формирователя 125 обуславливает передачу адреса в нужном направлении и обеспечивается нулевым уровнем сигналов в линиях 15 и 12 СИА и Ввод, формируемых блоком 8 (фиг.5) и последовательно проходящими через передатчики 124 блока 17, подшину 18 (фиг.6) через приемники 128 блока 29, а также по сигнальной линии 36 (ПСИА) че- с рез элемент И 139 и сигнальною линию 44, по сигнальной линии 34 (Пввод) через элемент И 134 и сигнальную линию 49 и далее через элемент ИЛИ 146 (фиг.8) и инвертор 126 (фиг.7). Адрес с подшины 25 дешифруется дешифратором 148 и в случае попадания адреса в адресное пространство модуля 22 памяти на сигнальной линии 38 идентификации адреса памяти появляется единичный уровень сигнала, который поступает в блок 37 и контроллер 33 (фиг.9). В случае активности одного из сигналов (ЧТС 40 и ЗПС 41), через элемент ИЛИ 141 поступающих

0

5

0

0

5

на вход элемента И 140, в подцикле передачи адреса по каналу (сигнал ПСИА равен 0) и через инвертор 142 также поступает на вход элемента И 140, по единичному сигналу идентификации адреса памяти (сигнальная линия 38) формируется единичный ответный сигнал синхрообмена, который по сигнальной линии 45 через элемент ИЛИ 147 и сигнальную линию 54 (фиг,8) поступает на вход передатчика 127 (фиг.7) и далее по сигнальной линии КСИП подтипы 18 управления канала через приемник 123 (фиг.З) и сигнальную линию 16 поступает в блок 10 (фиг.5).

По отрицательному фронту синхросигнала СЗ (фиг.15) генератора 102 (фиг.4), по сигнальной линии 81 поступающего на синхровод триггера 107 формируется единичный уровень сигнала СИА на основании единичного значения выходного сигнала элемента ИЛИ 114, обусловленного кодом операции обмена (сигнальные линии 72 и 73), который по сигнальной линии 15 через инвертирующий передатчик 124 блока поступает в соответствующую сигнальную линию КСИА подтипы 18 (фиг.6), сигнализируя об окончании подцикла передачи адреса в канале. Далее сигнал КСИА через инвертирующий приемни 128 (фиг.7) поступает в сигнальную линию 36 и на входе управления блоков 22, 26 и 37. По положительному перепаду сигнала ПСИА, поступающему на синхровход триггера 149 на основании единичного значения сигнала в линии 38 идентификации адреса памяти формируется единичный сигнал в линии 39 выбора модуля памяти, а в регистре 152 запоминается содержимое (адрес ячейки памяти) на время подцикла передачи данных по каналу, т.е. в те чение времени удержания единичного значения сигнала ПСИА 36, поступающего на управляющий вход регистра 152 через элемент ИЛИ-НЕ 158 (фиг.9) Триггер 129 по положительному фронту управляющего сигнала ПСИА, поступающему на синхровход триггера по сигнальной линии 36, фиксирует значение младшего разряда адреса памяти с под шины 24, на основании которого элементы И-НЕ 130 и 131 формируют код операции байтного типа. Нулевой уровень сигнала в линии 28 обуславливает формирование единичных сигналов

0

с

на обеих сигнальных линиях 30 и 31 кода байтного типа операции независимо от содержимого триггера 129. При байтном типе операции (единичные значения сигнала Пбайт 28) единичное значение на сигнальной линии 30 будет сформировано только при обращении по четному адресу младшего байта (нулевое состояние триггера 129), в противном случае на сигнальной линии 30 формируются нулевой, а на сигнальной линии 31 - единичный сигналы кода операции над байтом

5 (фиг.8). Единичный сигнал байтного типа операции формируется в регистре 96 и по сигнальной линии 79 (фиг.4) через элемент ИЛИ 113 (фиг.5), сигнальную линию 14, передатчик 124

0 (фиг.6), подпишу 18, приемник 128

(фиг.7) поступает в сигнальную линию Пбайт 28.

Положительный фронт сигнала СИА, поступающего на синхровход триггера

5 119 по сигнальной линии 15, обеспечивает по окончании подцикла передачи адреса по каналу формирование в линии 19 единичного сигнала идентификации синхрообмена, в случае единич0 чого значения сигнала СИП, поступающего с сигнальной линии 16 на информационный вход триггера 119. Единичное состояние триггера 119 удерживается вплоть до окончания подцикла

с передачи данных в канале при синхро- обмене (пока сигнал СИА равен 1). В случае асинхронного обмена, т.е. значение сигнала СИП в линии 16 На момент положительного перепада уровня сигнала СИА в линии 15 равно О, триггер 119 остается в нулевом состоянии (фиг.З).

В случае синхрообмена единичный сигнал в линии 19, поступая через элемент ИЛИ-НЕ 106 на один из выходов ПЗУ 104 (фиг.5), блокирует переход управляющего автомата из состоя- ния ТО (фиг.16), а поступая на вход элемента ИЛИ 90, формирует единичный уровень сигнала в линии 67, запрещающий выдачу адреса с регистра 89 в шину 3 (фиг.З).

При выполнении операции Запись, единичный сигнал записи на линии 72 кода операции обмена, вместе с единичным сигналом в линии 67 запроса адреса, поступая на элемент И-НЕ 92, обеспечивают формирование нулевого уровня сигнала выдачи данных, HOCTV0

0

5

пающего по сигнальной линии 66 на вход управления регистра 91 и обеспечивающего выдачу данных в шину 3 с выходного регистра 91 (фиг.З). При выполнении операции записи элементом ИЛИ 113 формируется единичный сигнал Байт в линии 14, причем в под- цикле передачи адреса единичное значение сигнала Байт определяется нулевым состоянием триггера 107,сигнал с инверсного выхода которого поступает на один из входов элемента И 112, на другой вход которого поступает сигнал с линии 72 кода операции записи. В подцикле передачи данных (единичное состояние триггера 107), значение сигнала Байт определяется только сигналом в линии 79 (фиг.4). Данные с шины 3 через шинный формирователь 122 поступают в подшину 2 (фиг.6) и далее через шинный формирователь 125 в шину 23 адреса/данных (фиг.7) и на информационные входы элементов 156 и 157 (фиг.9). Единичный сигнал выбора модуля 22 памяти с выхода блока 37 поступает на вход инвертора 153 и далее на входы выбора элементов 156 и 157 (фиг.9) разрешая в них выполнение операции. Единичный сигнал ПСИА по линии 36 поступает на входы элементов И 137 и 138 для формирования сигналов записи в память через элемент 143 задержки (фиг.8). Задержка необходима для того, чтобы сигнал записи пришел позже, чем гарантированно установится адрес на адресных входах элементов 156 и 157 (фиг.9). Для микросхем памяти, например серии 541РУ1, задержка составляет не менее 30 не (временные диаграммы фиг.17). Сигналы записи формируются отдельно для элементов 156 и 157 элементами И 137 и 138 на основании единичного значения сигнала в линии 41, единичного сигнала ПСИА, поступающего на входы элементов непосредственно с сигнальной линии 36 и через элемент 143 задержки, а также кода операции байтного типа, поступающего на входы элементов И 137 и 138 по сигнальным линиям 30 и 31. Выходные сигналы элементов 137 и 138 по сигнальным линиям 42 и 43 через элементы ИЛИ 144 и 145 (фиг.8) и инверторы 154 и 155 поступают на входы записи элементов 156 и 157 (фиг.9). По сигналам запи0

5

0

си осуществляется запись данных с тины 23 в микросхемы памяти модуля 22. Длительность сигнала записи должна быть не менее 50 не (фиг.17). Сигналы записи сбрасываются в 1 по сбросу в О сигнала ПСИА в линии 36 по окончании цикла синхрообмена (фиг.8). Согласно временной диаграмме операции записи (фиг.17) необходимо удержание адреса на адресных входах микросхем памяти не менее 20 не после сброса сигналов записи, что обеспечивается элементом 15t задержки, задерживающим прохождение единичного сигнала ПСИА на вход управления записи регистра 152 адреса (фиг.9).

При выполнении операции Чтение, единичный уровень сигнала на сигнальной линии 73 кода операции чтения,а также единичный сигнал 67 запрета выдачи адреса обуславливают формирование элементом И 93 единичного сигнала выбора направления передачи

5 данных по сигнальной линии 84 (фиг.З), поступающего на соответствующий вход управления блока 1 и обеспечивающего передачу данных в шину 3 с информационной подшины 2 канала через шин0 цый формирователь 122 (фиг.6). Единичный уровень сигнала ПСИА наряду с единичным значением сигнала ЧТС в линии 40 кода синхронной операции чтения обуславливают формирование элементом И 139 единичного сигнала, которьй по сигнальной линии 44 через элемент ИЛИ 146 (фиг.8), сигнальную линию 53 и инвертор 126 поступает на вход выбора направления передачи шинного формирователя 125, что обеспечивает передачу данных с выходной шины 21 модуля 22 памяти в информационную подшину 2 канала (фиг.7). Считанные из памяти данные с шины 3 поступают на информационные входы входного регистра 85, в котором защелкиваются по отрицательному перепаду сигнала управления по сигнальной линии 68, поступающего на потенциальный вход записи регистра 85 (фиг.З). Запись данных в регистр 85 осуществляется в конце цикла операции чтения при нулевом уровне синхросигнала С1 генератора 102 (фиг.4),по сигнальной линии 80 через инвертор 86, элемент И 8-7 (при единичных значениях сигналов в линиях 19 идентификации синхрообмена и сигнала 73 операции чтения)

5

0

5

0

5

19

и элемент ИЛИ 88, поступающего в сигнальную пинию 68 (фиг.З).

По окончании цикла обмена, положтельным фронтом сигнала С1 80 генертора 102 осуществляется запись в регистр 96 очередной микрокоманды, считанной из ПЗУ 95 по адресу в линиях 76 из адресного поля регистра 96 (фиг.4). Низким уровнем синхросигнала С4 в линии 75 осуществляетс сброс в О триггера 107, идентифицирующий окончание подцикла передач данных синхрообмена в канале (фиг.5 Нулевым уровнем сигнала СИА 15, через элемент ИЛИ 120 поступающим на вход сброса триггера 119, снимается активный единичный уровень сигнала в линии 19, а нулевым уровнем сигнала ПСИА в линии 36, через элемент ИЛИ 150 поступающим на вход сброса триггера 149, в линии 39 снимается активный единичный уровень сигнала выбора модуля памяти.

Низким уровнем синхросигнала С4 в линии 75 блокируется выдача из регистра 96 кода очередной операции омена в сигнальные линии 72 и 73 (фиг.4), что обуславливает форми- рование элементом ИЛИ-НЕ 94 единичного уровня сигнала в линии 83 активизации блока 1 и соответственно отключение шины 3 от информационной подшины 2 канала.

Рассмотрим теперь реализацию цикла асинхронного обмена со стороны процессора. В подцикле передачи адреса по каналу, т.е. при нулевом уровне сигнала ПСИА в линии 36 дешифратором 148 не будет опознан адрес модуля 22 памяти (фиг.9). Нулевой уровень сигнала идентификации адреса памяти по сигнальной линии 3 поступающий на вход элемента И 140, обусловит формирование нулевого ответного синхросигнала модуля 22 па

мяти, который через сигнальную линию 45, элемент ИЛИ 147 (нулевой уровень сигнала на линии 50 формируется элементом И 133 на основании нулевого значения сигнала в линии 3 выбора модуля памяти), сигнальную, линию 54 (фиг.З), передатчик 127 (фиг.7), сигнальную линию КСИП под- шины 18, приемник 123 (фиг.6), сигнальную линию 16 поступает в блоки 8 и 10 управления (фиг.5). По положительному фронту сигнала СИА в линии 16, идентифицирующему окончание

20

0

подцикла передачи адреса в канале, в триггере 119 подтверждается нулевой пассивный уровень сигнала в линии 19 идентификации синхрообмена. Единичный сигнал на входе ПЗУ 104, формируемый элементом ИЛИ-НЕ 106 на основании нулевого значения сигнала в линии 19 и единичного состояния триггера 107, обусловит переход управляющего автомата в состояние Т1 или Т2, в зависимости от кода операции, в следующем такте функционирования автомата (фиг.16), а также по сигнальной линии 71 поступает на вход элемента ИЛИ 99 и через инвертор 100 на вход генератора 102.Выходной единичный сигнал элемента ИЛИ 99 через инвертор 101 поступает на вход режима Останов генератора 102, вызывая приостановку генерации синхросигналов С1-С4 в фазе равенства О синхросигнала С1 (фиг.4). Низкий уровень сигнала ТО на выходе регист5 ра 105 обуславливает формирование единичного сигнала на выходе инвертора 111 в сигнальной линии 69 ,(фиг,5), поступающего на вход элемента ИЛИ 90 и далее по сигнальной линии 67 на вход управления регистра 89, обеспечивая отключение выходов . этого регистра от шины 3 (фиг.З).

При выполнении операции Запись элементом И-НЕ 92 на основании единичных значений сигнал в линиях 72 и 67 формируется нулевой сигнал выдачи данных по сигнальной линии 66, поступающий на вход управления регистра 91 и обеспечивающий выдачу данных в шину 3. Поскольку значение сигнала в линии 73 кода операции чтения равно 0, элементом И 93 на сигнальной линии 84 выбора направления передачи через блок 1 удерживается нулевой сигнал (фиг.З) и данные через шинный формирователь 122 поступают в информационную подшину 2 канала. Управляющий автомат блока 8 из состояния Т2 переходит в состояние Т7, т.е. с задержкой в 100 не

0 относительно сброса в О, сигнала КСИА, элементом ИЛИ 110 формируется единичный уровень сигнала Вывод, который по сигнальной линии 13 (фиг.5) поступает на вход инверти5 рующего передатчика 124 и далее в .соответствующую сигнальную линию Квывод подшины 18. Управляющий автомат находится в состоянии Т7 до

0

5

0

тех пор, пока адресуемым пассивным устройством канала на сигнальную линию КСИП полшины 18 не будет выставлен активный нулевой уровень сигнала, который через приемник 123 и сигнальную линию 16 (фиг.6) поступает на вход ПЗУ 104 и обуславливает переход управляющего автомата в состояние Т5 (фиг.16). При переходе автомата из состояния Т 5 в Т6 элементом ИЛИ 110 единичный уровень сигнала с сигнальной линии 13 Вывод, т.е. сигнал Квывод снимается как

минимум через 200 не после установки 15 НУЮ линию 16 (фиг.2, 6) и далее на

активного уровня сигнала КСИП, сигнализирующего о приеме пассивным устройством данных с информационной подшины канала. Далее управляющий автомат последовательно переходит в 20 состояние Т6 и через 100 не в состояние Т4, в котором находится до тех пор, пока пассивным устройством не будет сброшен в 1 управляющий сигнал КСИП подшины 18.

При асинхронном обмене в отличие от синхронного обмена согласно стандартной временной диаграмме операции Вывод (фиг.12) необходимо удержание активного уровня управляющего 30 канального сигнала Кбайт в течение 100 не после установки в О сигнала КСИА. Эта задержка обеспечивается элементом 103 (фиг.З). При выполнении синхронной операции записи эта выдержка блокируется единичным уровнем сигнала идентификации синхрооб- мена по сигнальной линии 19, поступающим на вход элемента ИЛИ-НЕ 118 сразу после окончания подцикла пере- ,дачи адреса в канале.

При выполнении операции Чтение управляющий автомат из состояния ТО переходит в состояние Т1 (фиг.16) на основание нулевого значения сигнала в линии 72 и единичного значения выходного сигнала элемента ИЛИ-НЕ-106, поступающих на входы ПЗУ 104. Элементом ИЛИ 109 на основании единичного значения выходного сигнала Т1

выход ПЗУ 104 (фиг.2,5) управляюще- |го автомата, обуславливая его переход в состояние ТЗ (фиг.16). В состоянии ТЗ согласно временной диаграмме операции Ввод (фиг.11) удерживается активный уровень сигнала Ввод, а на сигнальную линию 70 с выхода регистра 105 (фиг.З) поступает единичный сигнал на вход элемен- 25 та ИЛИ 88 и далее через сигнальную линию 68 на вход управления записью во входной регистр 85 (фиг.З). Данные с шины 3 в момент перехода управляющего автомата из состояния ТЗ в Т4 защелкиваются в регистре 85.Управляющий автомат находится в состоя нии Т4 до тех пор, пока адресным пассивным устройством не будет сбро35

шен в 1 управляющий сигнал КСИП подшины 18.

40

Элементом ИЛИ 116 формируется нулевой сигнал, поскольку на сигнальной линии СИП 16 и на выходе инвертора 117 нулевые сигналы, который через элементы 115 поступает на вход сброса триггера 107. Единичный сигнал с инверсного выхода триггера 107 поступает на вход элемента ИЛИ-НЕ 106 и обеспечивает нулевой уровень сиг- нала в сигнальной линии 71 (фиг.5). Сброс в О сигнала на линии 71 обеспечивает выдачу элементами ИЛИ 99 и НЕ 101 сигналов для возобновления работы генератора 102 (фиг.4). Управрегистра 105 (фиг.5) формируется еди-50 ляющий автомат блока 8 переходит в ничный сигнал Ввод, который по начальное (ТО) состояние (фиг.16). сигнальной линии 12 через передат- На временных диаграммах (фиг. 18) ил- чик 124 поступает в сигнальную линию Кввод подшины 18 (фиг.6). Единичный уровень сигнала на сигнальной линии 73 кода операции чтения обуславливает формирование элементом И 93 единичного сигнала выбора направлюстрируется конкретная реализация операций асинхронного обмена в процессоре. Сравнивая их со стандартными протоколами Q-шины (фиг.11 и 12) легко убедиться, что они удовлетворяют всем требованиям последних.

ления передачи данных через блок 1 (фиг.З), по сигнальной линии 84 поступающего на соответствующий вход шинного формирователя 122 (фиг.6) и обуславливающего передачу данных, выставленных пассивным адресуемым устройством на информационную подши- ну 2 канала в шину 3 процессора. По выставлению данных в канал адресуемое устройство выставляет активный сигнал КСИП, который с соответствующей сигнальной линии подшины 18 через приемник 123 поступает в сигналь0

0

выход ПЗУ 104 (фиг.2,5) управляюще- |го автомата, обуславливая его переход в состояние ТЗ (фиг.16). В состоянии ТЗ согласно временной диаграмме операции Ввод (фиг.11) удерживается активный уровень сигнала Ввод, а на сигнальную линию 70 с выхода регистра 105 (фиг.З) поступает единичный сигнал на вход элемен- 5 та ИЛИ 88 и далее через сигнальную линию 68 на вход управления записью во входной регистр 85 (фиг.З). Данные с шины 3 в момент перехода управляющего автомата из состояния ТЗ в Т4 защелкиваются в регистре 85.Управляющий автомат находится в состоянии Т4 до тех пор, пока адресным пассивным устройством не будет сбро30

35

шен в 1 управляющий сигнал КСИП подшины 18.

0

0

Элементом ИЛИ 116 формируется нулевой сигнал, поскольку на сигнальной линии СИП 16 и на выходе инвертора 117 нулевые сигналы, который через элементы 115 поступает на вход сброса триггера 107. Единичный сигнал с инверсного выхода триггера 107 поступает на вход элемента ИЛИ-НЕ 106 и обеспечивает нулевой уровень сиг- нала в сигнальной линии 71 (фиг.5). Сброс в О сигнала на линии 71 обеспечивает выдачу элементами ИЛИ 99 и НЕ 101 сигналов для возобновления работы генератора 102 (фиг.4). Управляющий автомат блока 8 переходит в начальное (ТО) состояние (фиг.16). На временных диаграммах (фиг. 18) ил-

люстрируется конкретная реализация операций асинхронного обмена в процессоре. Сравнивая их со стандартными протоколами Q-шины (фиг.11 и 12) легко убедиться, что они удовлетворяют всем требованиям последних.

К модулю памяти в режиме асинхронного обмена также может быть инициализировано обращение, но не со стороны процессора,а другим активным устройством.

Рассмотрим выполнение операции Вывод.

Блоком 37 на основании сигнала в линии 38 идентификации адреса памяти формируется единичный сигнал в линии 39 выбора модуля 22 памяти (фиг.9). Активным устройством выставляется в соответствующую сигнальную линию подшины 18 управления нулевой сигнал Квывод, который через инвертирующий приемник 128 (фиг..7) поступает в сигнальную линию Пвывод 35 и далее через элемент ИЛИ 132 на выход элемента И 133, на другой вход которого поступает единичный сигнал из линии 39 (фиг.8). Выходной сигнал элемента И 133 поступает в сигнальную линию 50 и через элемент ИЛИ 147

блока 46, сигнальную линию 54 и пере- 25 дит к смене направления передачи дан- датчик 127 в сигнальную линию ответ- ных через блок 20. кого синхросигнала КСИП подшины 18 (фиг.7). Элементом И 134 на основании нулевого значения сигнала в линии

30

Пввод 34 удерживается нулевой сигнал на выходе, который через сигнальную линию 49, элемент ИЛИ 146, по сигнальной линии 53 поступает через инвертор 126 на вход выбора направления шинного формирователя 125,обеспечивая тем самым передачу данных с подшины 2 канала (фиг.7) через шину 23 адреса/данных на входы модуля 22 памяти (фиг.9). Запись данных в элементы 156 и 157 осуществляется по единичным сигналам в линиях 51 и 52 записи младшего и старшего байт через инверторы 154 и 155, поступающие на их входы записи. Единичные сигналы асинхронной записи младшего и старшего байт формируются элементами И 135 и 136 на основании единичных значений сигнала в линии 39 выбора модуля памяти, сигнала Пвывод в линии 35 и кода байтного типа операций по сигнальным линиям 30 и 31, поступающим на входы элементов И 135 и 136, и через элементы ИЛИ 144 и 145 поступают в сигнальные линии 51 и 52 записи (фиг.8). По сбросу активным устройством сигнала Квывод в 1, с сигнальных линий 47, 48 и 50 снимается активный уровень сигналов.

35

40

45

50

55

При выполнении канальных операций асинхронного обмена между каким-либо активным устройством и модулем 22 памяти в режиме прямого доступа выдача процессором в сигнальные линии 40 и 41 кода операции синхронной записи блокируется низким уровнем в линии 74 синхросигнала С4 на элементах И 97 и 98, поскольку в этом случае приостановка генератора 102 осуществляется в фазе равенства О синхросигнала С4 (фиг.4). Поэтому при выполнении модулем памяти операций асинхронного обмена,управляющие сигналы синхронных операций обмена, формируемые контроллером 33, равны нулю и не оказывают влияние на формирование управляющих сигналов элементами ИЛИ блока 46 (фиг.8).

Временные диаграммы функционирования устройства в режиме асинхронного обмена изображены на фиг.18 и их сопоставление со стандартными временными диаграммами операций Ввод (фиг.11) и Вывод (фиг.12) доказывает, что они полностью удовлетворяют требованиям стандартных протоколов обмена Q-шины. Из временных диаграмм (фиг.18) видно, что при минимальном времени ожидания отклика адресуемого пассивного устройства длительность цикла асинхронной one24

0

0

При выполнении операции Ввод, активным устройством, инициализирующим обмен, в сигнальную линию Кввод подшины 18 выставляется нулевой сигнал, который через инвертирующий приемник 128 (фиг.7) поступает в сигнальную линию Пввод 34 и обуславливает формирование элементом И 133 ответного сигнала асинхронного обмена и элементом И 134 формирование сигнала выбора направления передачи данных через блок 20. Единичный сигнал в линии 49 через элемент ИЛИ 146 (фиг.8), сигнальную линию 53, инвертор 126 поступает на вход выбора направления шинного формирователя 125 (фиг.7), обеспечивая передачу данных в информационную под- шину 2 канала с выходной шины 21 модуля 22 памяти.По окончании операции Ввод активным устройством сбрасывается в 1 управляющий канальный сигнал Кввод, что приво5 дит к смене направления передачи дан- ных через блок 20.

0

5

0

5

0

5

При выполнении канальных операций асинхронного обмена между каким-либо активным устройством и модулем 22 памяти в режиме прямого доступа выдача процессором в сигнальные линии 40 и 41 кода операции синхронной записи блокируется низким уровнем в линии 74 синхросигнала С4 на элементах И 97 и 98, поскольку в этом случае приостановка генератора 102 осуществляется в фазе равенства О синхросигнала С4 (фиг.4). Поэтому при выполнении модулем памяти операций асинхронного обмена,управляющие сигналы синхронных операций обмена, формируемые контроллером 33, равны нулю и не оказывают влияние на формирование управляющих сигналов элементами ИЛИ блока 46 (фиг.8).

Временные диаграммы функционирования устройства в режиме асинхронного обмена изображены на фиг.18 и их сопоставление со стандартными временными диаграммами операций Ввод (фиг.11) и Вывод (фиг.12) доказывает, что они полностью удовлетворяют требованиям стандартных протоколов обмена Q-шины. Из временных диаграмм (фиг.18) видно, что при минимальном времени ожидания отклика адресуемого пассивного устройства длительность цикла асинхронной oneрации Ввод равна 600 не, а цикла Вывод - 800 не.

Длительность цикла генератора 102 выбирается из-за необходимости обес- печения стандартных временных диаграмм операций асинхронного обмена, так как рассматривается универсальный вариант обращения процессора по произвольному адресу канала.

Во-первых, необходимо обеспечить удержание адреса в информационной подшине канала в течении 150 не до формирования активного уровня управляющего сигнала КСИА в канале. Во- вторых, формирование сигнала на входе Останов генератора, должно осуществляться до отрицательного фронта синхросигнала С2 генератора, чтобы приостановка генератора произошла в фазе равенства нулю синхросигнала С1 (при использовании в качестве генератора, например, стандартной микросхемы 1804 ГГ1). Поскольку формирование активных уровней сигналов КСИА и Останов привязано к отрицательному фронту синхросигнала СЗ генератора, то может быть выбран либо стандартный 400 не цикл генератора 1804 ГГ1, либо 350 не цикл генератора с 50 не задержкой формирования отрицательног фронта синхросигнала СЗ (фиг.15). В случае синхронного режима функционирования интерфейсного канала, цикл обмена данными процессора 4 и модуля 22 памяти (фиг.13 и 14) вписывается в цикл генератора выбранной длительности.

Формула изобретения

с первого по пятый информационные к управляющий входы коммутатора памяти синхронного режима связи соединены соответственно с первым, вторым выходами блока управления синхронным режимом канала, вторым и первым выходами блока формирования кода операции над байками- данных, выходом дешифратора адреса памяти и вторым выходом второго блока усиления, третий выход и первый и второй синхронизирующие входы блока управления си хронным режимом канала соединены соответственно с разрешающим входом и группой выходов блока управления асинхронным режимом канала и выходом первого блока приемопередатчиков, вход кода операции и третий выход блока управления синхронным режимом канала являются соответствующими входом и выходом устройства для подключения к группе синхронизирующих выходов и входу идентификации операции в канале процессора.

so

n

76

Ч

{

ГО К

el

) ынзле менпан nu,

76

Фал Ч

г

Пассивнее ganpouatlfo Адрес XXAw Ae-:

кои Kttitoa

кап кшт

кг кем

KtNM

кем к влит

6LLISVI

(QKftQ

го

Фиг. 15

72

Г7

Фие.16

| Авторское свидетельство СССР № 1396817, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Техническое описание и инструкция по эксплуатации | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| -ЦНИИ Электроника, 1979 | |||

| рис | |||

| Пишущая машина для тюркско-арабского шрифта | 1922 |

|

SU24A1 |

Авторы

Даты

1989-05-23—Публикация

1987-09-28—Подача