Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и систем управления.

Известно триггерное устройство (см. патент РФ N 1045354 от 17.05.82, МКИ: H 03 K 3/286, "Триггерное устройство (второй вариант), Г.И.Шишкин, опубликовано 30.09.83, Бюл. N 36), содержащее бистабильное устройство, вход которого соединен с первым выводом резистора и первым выводом конденсатора, второй вывод которого подключен к нулевой шине. Прямой выход бистабильного устройства подключен ко второму выводу резистора. Бистабильное устройство содержит элемент "ИСКЛЮЧАЮЩЕЕ ИЛИ" и тактируемый Д-триггер, выход которого подключен к первому входу элемента "ИСКЛЮЧАЮЩЕЕ ИЛИ", второй вход которого соединен с тактовым входом Д-триггера и со входом триггерного устройства, а выход является прямым входом бистабильного устройства. Д-вход триггера является входом бистабильного устройства.

Недостатком известного триггерного устройства является отсутствие возможности выявления его несанкционированного переключения из-за отсутствия дополнительного (промежуточного) состояния, свидетельствующего о режиме переключения триггерного устройства.

Известно триггерное устройство (см. патент РФ N 1276222 от 28.06.85, МКИ: H 03 K 3/286, "Триггерное устройство" (первый вариант), А.Я.Рыбаков, Г. И. Шишкин, опубликовано 27.01.95, Бюл. N 3), которое выбрано в качестве прототипа и содержит резистор, первый вывод которого соединен с первым выводом конденсатора, второй вывод которого подключен к нулевой шине, и бистабильное устройство, вход и прямой выход которого соединены соответственно с первым и вторым выводами резистора. Бистабильное устройство содержит три элемента ИЛИ-НЕ и тактируемый D-триггер. Первые входы первого и второго элементов ИЛИ-НЕ соединены с соответствующими установочными входами триггерного устройства. Второй вход первого элемента ИЛИ-НЕ соединен с выходом второго элемента ИЛИ-НЕ, а выход является прямым выходом бистабильного устройства. Прямой выход D-триггера соединен со вторым входом второго элемента ИЛИ-НЕ, а D-вход является входом бистабильного устройства. Первый и второй входы третьего элемента ИЛИ-НЕ соединены с соответствующими установочными входами триггерного устройства, а выход - с тактовым входом D-триггера.

Недостатком известного триггерного устройства является отсутствие возможности выявления несанкционированного переключения под действием помех или при отказе элементов схемы из-за отсутствия дополнительного (промежуточного) состояния, свидетельствующего о режиме переключения триггерного устройства.

Задачей, решаемой предлагаемым техническим решением, является создание триггерного устройства, обладающего возможностью выявления несанкционированного переключения триггерного устройства под действием помех или при отказе элементов схемы.

Технический результат, заключающийся в обеспечении возможности выявления несанкционированного переключения триггерного устройства под действием помех или при отказе элементов схемы, достигается тем, что в триггерное устройство, содержащее резистор, первый и второй выводы которого соединены соответственно с первым выводом конденсатора и прямым выходом бистабильного устройства, введены элемент И-НЕ, инвертор и второй резистор, один вывод которого соединен с инверсным выходом бистабильного устройства, другой вывод - со вторым выводом конденсатора и через инвертор с первым входом элемента И-НЕ, второй вход которого соединен с первым выводом конденсатора, а выход соединен со входом бистабильного устройства.

Указанная совокупность признаков позволяет обеспечить возможность выявления несанкционированного переключения триггерного устройства за счет обеспечения дополнительного состояния конденсатора, причем в режиме хранения информации конденсатор всегда заряжен в одном или другом направлении, разряженное состояние конденсатора свидетельствует о режиме переключения триггерного устройства.

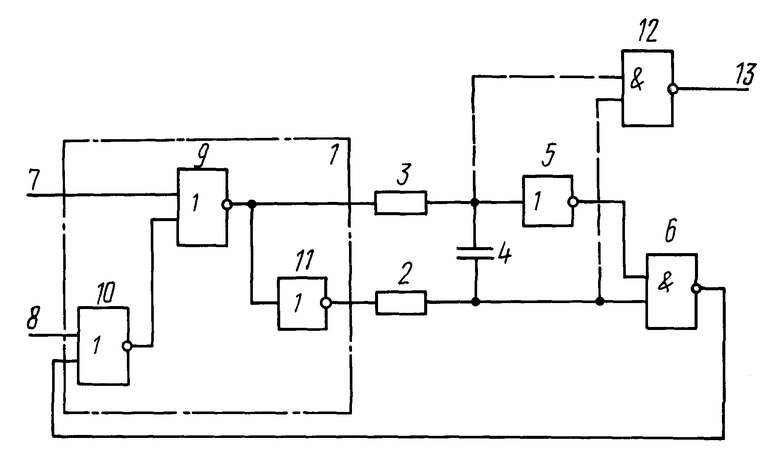

На чертеже представлена принципиальная электрическая схема триггерного устройства.

Триггерное устройство содержит бистабильное устройство 1, первый 2 и второй 3 резисторы, конденсатор 4, инвертор 5, элемент И-НЕ 6. Первый и второй выводы резистора 2 соединены соответственно с первым выводом конденсатора 4 и прямым выходом бистабильного устройства 1, инверсный выход которого соединен с первым выводом резистора 3, второй вывод которого соединен со вторым выводом конденсатора 4 и через инвертор 5 с первым входом элемента И-НЕ 6. Вход бистабильного устройства 1 соединен с выходом элемента И-НЕ 6, второй вход которого соединен с первым выводом конденсатора 4. Бистабильное устройство 1 содержит два элемента ИЛИ-НЕ 9, 10 и инвертор 11. Первые входы элементов ИЛИ-НЕ 9, 10 являются соответственно первым и вторым входами бистабильного устройства 1 и соединены соответственно с входом 7 установки и входом 8 сброса триггерного устройства. Второй вход элемента ИЛИ-НЕ 9 соединен с выходом элемента ИЛИ-НЕ 10, второй вход которого является входом бистабильного устройства 1. Выход элемента ИЛИ-НЕ 9 является инверсным выходом бистабильного устройства 1 и соединен через инвертор 11 с прямым выходом бистабильного устройства 1. В качестве выходов триггерного устройства могут использоваться прямой и инверсный выходы бистабильного устройства 1.

Для выявления переключения в триггерное устройство может быть введен логический элемент 12, выполненный, например, в виде элемента И-НЕ, первый и второй входы которого соединены соответственно с первым и вторым выводами конденсатора 4, а выход является контрольным выходом 13 триггерного устройства.

При включении напряжения питания на входе 7 установки и на входе 8 сброса триггерного устройства присутствует уровень логического "0", конденсатор 4 разряжен.

Бистабильное устройство 1 при включении питания может установиться как в состояние логического "0", так и в состояние логической "1". Допустим, что бистабильное устройство 1 установилось в состояние логической "1". При этом на прямом выходе бистабильного устройства 1 присутствует уровень логической "1", а на инверсном выходе - уровень логического "0".

Напряжение на обоих выводах конденсатора 4, а следовательно, и на входе инвертора 5 и на втором входе элемента И-НЕ 6 в момент включения питания определяется соотношением сопротивлений резисторов 2, 3. Поскольку сопротивление резистора 3 выбрано примерно на порядок больше сопротивления резистора 2, напряжение на обоих выводах конденсатора 4 практически равно напряжению на прямом выходе бистабильного устройства 1 и соответствует уровню логической "1". При этом на выходе инвертора 5 и на первом входе элемента И-НЕ 6 присутствует уровень логического "0", что определяет наличие уровня логической "1" на выходе элемента И-НЕ 6 и вызывает переключение логических элементов 10, 9, 11 соответственно в состояние логического "0", логической "1" и логического "0". Бистабильное устройство 1 устанавливается в состояние логического "0". На обоих выводах конденсатора 4, а следовательно, и на втором входе элемента И-НЕ 6 и на входе инвертора 5 устанавливается уровень логического "0", инвертор 5 переключается в состояние логической "1", на выходе элемента И-НЕ 6 сохраняется уровень логической "1", а бистабильное устройство 1 остается в состоянии логического "0". Конденсатор 4 начинает заряжаться напряжением логической "1" с инверсного выхода бистабильного устройства 1 через резисторы 2, 3. При этом напряжение на втором выводе конденсатора 4 начинает повышаться. При достижении указанным напряжением порога срабатывания инвертор 5 переключается в состояние логического "0", состояние элемента И-НЕ 6 не изменяется. Далее происходит заряд конденсатора 4 до напряжения питания. После заряда конденсатора 4 процесс установки триггерного устройства в исходное состояние логического "0" заканчивается.

При поступлении импульса положительной полярности на вход 7 установки бистабильное устройство 1 переключается в состояние логической "1". При этом на выходе элемента ИЛИ-НЕ 9, а следовательно, и на инверсном выходе бистабильного устройства 1 формируется уровень логического "0", который переключает инвертор 11 и на его выходе, а следовательно, и на прямом выходе бистабильного устройства устанавливается уровень логической "1". Состояние элемента ИЛИ-НЕ 10 не изменяется.

В момент переключения бистабильного устройства 1 на первом и втором выводах конденсатора 4 потенциал возрастает на величину, равную падению напряжения на защитном диоде (Uд), который установлен на входе инвертора 5 и привязан к цепи питания Eпит. Защитные диоды установлены на входах логических элементов внутри микросхем, выполненных на основе КМОП-технологии. См., например, Цифровые интегральные микросхемы: Справочник/П.П.Мальцев, Н.С.Долидзе, М. И. Критенко и др. - М.: Радио и связь, 1994, с. 101, рис. 3.12). На втором выводе конденсатора 4, а следовательно, и на входе инвертора 5 потенциал станет равен Eпит + Uд; на первом выводе конденсатора 4, а следовательно, на втором входе элемента И-НЕ 6 потенциал станет равен Uд. При этом начинает протекать ток разряда конденсатора 4 через прямой выход бистабильного устройства 1, резистор 2, защитный диод и цепь питания. Ток, протекающий через резистор 3, по сравнению с током, протекающим через резистор 2, незначительный, т. к. сопротивление резистора 3 на порядок больше сопротивления резистора 2. Напряжение на первом выводе конденсатора 4, а следовательно, и на втором входе элемента И-НЕ 6 повышается. При достижении указанным напряжением порога срабатывания элемент И-НЕ 6 не изменяет состояния, т. к. на первом выходе элемента И-НЕ 6 находится уровень логического "0", который удерживает элемент И-НЕ 6 в состоянии логической "1". Далее напряжение на первом выводе конденсатора 4 возрастает до напряжения на прямом выходе бистабильного устройства 1, т.е. практически до Eпит. Как только напряжение на конденсаторе 4 достигнет величины Uд, разряд конденсатора 4 через защитный диод заканчивается и он медленно заряжается через резисторы 2, 3.

Напряжение на втором выводе конденсатора 4, а следовательно, и на входе инвертора 5 начинает понижаться. При достижении указанным напряжением порога срабатывания инвертор 5 переключается в состояние логической "1". При этом на первом входе элемента И-НЕ 6 появляется уровень логической "1", который переключает его в состояние логического "0". Логический "0" поступает на вход бистабильного устройства 1, переключает элемент ИЛИ-НЕ 10 в состояние логической "1", но в целом не изменяет состояние бистабильного устройства 1. Напряжение на втором выводе конденсатора 4 продолжает понижаться до напряжения на инверсном выходе бистабильного устройства 1, т.е. до уровня логического "0". Конденсатор 4 зарядился в обратном направлении до Eпит. Импульс со входа 7 установки снимается. Процесс установки триггерного устройства в состояние логической "1" заканчивается. Триггерное устройство поддерживается в состоянии логической "1" уровнем логического "0" с выхода элемента И-НЕ 6.

При поступлении на вход 8 сброса импульса положительной полярности бистабильное устройство 1 переключается в состояние логического "0". При этом на прямом выходе устанавливается уровень логического "0", на инверсном выходе - уровень логической "1".

В момент переключения бистабильного устройства 1 потенциал на выводах конденсатора 4 понижается на величину, равную падению напряжения на защитном диоде, который установлен на входе инвертора 5 и привязан к нулевой шине (См. Цифровые интегральные микросхемы: Справочник/ П.П.Мальцев, Н.С.Долидзе, М. И. Критенко и др. - М.: Радио и связь, 1994, с. 101, рис. 3.12). При этом на втором выводе конденсатора 4 потенциал станет равен минус Uд; а на первом выводе конденсатора 4 - (Eпит - Uд). Состояния инвертора 5 и элемента И-НЕ 6 не изменяются. При этом начинает протекать ток разряда конденсатора 4 через защитный диод, резистор 2 и прямой выход бистабильного устройства 1. Ток, протекающий через резистор 3, незначительный по сравнению с током, протекающим через резистор 2. Напряжение на первом выводе конденсатора 4, а следовательно, и на втором входе элемента И-НЕ 6 начинает понижаться. При достижении указанным напряжением порога срабатывания элемент И-НЕ 6 переключается в состояние логической "1", которая передается на вход бистабильного устройства 1 и подтверждает его переключение в состояние логического "0". Напряжение на первом выводе конденсатора 4 далее понижается до напряжения на прямом выходе бистабильного устройства 1, т.е. до уровня логического "0". Как только напряжение на конденсаторе 4 станет равным минус Uд, заканчивается разряд конденсатора 4 через защитный диод, и конденсатор 4 начинает медленно заряжаться через резисторы 2, 3 с инверсного выхода бистабильного устройства 1 уровнем логической "1". Напряжение на втором выводе конденсатора 4, а следовательно, и на входе инвертора 5 повышается. При достижении указанным напряжением порога срабатывания инвертор 5 переключается в состояние логического "0", который поступает на первый вход элемента И-НЕ 6 и подтверждает его переключение в состояние логической "1". Напряжение на втором выводе конденсатора 4 далее повышается до уровня логической "1". Конденсатор 4 зарядился в обратном направлении до Eпит. Импульс со входа 8 сброса снимается, процесс установки триггерного устройства в состояние логического "0" заканчивается.

В режиме хранения информации конденсатор 4 всегда заряжен в одном или другом направлении. Разряженное состояние конденсатора 4 информирует о переключении триггерного устройства и может быть зафиксировано с помощью устройства 12, выход которого является контрольным выходом 13 триггерного устройства, а входы подключены к выводам конденсатора 4.

Триггерное устройство может переключаться в состояние логического "0" или логической "1". При переключении триггерного устройства в состояние логической "1" на выводах разряженного конденсатора 4 присутствует уровень логической "1". Для выявления этого переключения можно использовать, например, элемент 12 И-НЕ (см. черт.), т.к. присутствие на обоих входах уровня логической "1" переключает элемент 12 И-НЕ в состояние логического "0".

При переключении триггерного устройства в состояние логического "0" на обоих выводах разряженного конденсатора 4 присутствует уровень логического "0". Для выявления этого переключения можно использовать элемент 12 ИЛИ-НЕ, так как присутствие на обоих входах элемента 12 ИЛИ-НЕ уровня логического "0" переключает его в состояние логической "1".

При необходимости выявлять любое переключение триггерного устройства можно использовать элемент 12 "ИСКЛЮЧАЮЩЕЕ ИЛИ", так как присутствие на обоих входах элемента 12 "ИСКЛЮЧАЮЩЕЕ ИЛИ" уровня логического "0" или уровня логической "1" формирует на его выходе уровень логического "0". Переключение триггерного устройства под действием управляющих сигналов является санкционированным, а переключение триггерного устройства под действием помех, без присутствия управляющих сигналов - несанкционированным.

Как видно из описания работы триггерного устройства, введенные в него элемент И-НЕ 6, инвертор 5 и второй резистор 3 позволяют обеспечить возможность выявления несанкционированного переключения триггерного устройства за счет обеспечения дополнительного состояния конденсатора 4.

При этом для установки триггерного устройства при включении питания в исходное состояние логического "0" не требуется формирование специальных сигналов, что способствует упрощению разрабатываемой аппаратуры.

В целях подтверждения осуществимости заявляемого объекта и достижения технического результата в институте построен и испытан лабораторный макет триггерного устройства, выполненный по приведенной на чертеже схеме. Проведенные испытания показали осуществимость заявляемого триггерного устройства и подтвердили его практическую ценность.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТРИГГЕРНОЕ УСТРОЙСТВО | 1996 |

|

RU2123232C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2002 |

|

RU2212095C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 1995 |

|

RU2106742C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2001 |

|

RU2207716C2 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 1999 |

|

RU2180985C2 |

| ЭНЕРГОНЕЗАВИСИМАЯ ЯЧЕЙКА ПАМЯТИ | 1999 |

|

RU2215337C2 |

| ГЕНЕРАТОР ПРЯМОУГОЛЬНЫХ ИМПУЛЬСОВ | 1997 |

|

RU2146075C1 |

| ПОМЕХОСТОЙКОЕ ТРИГГЕРНОЕ УСТРОЙСТВО | 1995 |

|

RU2106056C1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2000 |

|

RU2178617C2 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2001 |

|

RU2211528C2 |

Изобретение относится к импульсной технике. Технический результат заключается в возможности выявления несанкционированного переключения триггерного устройства. Он достигается за счет обеспечения дополнительного состояния конденсатора. Триггерное устройство содержит резистор 2, конденсатор 4, элемент И-ИЕ 6, инвертор 5 и второй резистор 3. Один вывод резистора 3 соединен с инверсным выходом бистабильного устройства 1, другой вывод - с вторым выводом конденсатора 4. Выход элемента 6 соединен с входом бистабильного устройства 1. Второй вход элемента И-НЕ 6 соединен с первым выводом конденсатора 4. 1 ил.

Триггерное устройство, содержащее резистор, первый и второй выводы которого соединены соответственно с первым выводом конденсатора и прямым выходом бистабильного устройства, отличающееся тем, что введены элемент И - НЕ, инвертор и второй резистор, один вывод которого соединен с инверсным выходом бистабильного устройства, другой вывод - с вторым выводом конденсатора и через инвертор - с первым входом элемента И - НЕ, второй вход которого соединен с первым выводом конденсатора, а выход соединен с входом бистабильного устройства.

| ТРИГГЕРНОЕ УСТРОЙСТВО (ЕГО ВАРИАНТЫ) | 1985 |

|

RU1276222C |

| Триггерное устройство (его варианты) | 1982 |

|

SU1045354A1 |

| ЛЕКАРСТВЕННАЯ ФОРМА ДЛЯ ДЕТЕЙ, ОБЛАДАЮЩАЯ ПРОТИВОВОСПАЛИТЕЛЬНЫМ И ЖАРОПОНИЖАЮЩИМ ДЕЙСТВИЕМ | 1998 |

|

RU2155585C2 |

| US 4048521 A, 30.09.77. | |||

Авторы

Даты

1998-12-10—Публикация

1997-03-19—Подача