(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ИСТОЧНИКА ПОСЛЕДОВАТЕЛЬНОСТИ ИМПУЛЬСОВ

1

Изобретение откосится к вычислительной технике и может быть использовано в цифровых вычислительных устройствах.

Известно устройство контроля последовательности импульсов, содержащее элементы HI ИЛИ, триггер и элемент задержки ll .

Недостатками этого устройства являются критичность к параметрам контролируемых импульсов (между фронтами импульсов должны быть интервалы не меньше, чем длительность импульса), а также Невозможность выявить пропадание подряд четного числа импульсов.

Наиболее близким по технической сущности и предложенному является устройство для контроля источника. последовательности импульсов, содержащее два триггера, схему сравнения, элементыИЛИ и исполнительный элемент С21 .

Недостатком этого устройства является низкая надежность контроля, так как контролируется только наличие появления четного или нечетного импульса и не контролируется очередность их следования. Кроме того, из-, за временных сдвигов фронтовсравниваемых импульсов возможна ложная выдача сигнала сбоя при правильном функционировании источника последовательности импульсов.

5 Цель изобретения - повышение надежности контроля.

Поставленная цель достигается тем, что в устройство для контроля источника последовательности импульсов,содержащее триггер,элемент ИЛИ и схему сравнения, введены C4eT4Hk, дешифратор и группа элементов И, а схема сравнения выполнена из триггера, элемента НЕ и элемента И, при

15 этом вход счетчика соединен с первым выходом источника последовательности импульсов, {Разрядные выходы счетчика соединены соответственно с входами дешифратора,выходы которого соединены соответственно с

первыми входами элементов И группы, вторые входы элементов И группы соединены соответственно с группой выходов источника последовательности

25 импульсов, выходы элементов и группы соединены с входами элемента ИЛИ, выход которого соединен с входом установки в ноль триггера схемы сравнения, выход триггера схемы сравнения соединен с первым входом элемента И схеми сравнения, второй вход которого соединен с вторым выходом источника последовательности импульсов, третий вход элемента И схемы сравнения соединен через элемент НВ со входом установки в единицу триггера схемы сравнения и с третьим выходом источника последовательности импульсов, выход элемента И схемы сравнения соединен с входом установки в единицу триггера, вход у становки в ноль которого соединен с шиной Сброс, а выход триггера является выходом сигнала сбоя устройства.

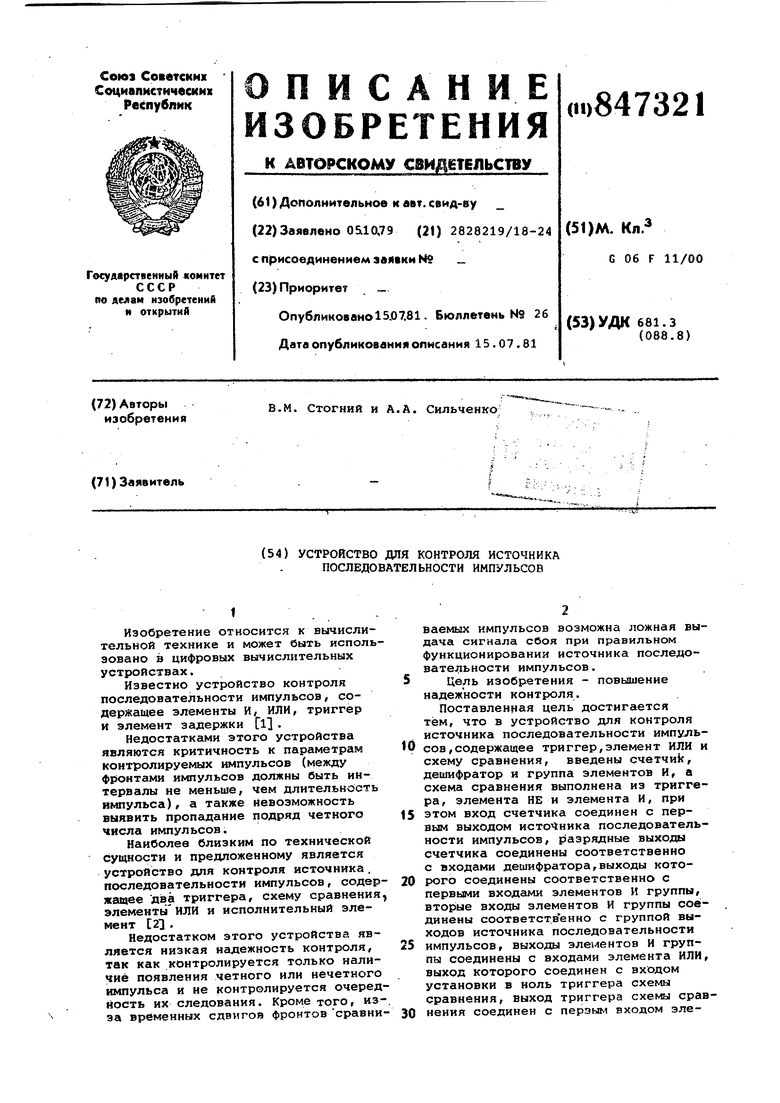

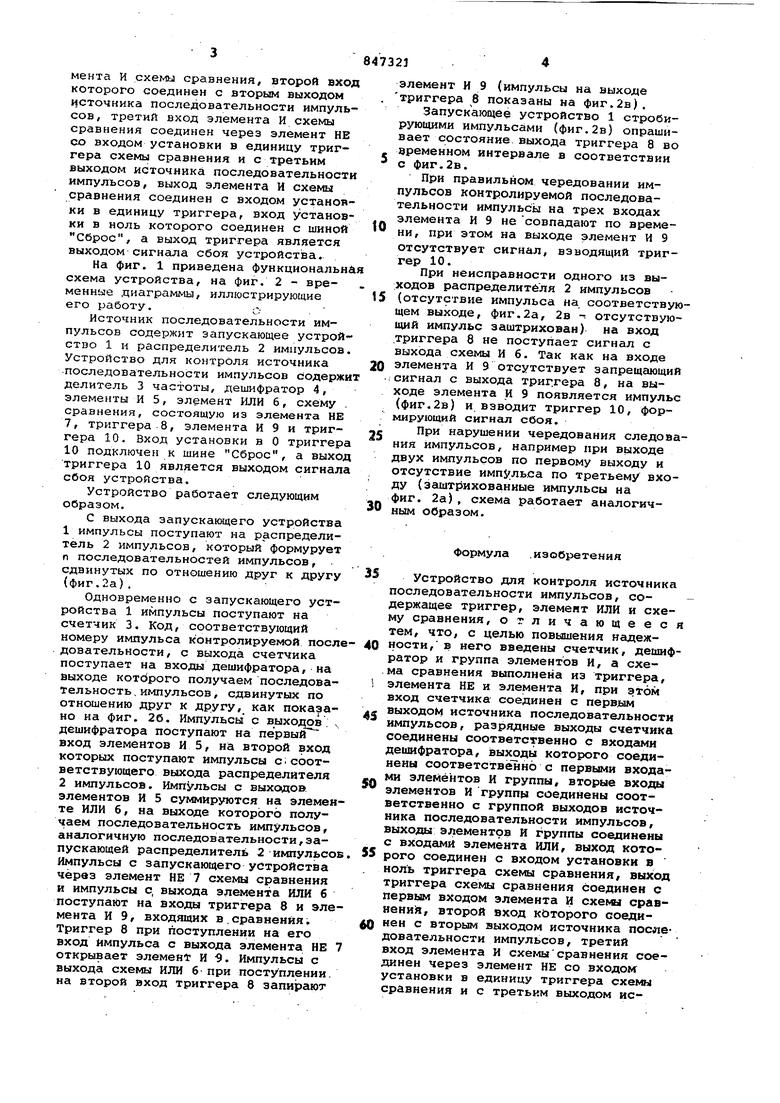

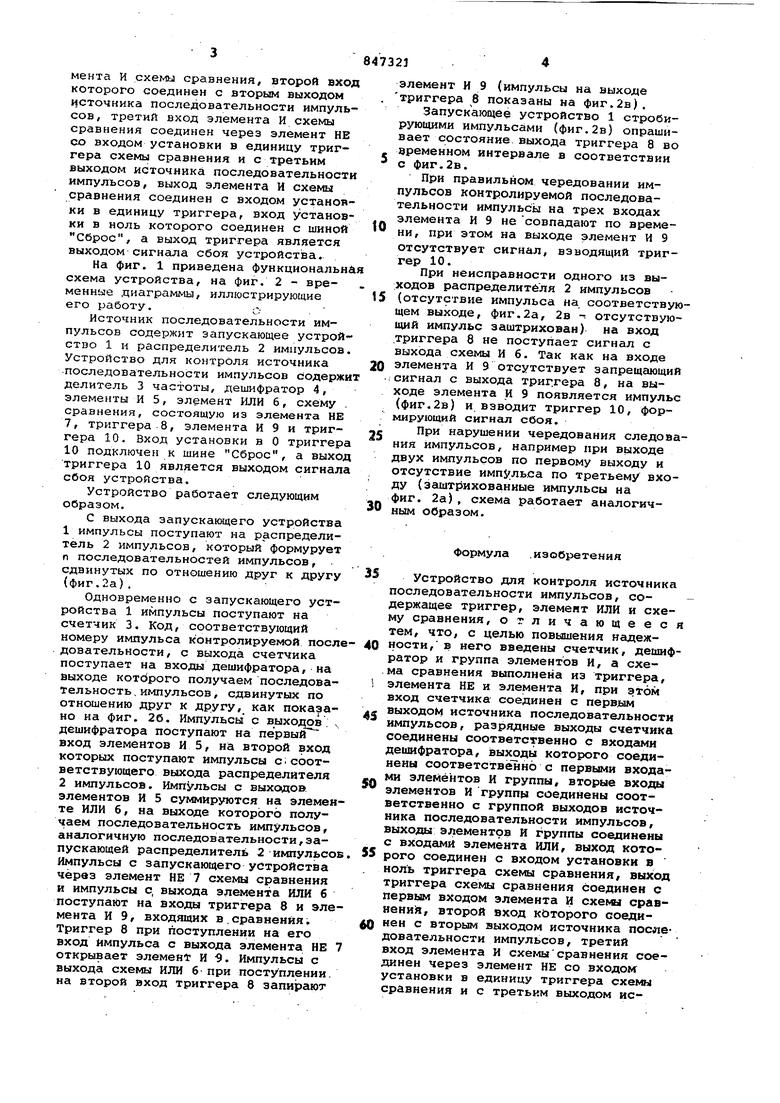

На фиг. 1 приведена функциональна схема устройства, на фиг. 2 - временные диаграммы, иллюстрирующие его работу.о

Источник последовательности импульсов содержит запускающее устройство 1 и распределитель 2 импульсов. Устройство для контроля источника последовательности импульсов содержи делитель 3 частоты, дешифратор 4, элементы И 5, элемент ИЛИ 6, схему . сравнения, состоящую из элемента НЕ 7, триггера 8, элемента И 9 и триггера 10. Вход установки в О триггера 10 подключен к шине Сброс, а выход триггера 10 является выходом сигнала сбоя устройства.

Устройство работает следующим образом.

С выхода запускающего устройства

1импульсы поступают на распределитель 2 импульсов, который формурует п последовательностей импульсов, сдвинутых по отношению друг к другу {фиг.2а).

Одновременно с запускающего устройства 1 импульсы поступают на счетчик 3. Код, соответствующий номеру импульса контролируемой последовательности, с выхода счетчика поступает на входы дешифратора, на выходе котброго получаем последовательность ,импульсов, сдвинутых по отношению друг к другу, как показано на фиг. 26. Импульсы с выхоцоъ ч дешифратора поступают на первый вход элементов И 5, на второй вход которых поступают импульсы ссоответствующего выхода распределителя

2импульсов. Импульсы с выходов элементов И 5 суммируются на элементе ИЛИ 6, на выходе которого получаем последовательность импульсов, анашогичную последовательности,запускающей распределитель 2 импульсо Импульсы с запускающего устройства через элемент НЕ 7 схемы сравнения

и импульсы с, выхода элемента ИЛИ 6 поступают на входы триггера 8 и элемента И 9, входящих в.сравнения; Триггер 8 при поступлении на его вход импульса с выхода элемента НЕ открывает элемент И 9. Импульсы с выхода схемы ИЛИ б при поступлении, на второй вход триггера 8 запирают

элемент И 9 (импульсы на выходе триггера 8 показаны на фиг.2в).

Запускающее устройство 1 стробирующими импульсами (фиг.2в) опрашивает состояние выхода триггера 8 во временном интервале в соответствии с фиг.2в.

При правильном чередовании импульсов контролируемой последовательности импульсы на трех входах элемента И 9 не совпадают по времени, при этом на выходе элемент И 9 отсутствует сигнал, взводящий триггер 10.

При неисправности одного из выходов распределителя 2 импульсов 5 (отсутствие импульса на соответствующем выходе, фиг.2а, 2в - отсутствующий импульс заштрихован) на вход триггера 6 не поступает сигнал с выхода схемы И 6. Так как на входе элемента И 9 отсутствует запрещающий сигнал с выхода триг.гера 8, на выходе элемента И 9 появляется импульс (фиг.2в) и взводит триггер 10, формирующий сигнал сбоя.

При нарушении чередования следования импульсов, например при выходе двух импульсов по первому выходу и отсутствие по третьем/ входу (заштрихованные импульсы на фиг. 2а), схема работает аналогич ным образом.

Формула .изобретения

Устройство для контроля источника последовательности импульсов, содержащее триггер, элемент ИЛИ и схему сравнения, отличающеес тем, что, с целью повышения надежности, в него введены счетчик, дешифратор и группа элементов И, а схема сравнения выполнена из триггера, элемента НЕ и элемента И, при этом вход счетчика соединен с nepajuM выходом источника последовательности импульсов, разрядные выходы счетчика соединены соответственно с входами дешифратора, которого соединены соответственно с первыми входами элементов И группы, вторые входы элементов И группы соединены соответственно с группой выходов источника последовательности импульсов, выходы элементов И группы соединены с входами элемента ИЛИ, выход которого соединен с входом установки в ноль триггера схемы сравнения, выход триггера схемы сравнения соединен с первым входом элемента И схемы сраваенкя, второй вход которого соединен с вторым выходом источника последовательности импульсов, третий вход элемента И схемысравнения соединен через элемент НЕ со входом установки в единицу триггера схемы сравнения и с третьим выходом источника последовательности импульсов, выход элемента И схемы сравне имя соединен с входом установки в едииицу триггера, вход установки в ноль которого соединен с шиной Сброс, а выход триггера является выходом сигнала сбоя устройства.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР W 440665, кл. G 06 F 11/00, 1972.

2.Авторское свидетельство СССР ..О 388262, кл. G 06 F 11/00, 1969 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное оперативное запоминающее устройство | 1988 |

|

SU1559379A1 |

| Устройство для обучения основам вычислительнй техники | 1981 |

|

SU1005156A1 |

| Буферное запоминающее устройство | 1989 |

|

SU1654875A1 |

| Устройство для отладки программ | 1982 |

|

SU1049914A1 |

| Устройство для контроля цифровых объектов | 1982 |

|

SU1072048A1 |

| Устройство для контроля и индикации отказов | 1986 |

|

SU1448339A1 |

| Устройство для ввода информации | 1985 |

|

SU1525697A1 |

| Устройство для индикации | 1978 |

|

SU734755A1 |

| Измерительное устройство с самоконтролем | 1984 |

|

SU1233112A1 |

| МНОГОМЕРНАЯ СИСТЕМА ТЕЛЕМЕХАНИКИ | 1989 |

|

RU2020594C1 |

бых раепре/глитем IУ// М

ff.hat. ffitft/tpppmofla.

L

Выуоанз

n

Betro Tp to

П П n

П

n n

n

П

.П

Авторы

Даты

1981-07-15—Публикация

1979-10-05—Подача