Toe или, третья группа входов которого соединена с группой выходов третьего блока элементов И, первый вход которого соединен с выходом второго элемента НЕ и входом установки в единицу второго триггера, второй вход третьего блока элементов И соединен с выходом четвертого элемента И, входом второго элемента задержки и с вторым входом четвертого блока элементов И, группа входов которого соединена с входами третьего элемента ИЛИ и с выходами второго счетчика, вход установки в ноль которого соединен с выходом второгоэлемента задержки, а счетный вход с выходом третьего элемента задерж4991

ки, вхЬд которого соединен с вторым входом второго блока элементов И и с Выходом третьего элемента И, первый вход которого соединен с выходом первого элемента ИЛИ и с пёрвь|м входом четвертого элемента И, вторЬй вход которого соединен с выходом первого элемента НЕ, вход которого соединен с вторым входом третьего элемента И и с выходом схемы сравнения, первая группа входов которой соединена с группой выходов регистра исполнительного адреса, а вторая группа входов схемы сравнения сое- динена с группой выходов регистра адреса команд и с группой входов второго и третьего блока элементов И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля программ | 1987 |

|

SU1439601A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для проверки полноты тестирования программ | 1989 |

|

SU1693607A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для отладки программ | 1981 |

|

SU980096A1 |

| Устройство для измерения частот появления групп команд | 1988 |

|

SU1578717A1 |

| Устройство для контроля микропроцессорной системы | 1984 |

|

SU1213480A1 |

| Устройство для отладки программ | 1985 |

|

SU1348840A1 |

| Автоматизированная система тестового контроля | 1985 |

|

SU1278857A1 |

| Многоканальное устройство для обмена информацией | 1984 |

|

SU1359781A1 |

Изобретение относится к вычислительной технике, а именно к устройствам для программного управления, . и может быть использовано в ЭВМ для обеспечения отладки- программ, Процесс отладки программ заключается в контроле последовательности чередования исполняемых адресов команд условных и безусловных переходов. Фиксация последовательности адресов команд перехода осуществляется обычно в оперативном запоминающем устройстве (ОЗУ) с последующим их считыванием, анализом и исправлением ошибок в программе.

Известно устройство для отладки программ, содержащее память типа ОЗУ для записи адресов условных и безусловных переходов l.

Недостатком устройства является малая производительность.

Наиболее близким к предлагаемому является устройство для управления памятью, содержащее регистр исполнительного адреса, регистр адреса команд, блок буферных регистров, счетчик, триггер, распределитель, элемент ИЛИ, элементы И, элемент задержки Z ,

л

Однако практически все программы в этом устройстве содержат большое количество циклических участков с разным числом повторения каждого

участка; При ютладкег таких программ на известном устройстве в ОЗУ в процессе прохождения циклическогоучастка записывается один и тот же адрес перехода, что приводит к низкой производительности устройства.

Цель изобретения - увеличение произврдительности при отладке, программ оперативной памяти ЭВМ,

I

Эта цель достигается тем, что в

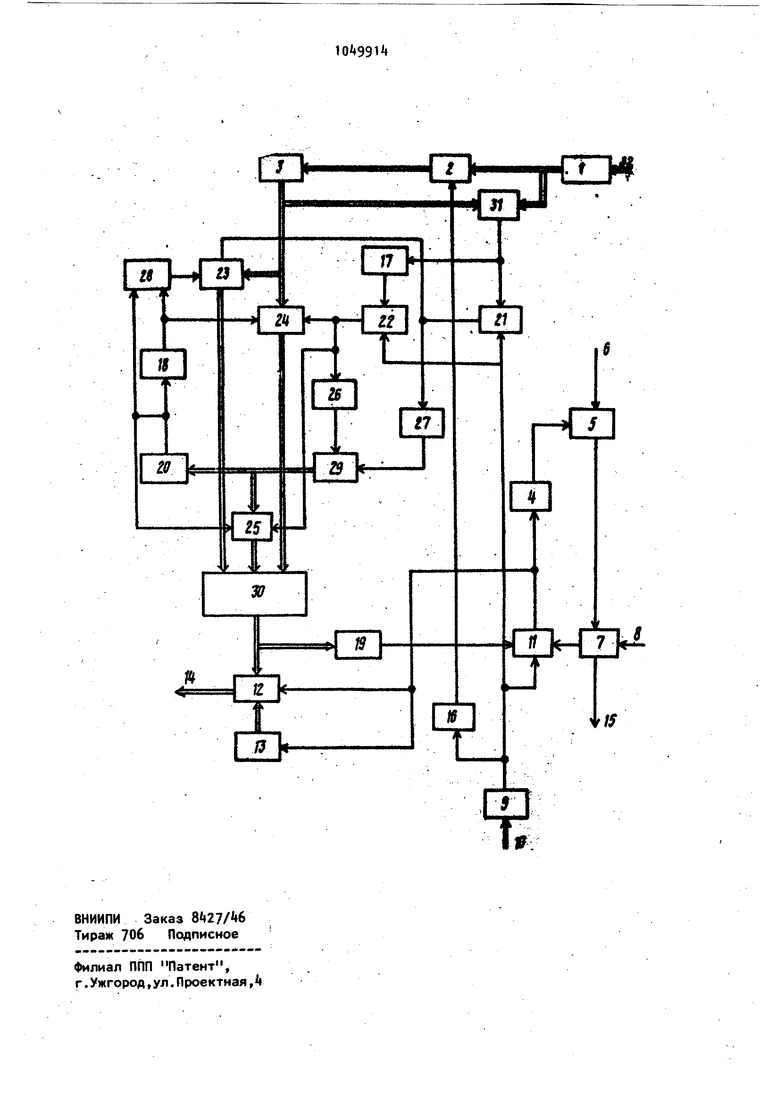

устройство для отладки программ, содержащее регистр исполнительного адреса, первый блок элементов И, ре гистр адреса команд, первый и второй элементы И, первый счетчик, распределитель импульсов, блок буферных регистров, первый триггер, первый элемент задержки, первый элемент ИЛИ, входы которого.соединены с группой входов команд переходов устройства, а выход соединен с входом первого элемента задержки и с первым входом второго элемента И, второй вход которого соединен с инверсным выходом первого триггера, вход установки в ноль которого соединен с устанбвочг ным входом устройства, а прямой выход соединен с выходом прерываний устройства, управляющий вход устрой ства соединен с первым входом, первого лемента И, выход которого соединен с входом установки в единицу пергвого триггера, второй вход первого элементу И соединен с выходом переполнения первого счетчика, счетный вход которого соединен с выходом второго элемента И, с управляющим входом распределителя импульсов и входом записи блока буферных регист ров, группа управляющих входов которого соединена с группой выходов распределителя импульсов, выход блока буферных регистров соединен с группой информационных выходов устройства, группа информационных входов регистра исполнительного адреса соединена с группой адресных входов команд перехода устройства, группа выходов регистра исполнительного адреса соединена с группой входов первого блока элементов И, группа выходов которого соединена с группой информационных входов регистра адреса команд, введены третий и четвертый элементы И, второй, третий и четвертый блоки элементов И, первый и второй элементы НЕ, второй и третий элементы-ИЛИ, второй счетчик, второй и третий элементы задержки, второй триггер, схема сравнения и блок элементов ИЛИ, группа выходов которого соединена с группой информационных входов блока буферных регистров и входами второго элемента ИЛИ, выход которого соединен с третьим входом второго элемента И, первая группа входов блока элементов ИЛИ соединена с группой выходов второго блока элементов И, первый вход которого соединен.с прямым выходом второго триггера, вход устанрв ки в ноль которого соединен с входом второго элемента НЕ, выходом третьего элемента ИЛИ и первым входом четвертого блока элементов И, группа выходов которого соединена с второй группой входов блока элементов ИЛИ, третья группа входов которого соединена с группой выходов третьего блока элементов И, первый вход которого соединен с выходом второго элемен та НЕ и входом установки в единицу второго триггера, вход третье го блока элементов И соединен с выходом четвертого элемента И, входом второго элемента задержки и с вторым входом четвертого блока элементов И, группа входов которого соединена с входами третьего элемента И1Н1 и с выходами второго счетчика, вход установки в ноль которого соединен с выходом второго элемента задержки а счетный вход - с выходом третьего элемента задержки, ход которого соединен с вторым входом второго ,блока элементов И и с выходом третьего элемента И, первый вход которого соединен с выходом первого элеиента ИЛИ и с первым входом четвертого элемента И, второй вход которого соединен с выходом первого элемента НЕ, вход которого соединен с вторым входом третьего элемента И и с выходом схемы сравнения, первая входов которой соединена с группой выходов регистра исполнительного адреса, а вторая группа входов схемы сравнения соединена с группой выходов регистра адреса команд и с группой входов второго и третьего блока элементов И. На чертеже приведена функциональная схема предлагаемого устройства. Устройство содержит регистр 1 исполнительного адреса, блок 2 элементов И, регистр 3 адреса команд, счетчик i. элемент И 5, управляющий вход 6 устройства, триггер 7, вход 8 установки устройства, элемент ИЛИ 9, группу входов 10 команд перехода устройства, элемент И 11, блок 12 буферных регистров, распределитель 13 импульсов, группу информационных выходов Ц устройства, выход 15 прерываний устройства, элемент 1б задержки , элементы НЕ 17 и 18, элементы ИЛИ 19 и 20, элементы И 21 и 22, блоки 23-25 элементов И, элементы 26-27 задержки, триггер 28, счетчик 29, блок 30 элементов ИЛИ, схему 31 сравнения, группу адресных входов 32 команд .перехода. Регистр 1 предназначен для приема, хранения и выдачи п-разрядного кода исполнительного адреса, поступающего параллельным кодом из ЭВМ на группу входов команд перехода. Блок 2 элементов И представляет собой набор п-двухвходовых элементов И, первые входы которых объединены и являются первым входом блока 2. Вторые входы составляют группу входов элемента И. Структура регистра 3 аналогична структуре регистра 1, Счетчик 4 предназначен для счета импульсов, является кольцевым и вырабатывает на своем выходе сигнал при переполнение Блок 12 состоит из регистров, предназначенных для приема, хранения и

выдачи n-разрядного параллельного кода. На каждом разрядном входе всех регистров установлены элемен.ты И на три входа. Первые входы всех элементов И объединены и являются входом записи блока 12. Вторые входы каждых п (по количеству разрядов в регистрах) элементов объединены и образуют группу управляющих входов блока 12. Третьи входы каждого элемента И объединены в труппу информационных входов. Запись кода в определенный регистр блока 12 обеспемивается наличием разрешающих потенциалов на входе записи блока 12 и на определенном входе из группы (т) управляющих входов блока 12 (от распределителя 13 импульсов).

Распределитель 13 импульсов выполнен по одной из классических схем. Количество выходов распределителя m (по числу регистров в блоке 12),обрэзуют группу выходов.

23-25 элементов И представляют собой набор п-трехвходовых элементов И, первые входы которых объединены в первый вход блоков 23 25j объединение вторых входов образует второй вход блоков 23 - 25. Третьи входы элементов И образуют группу входов. Счетчик 29 построен по классической схеме, имеет счетный вход и вход установки в ноль. Съем информации с выходов счетчика - параллельный. Блок 30 элементов ИЛИ представляет собой набор п-трехвходовых элементов ИЛИ. Схема 31 сравнения предназначена для поразрядного сравнения двух параллельных двоичных кодов, поступающих на их группы входов. Сиг нал (логическая единица) на выходе схемы 31 формируется при поразрядном совпадении сравниваемых кодов.

Входы 6 и 8, выход 15 устройства связан с приоритетной системой ЭВМ.

Сигналы (команды перехода) на групу входов 10 устройства поступают с процессора ЭВМ (например, с дешифратора регистра кода операции).

Группа информационных выходов 1 устройства предназначена для перезаписи кодов из регистров блока 12 в ОЗУ ЭВМ.

Время задержки элементов 1б, 26 и 27 задержки выбирается из условия надежного занесения информации в регистр блока 12. При выполнении программ для изменения порядка следования команд используется содержимое регистра 3, где хранится адрес команды перехода. При выполнении программы устройство работает в двух режимах. Пока нет циклического участка в линейном режиме, при появлении циклического участка - в циклическом режиме.

Устройство работает следующим образом.

В исходном положении регистры 1 и 3, счетчики 4 и 29, распределитель 13 импульсов, блок 12 буферных регисров и триггер 7 обнулены. Цепи установки в ноль на чертеже не показаны. Кроме того триггер 28 устанавливается в исходное (единичное) состояние сигналами с выходов обнуленного счетчика 29 через элементы ИЛИ 20, НЕ 18.

Для удобства описания работы устройства вначале рассмотрим его работу в линейном режиме.

В этом режиме изменение порядка следования команд происходит под действием команд условного и безусловного перехода, поступающих с группы входов 10 устройства на элемент ИЛИ 9 и далее с его выхода на входы элементов И 11, 21 и 22 и элементов 16 задержки.

Так как в исходном состоянии в регистре 3 записан нулевой код, а в регистр 1 в процессе подготовки ЭВМ к выполнению команды перехода записывается код адреса команды перехода, то на вь1ходе схемы 31 Сравнения вырабатывается сигнал несравнения - логический ноль, который запрещает прохождение сигнала перехода (логическая единица с вь1хода элемента ИЛИ 9 через элемент И 21, а пройдя через элемент RE 17, разрешает прохождение сигнала перехода через элемент И 22 на второй вход блока 2k элементов И, на первом входе которого присутствует разрешающий потенциал (логическая единица) с выхода элемента НЕ 18 (в исходном состоянии счетчик 29 обнулен, и нулевой код с его выходов поступает на входы элемента ИЛИ 20 и формирует на его выходе и, следовательно, на входе элемента НЕ 18 логический нсяь) В исходном состоянии в регистре 3 записан нулевой код, поэтому на группе выходов блока 2k также присутствует нулевой код, который поступает на третью группу входов блока 30. На других группах входов блока 30 также присутствуют нулевые коды, за счет того, что на первом входе блока 25 элементов И и на втором входе блока 23 элементов И присутствуют запрещающие нулевые сигналы, поступающие соответственно с выхода элемента ИЛИ 20 и с выхода элемента И 21, следо вательно, на группе выходов блока 30 элементов ИЛИ также присутствует нуг левой код, который поступает на входы элемента-ИЛИ 19, формируя на его выходе запрещающий потенциал. Этот сигнал поступает на третий вход элемента И 11 и запрещает прохождение через него сигнала перехода. Поэтому на выходе элемента И 11 не появляется сигнал разрешения записи исходного (нулевого) кода регистра 3 в блок 12 буферных регистров, а в счетчик не добавляется еДиница. Кроме того, сип нал перехода с выхода элемента ИЛИ 9 пройдя элемент 16 задержки, осуществляет перепись содержимого регистра 1 в регистр 3. При реализации следующей команды перехода схема 31 Ьравнения снова вырабатывает сигнал несравнения (логический ноль , который запрещает прохождение сигнала перехода с выхода элемента ИЛИ 9 через элемент И 21. Однако, пройдя элемент НЕ 17, сигнал несравнения разрешает прохождение сигнала перехода через элемент И 22 на второй вход блока 2. Так как на выходе элемента И 21 присутствует нулевой сигнал, то счетчик 29 не изменяет своего состояния, и нулевой код с его выхода через элемент ИЛИ 20 поступает на вход элемента НЕ 18. На выходе элемента НЕ 18 формируется единичный сигнал, который поступает на первый вход блока и разрешает передачу .содержимого регистра 3 (код адреса предыдущей команды перехода) на третьею группу входов блока 30 и далее на группу информационных входов блока 12 и на входы элемента ИЛИ 19. В коде адреса команды всегда присутствует хотя бы одна единица. Поэтому на выходе элемента ИЛИ 19 формируется сигнал, поступающий на третий вход элемента И 11. На втором вхо де элемента И 11 присутствует разрешающий сигнал (логическая единица) с инверсного выхода триггера 7 (триггер 7 в исходном, нулевом состоянии). Следовательно, сигнал перехода проходит на выход элемента И 11 и поступает на управляющий вход распределителя 13 импульсов. При этом на первом выходе из его группы выходов (Появляется единичный сигнал. Кроме того, сигнал ,с выхода элемента И 11 осуществляет прибавление единицы в счетчик и дает разрешение на перепись содержимого регистра 3 (с группы выходов блока 30 элементов или) в регистр блока 12 буферных регистров. Прохождение кодов через блоки 23 и 25 элементов И, как и в первом случае, блокируется сигналами (логические нули) с выходов элементов И 21 и ИЛИ 20 соответственно. Сигнал с выхода элемента 16 задержки осуществляет перепись содержимого регистра 1 в регистр 3 и тем самым подготавливает устройство к обработке следующей Команды условного (безусловного) перехода . Коды адресов команд перехода с регистра 3 переписываются в регистры блока 12, номерй которых определяются сигналом на соответствующем выходе группы выходов распределителя 13 импульсов. Счетчик считает количество реализованных команд переходов и выдает сигнал переполнения при выполнении m команд перехода. Сигнал переполнения поступает на второй вход элемента И 5 и при условии разрешения по входу 6 устройства . поступает на вход триггера 7. С выхода триггера 7 сигнал выдается в приоритетную систему ЭВМ, сообщая с заполнении всех регистров блока 12. Нулевой сигнал с триггера 7 поступает на элемент И 11 и блокирует распределитель 13 импульсов, счетчик и блок 12 буферных регистров. Блокировка обеспечивает сохранение содержимого регистров блока 12 до его переписи через группу выходов 1 устройства в оперативную память ЭВМ. Пос ле переписи содержимого этих регистров в оперативную память ЭВМ триггер 7 сбрасывается i; сигналом по входу 8 и тем самым подготавливает устройство к следующему циклу работы. Предлагаемое устройство работает по описанному алгоритму до циклического участка в программе в частном случае, до конца программы). 9 При наличии циклического участка программы устройство переходит в цик лический режим работы. Для определения правильности прохождения циклического участка необходимо определит количество повторений этого цикличес кого участка. При повторении ЭВМ какого-либо участка программы в регистр 1 повторно заносится код адреса команды перехода, по которой был сделан пере ход при реализации ЭВМ предыдущей ко манды перехода. Поэтому код адреса предыдущей команды перехода, хранящийся в регистре 3, совпадает с кодом адреса следующей команды перехода. В этом случае схема 31 сравнения вырабатывает сигнал сравнения (логическая единица), который разрешает прохождение сигнала перехода с выхода элемента ИЛИ 9 через элемент И 21 и блокирует (через элемент НЕ. 1 прохождение сигнала перехода через элемент И 22. Сигнал с выхода элемента И 21 поступает на вход элемента 27 задерж ки и на второй вход блока 23 элементов И, на первом входе которого также присутствует разрешающий сигна с прямого выхода триггера 28(триггер 28 находится в исходном (единичном состоянии, так как счетчик 29 обнулен). Содержимое регистра 3(код адреса команды перехода циклического участка) через блок 23 элементов И поступает на первую группу входов блока 30 элементов ИЛИ и далее на группу информационных входов блока 1 и входы элемента ИЛИ 13. Блоки 24 и 25 элементов И блокированы сигнало (логический ноль) с выходов элемента И 22 и элемента ИЛИ 20 соответст.венно, поэтому информация на блок 30 поступает только с выходов блока 23. Так как в коде адреса команды пе рехода всегда присутствует хотя бы одна единица, на выходе олемента ИЛИ 19 формируется сигнал (логическая единица) , который поступает на третий вход элемента И 11 и разрешает прохождение сигнала перехода через элемент И 11 на счетны вход счетчика , на вход записи блока 12 и управляющий вход распределителя 13 Сигнал с выхода элемента И 11 осуществляет прибавление единицы в счетчике k, переводит распределител 13 импульсов в следующее положение l И дает разрешение на перепись содержимого регистра 3 в регистр (номер которого определяет распределитель 13 импульсов) блока 12 буферных регистров. Сигнал с выхода элемента 16 задержки дает разрешение на перепись содержимого регистра 1 в регистр 3. Сигнал с выхода элемента 27 задержки приб.авляет единицу в счетчике 29. Так , как счетчик 29 первоначально обнулен, то после прибавления единицы на его выходах формируется отличный от нуля код, который через элементы ИЛИ 20, НЕ 18 блокирует по первому входу блок 2 элементов И и сбрасывает триггер 28, блокируя тем самым по первому входу блок 23 элементов И. Таким образом, произведена запись адреса команды перехода к циклическому участку. При последующих повторениях этого же участка программы информация в блок 12 не поступает, так как блоки 23, 2k и 25 элементов И блокированы. На счетный вход счетчика не поступают единицы, так как элемент И 11 блокирован сигналом (логический ноль) с выхода элемента ИЛИ 19. Счетчик 29 считает количество реализованных повторений (циклов} данного участка. После прохождения циклического участка программы в регистр 1 заносится код адреса очередной команды перехода. Схема 31 сравнения в этом случае формирует на своем выходе сигнал несравнения, который блокирует элемент И 21 и через элемент НЕ 17 разрешает прохождение очередного сигнала перехода (с выхода элемента ИЛИ 9) на выход элемента И 22. Сигнал с выхода элемента И 22 разрешает прохождение содержимого счетчика 29 (количество повторений циклическогоучастка) через блок 25 элементов Ни далее через блок 30 злементов ИЛИ на группу информационных входов блока 12 и входы элемента ИЛИ 19. Сигнал с выхода элемента ИЛИ 19 разрешает прохождение сигнала перехода через элемент И 11, Сигнал с выхода элемента И 11 производит перевод распределителя 13 в следующее положение, осуществляет прибавление единицы в счетчике t и переписывает содержимое счетчика 29 (с группы выходов блока 30) в регистр (номер которого определяет распределителЬг 13} блока 12 буферных регистров.

с выхода элемента И 22, пройдя элемент 26 задержки, обнуляет счетчик 29. Если счетчик 29 заполняется до окончания повторений участка программ, то при поступлении на rpyrtпу входов 10 устройства очередного сигнала перехода счетчик 29 обнуля-, ется (схема 31 сравнения вырабатывает сигнал сравнения и элемент И 21 открыт, и нулевой код на группе ВЫ ходов его через элементы ИЛИ 20, НЕ 18 устанавливает триггер 28 а единичное состояние. Сигнал с прямого: выхода триггера 28 разрешает перезапись содержимого регистра 3 через блоки 23 и 30 в блок 12 по ранее описанному алгоритму. Содержание счетчика k при этом увеличивается иа единицу. Следовательно, в блок 12, а затем ив память ЭВМ повторно записывается адрес команды перехода к :

циклическому участку. Количество повторов участка программы в этом случае равно сумме максимально возможнЬго кода счетчика 29 и текущего кода счетчика 29 после прохождения циклич 1Ск6го участка программы.

Таким образом, устройство представляет эффективное и оперативное средство фиксации последовательности адресов реализуемых команд перехода в процессе выполнения программы с автоматическим подсчетом числа повторений циклических участков в про- . грамме и позволяет исключить повторную запись в оперативную память адресов команд переходов циклических участков. Тем самым достигается большая производительность предлагаемого устройства по сравнению с известным. .

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США N-3673573, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Контрольный висячий замок в разъемном футляре | 1922 |

|

SU1972A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Фальцовая черепица | 0 |

|

SU75A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-10-23—Публикация

1982-07-15—Подача