Пзобретение относится к области автоматики и вычислительной техники и может быть использовано при приеме и обработке информации от оптоэлектронных датчиков, в автоматических системах управления фокусированием изображения в оптических устройствах,

Целью изобретения является упрощение устройства за счет уменьшения объема хранимой информации.

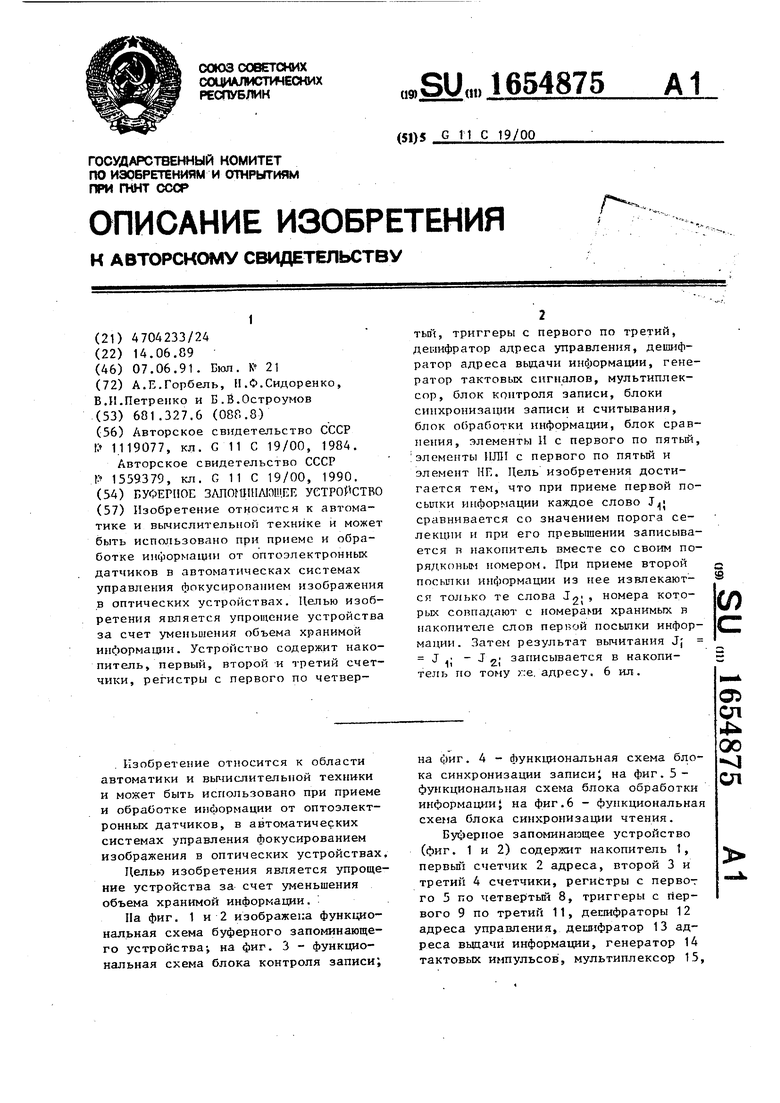

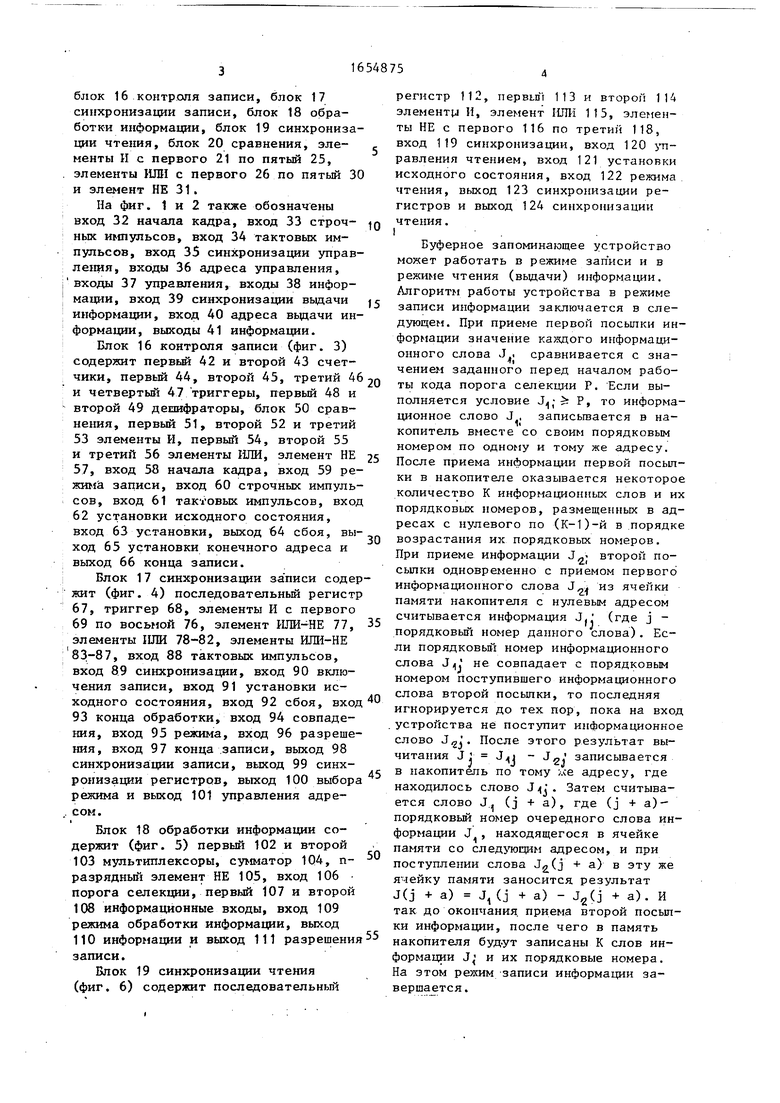

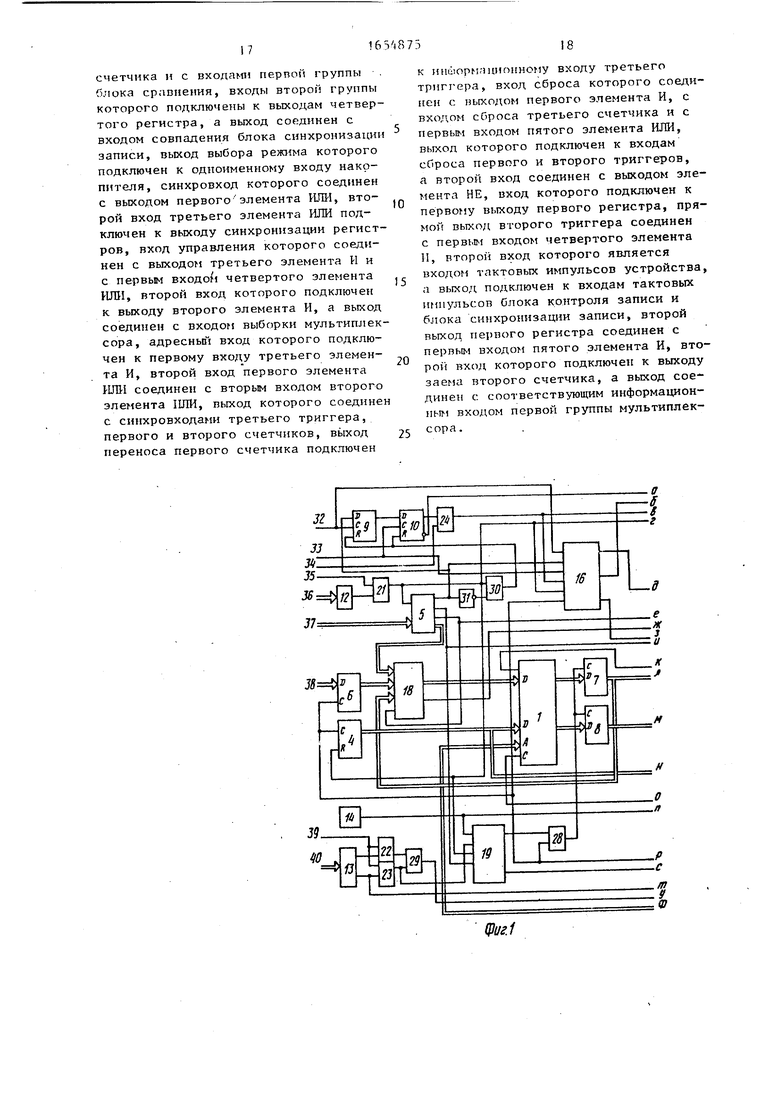

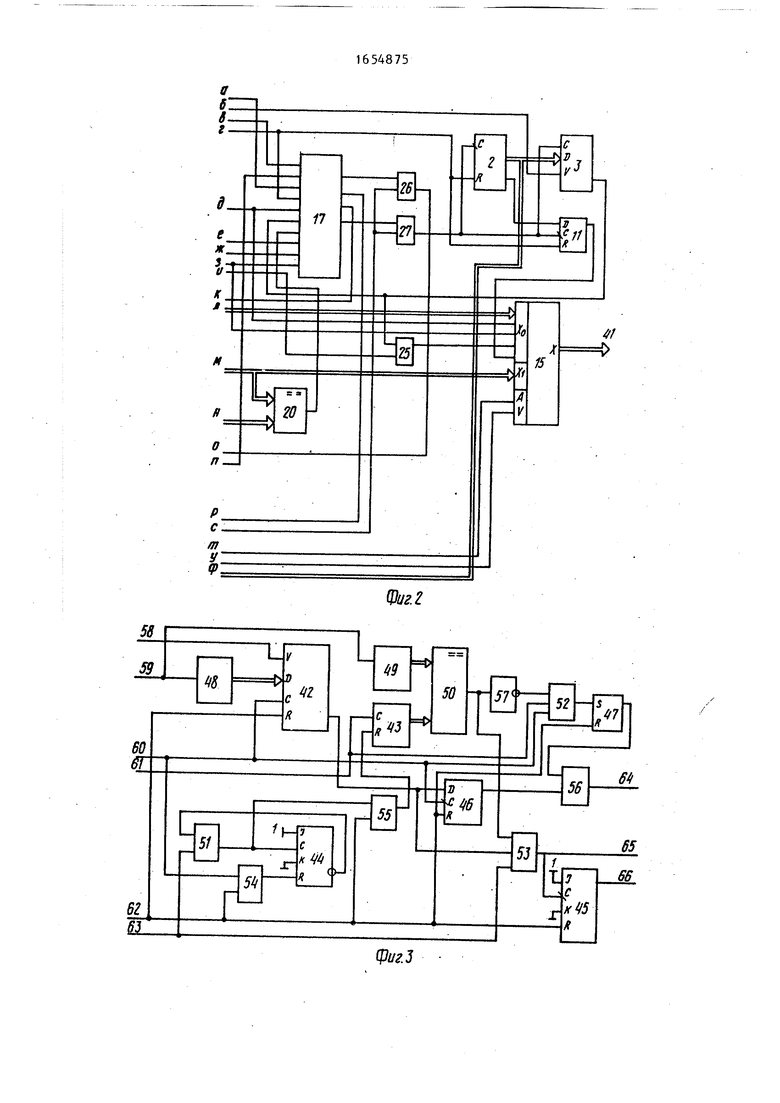

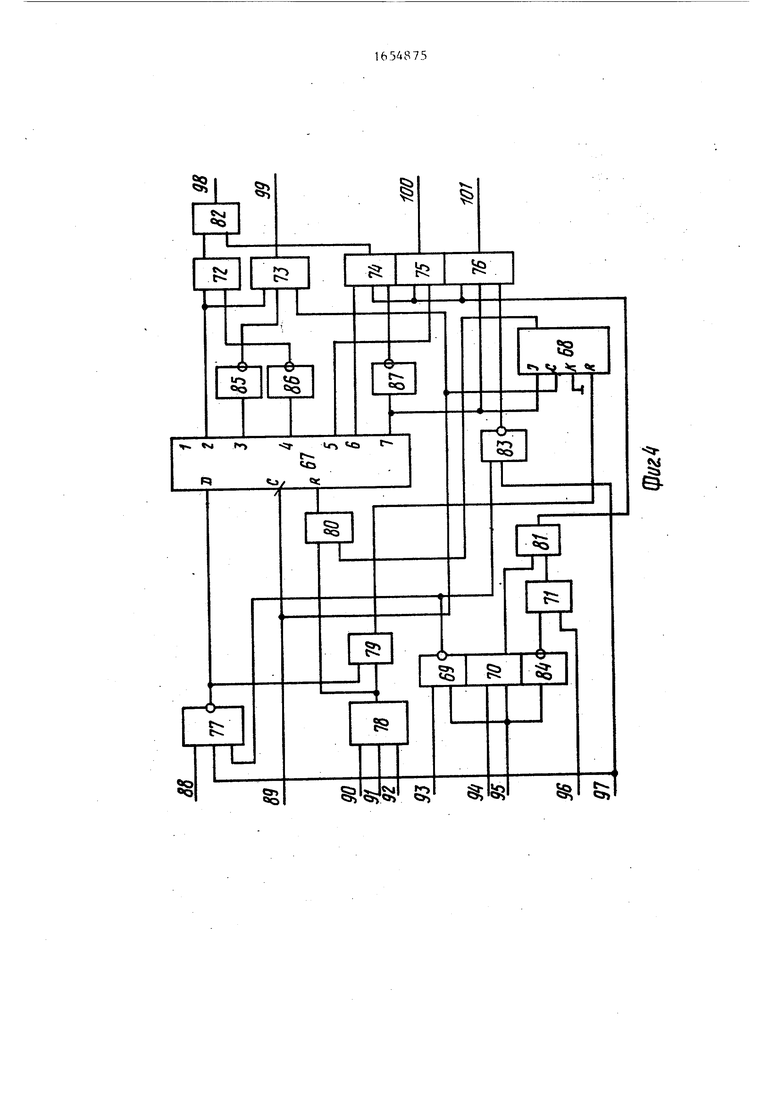

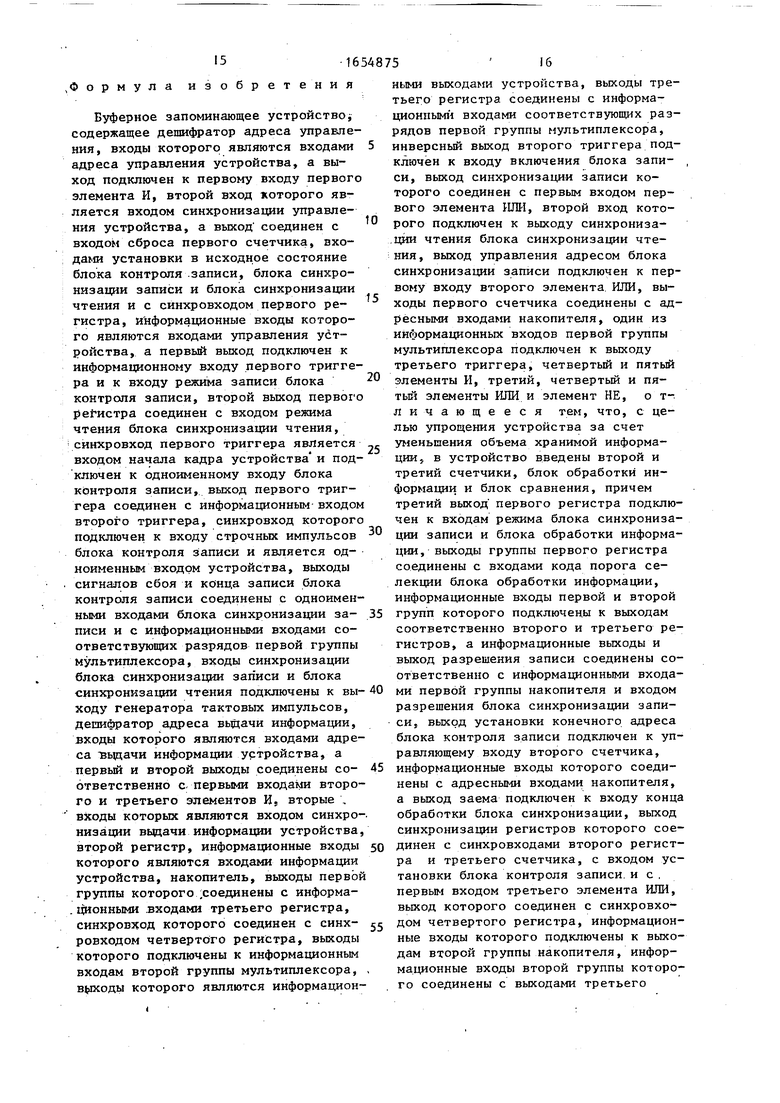

На фиг. 1 и 2 изображена функциональная схема буферного запоминающего устройства-, на фиг. 3 - функциональная схема блока контроля записи;

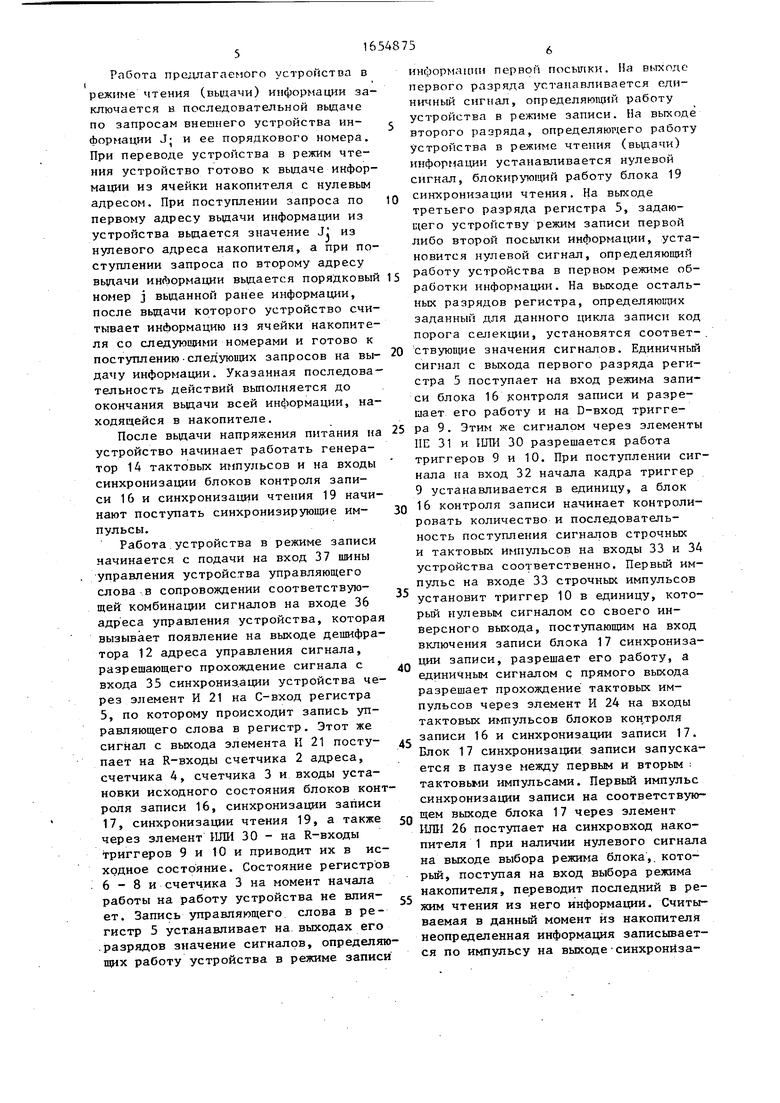

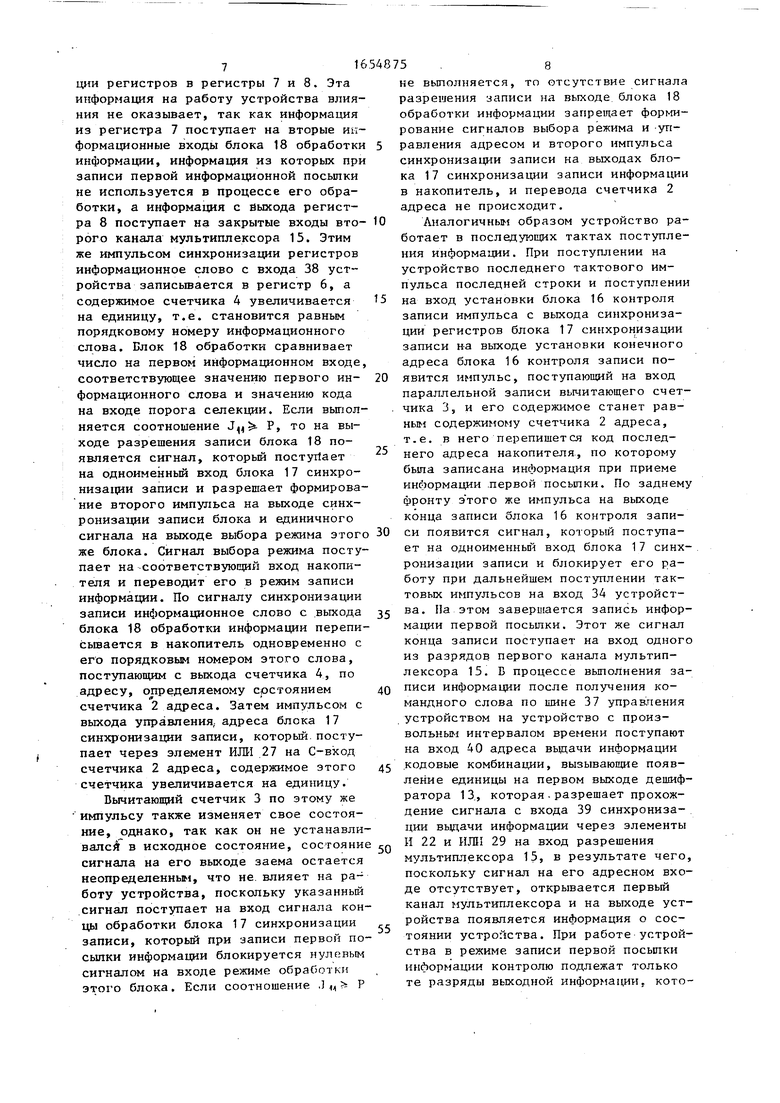

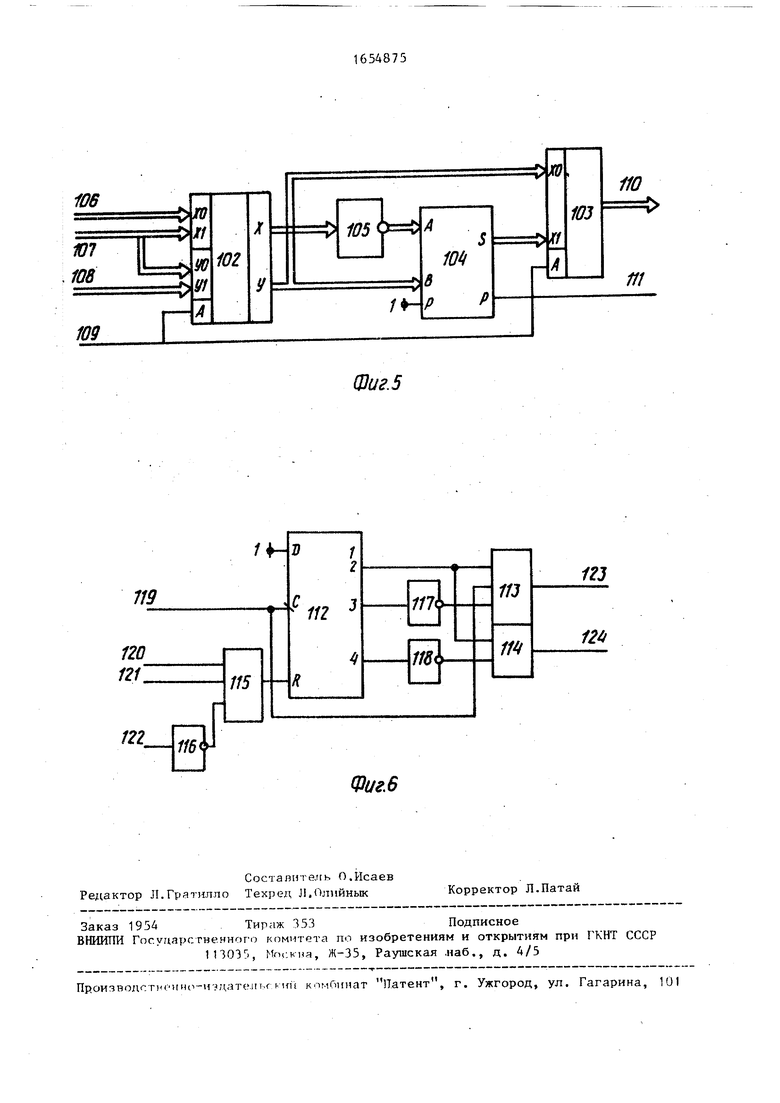

на фиг. 4 - функциональная схема блока синхронизации записи; на фиг. 5- функциональная схема блока обработки информации на фиг.6 - функциональная схема блока синхронизации чтения.

Буферное запоминающее устройство (фиг. 1 и 2) содержит накопитель 1, первый счетчик 2 адреса, второй 3 и третий 4 счетчики, регистры с перво-т го 5 по четвертый 8, триггеры с первого 9 по третий 11, дешифраторы 12 адреса управления, дешифратор 13 адреса выдачи информации, генератор 14 тактовых импульсов, мультиплексор 15,

С5

сп

Јь

оо

СЛ

блок 16 контроля записи, блок 17 синхронизации записи, блок 18 обработки информации, блок 19 синхронизации чтения, блок 20 сравнения, элементы И с первого 21 по пятый 25, элементы ИЛИ с первого 26 по пятый 30 и элемент НЕ 31.

На фиг. 1 и 2 также обозначены вход 32 начала кадра, вход 33 строчных импульсов, вход ЗА тактовых импульсов, вход 35 синхронизации управления, входы 36 адреса управления, входы 37 управления, входы 38 информации, вход 39 синхронизации выдачи информации, вход 40 адреса выдачи информации, выходы 41 информации.

Блок 16 контроля записи (фиг. 3) содержит первый 42 и второй 43 счетчики, первый 44, второй 45, третий 46 и четвертый 47 триггеры, первый 48 и второй 49 дешифраторы, блок 50 сравнения, первый 51, второй 52 и третий 53 элементы И, первый 54, второй 55 и третий 56 элементы ИЛИ, элемент НЕ 57, вход 58 начала кадра, вход 59 режима записи, вход 60 строчных импульсов, вход 61 тактовых импульсов, вход 62 установки исходного состояния, вход 63 установки, выход 64 сбоя, выход 65 установки конечного адреса и выход 66 конца записи.

Блок 17 синхронизации записи содержит (фиг. 4) последовательный регистр 67, триггер 68, элементы И с первого 69 по восьмой 76, элемент ИЛИ-НЕ 77, элементы ИЛИ 78-82, элементы ИЛИ-НЕ 83-87, вход 88 тактовых импульсов, вход 89 синхронизации, вход 90 включения записи, вход 91 установки исходного состояния, вход 92 сбоя, вход 93 конца обработки, вход 94 совпадения, вход 95 режима, вход 96 разрешения, вход 97 конца записи, выход 98 синхронизации записи, выход 99 синхронизации регистров, выход 100 выбора режима и выход 101 управления адресом.

Блок 18 обработки информации содержит (фиг. 5) первый 102 и второй 103 мультиплексоры, сумматор 104, п- разрядный элемент НЕ 105, вход 106 порога селекции, первый 107 и второй 108 информационные входы, вход 109 режима обработки информации, выход 110 информации и выход 111 разрешения записи.

Блок 19 синхронизации чтения (фиг. 6) содержит последовательный

0

0

5

0

5

0

5

регистр 112, первый 113 и второй 114 элементу И, элемент ИЛИ 115, элементы НЕ с первого 116 по третий 118, вход 119 синхронизации, вход 120 управления чтением, вход 121 установки исходного состояния, вход 122 режима чтения, выход 123 синхронизации регистров и выход 124 синхронизации

чтения. I

Буферное запоминающее устройство может работать в режиме записи и в режиме чтения (выдачи) информации. Алгоритм работы устройства в режиме записи информации заключается в следующем. При приеме первой посылки информации значение каждого информационного слова J сравнивается с значением заданного перед началом работы кода порога селекции Р. Если выполняется условие Р, то информационное слово J , записывается в на- ii

копитель вместе со своим порядковым номером по одному и тому же адресу. После приема информации первой посылки в накопителе оказывается некоторое количество К информационных слов и их порядковых номеров, размещенных в адресах с нулевого по (К-1)-й в порядке возрастания их порядковых номеров. При приеме информации второй посылки одновременно с приемом первого информационного слова J. из ячейки памяти накопителя с нулевым адресом считывается информация J. (где j - порядковый номер данного слова). Если порядковый номер информационного слова J,, не совпадает с порядковым номером поступившего информационного слова второй посылки, то последняя игнорируется до тех пор, пока на вход устройства не поступит информационное слово . После этого результат вычитания J : - J2. записывается в накопитель по тому /.се адресу, где находилось слово J(j. Затем считывается слово J,| (j + а), где (j + а)- порядковый номер очередного слова информации J , находящегося в ячейке памяти со следующим адресом, и при поступлении слова J(j + а) в эту же ячейку памяти заносится результат J(j + а) JA(j + а) - Je(j + а). И так до окончания приема второй посылки информации, после чего в память накопителя будут записаны К слов информации Jx и их порядковые номера. На этом режим записи информации завершается.

10

Работа предлагаемого устройства в I

режиме чтения (выдачи) информации заключается в последовательной вьщаче по запросам внешнего устройства ин- Аормации J; и ее порядкового номера. При переводе устройства в режим чтения устройство готово к выдаче информации из ячейки накопителя с нулевым адресом. При поступлении запроса по первому адресу выдачи информации из устройства выдается значение Ji из нулевого адреса накопителя, а при поступлении запроса по второму адресу выдачи информации выдается порядковый 15 номер j выданной ранее информации, после выдачи которого устройство считывает информацию из ячейки накопителя со следующими номерами и готово к поступлению-следующих запросов на выдачу информации. Указанная последовательность действий выполняется до окончания выдачи всей информации, находящейся в накопителе.

20

информации первой посыпки. На выходе первого разряда устанавливается единичный сигнал, определяющий работу устройства в режиме записи. На выходе второго разряда, определяющего работу устройства в режиме чтения (выдачи) информации устанавливается нулевой сигнал, блокирующий работу блока 19 синхронизации чтения. На выходе третьего разряда регистра 5, задающего устройству режим записи первой либо второй посылки информации, установится нулевой сигнал, определяющий работу устройства в первом режиме обработки информации. На выходе остальных разрядов регистра, определяющих заданный для данного цикла записи код порога селекции, установятся соответствующие значения сигналов. Единичный сигнал с выхода первого разряда регистра 5 поступает на вход режима записи блока 16 контроля записи и разрешает его работу и на D-вход триггеПосле выдачи напряжения питания на 25 ра 9. Этим же сигналом через элементы устройство начинает работать генера- 11С 1 и ИЛИ 30 разрешается работа

триггеров 9 и 10. При поступлении сигнала на вход 32 начала кадра триггер 9 устанавливается в единицу, а блок 16 контроля записи начинает контролировать количество и последовательность поступления сигналов строчных и тактовых импульсов на входы 33 и 34 устройства соответственно. Первый импульс на входе 33 строчных импульсов установит триггер 10 в единицу, который нулевым сигналом со своего инверсного выхода, поступающим на вход включения записи блока 17 синхронизации записи, разрешает его работу, а единичным сигналом с прямого выхода разрешает прохождение тактовых импульсов через элемент И 24 на входы тактовых импульсов блоков контроля записи 16 и синхронизации записи 17. Блок 17 синхронизации записи запускается в паузе между первым и вторым тактовыми импульсами. Первый импульс синхронизации записи на соответствующем выходе блока 17 через элемент ИЛИ 26 поступает на синхровход накопителя 1 при наличии нулевого сигнала на выходе выбора режима блока, который, поступая на вход выбора режима накопителя, переводит последний в режим чтения из него информации. Считываемая в данный момент из накопителя неопределенная информация записывается по импульсу на выходесинхронйзатор 14 тактовых импульсов и на входы синхронизации блоков контроля записи 1 6 и синхронизации чтения 19 начинают поступать синхронизирующие им- пульсы.

Работа устройства в режиме записи начинается с подачи на вход 37 шины управления устройства управляющего слова в сопровождении соответствую- щей комбинации сигналов на входе 36 адреса управления устройства, которая вызывает появление на выходе дешифратора 12 адреса управления сигнала, разрешающего прохождение сигнала с входа 35 синхронизации устройства через элемент И 21 на С-вход регистра 5, по которому происходит запись управляющего слова в регистр. Этот же сигнал с выхода элемента И 21 посту- пает на R-входы счетчика 2 адреса, счетчика 4, счетчика 3 и входы установки исходного состояния блоков контроля записи 16, синхронизации записи 17, синхронизации чтения 19, а также через элемент ИЛИ 30 - на R-входы триггеров 9 и 10 и приводит их в исходное состояние. Состояние регистров 6 - 8 и счетчика 3 на момент начала работы на работу устройства не влия- ет. Запись управляющего слова в регистр 5 устанавливает на выходах его разрядов значение сигналов, определяющих работу устройства в режиме записи

5

0

информации первой посыпки. На выходе первого разряда устанавливается единичный сигнал, определяющий работу устройства в режиме записи. На выходе второго разряда, определяющего работу устройства в режиме чтения (выдачи) информации устанавливается нулевой сигнал, блокирующий работу блока 19 синхронизации чтения. На выходе третьего разряда регистра 5, задающего устройству режим записи первой либо второй посылки информации, установится нулевой сигнал, определяющий работу устройства в первом режиме обработки информации. На выходе остальных разрядов регистра, определяющих заданный для данного цикла записи код порога селекции, установятся соответствующие значения сигналов. Единичный сигнал с выхода первого разряда регистра 5 поступает на вход режима записи блока 16 контроля записи и разрешает его работу и на D-вход триггера 9. Этим же сигналом через элементы 11С 1 и ИЛИ 30 разрешается работа

триггеров 9 и 10. При поступлении сигнала на вход 32 начала кадра триггер 9 устанавливается в единицу, а блок 16 контроля записи начинает контролировать количество и последовательность поступления сигналов строчных и тактовых импульсов на входы 33 и 34 устройства соответственно. Первый импульс на входе 33 строчных импульсов установит триггер 10 в единицу, который нулевым сигналом со своего инверсного выхода, поступающим на вход включения записи блока 17 синхронизации записи, разрешает его работу, а единичным сигналом с прямого выхода разрешает прохождение тактовых импульсов через элемент И 24 на входы тактовых импульсов блоков контроля записи 16 и синхронизации записи 17. Блок 17 синхронизации записи запускается в паузе между первым и вторым тактовыми импульсами. Первый импульс синхронизации записи на соответствующем выходе блока 17 через элемент ИЛИ 26 поступает на синхровход накопителя 1 при наличии нулевого сигнала на выходе выбора режима блока, который, поступая на вход выбора режима накопителя, переводит последний в режим чтения из него информации. Считываемая в данный момент из накопителя неопределенная информация записывается по импульсу на выходесинхронйза716

ции регистров в регистры 7 и 8. Эта информация на работу устройства влияния не оказывает, так как информация из регистра 7 поступает на вторые информационные входы блока 18 обработки информации, информация из которых при записи первой информационной посыпки не используется в процессе его обработки, а информация с выхода регистра 8 поступает на закрытые входы вто- рого канала мультиплексора 15. Этим же импульсом синхронизации регистров информационное слово с входа 38 устройства записывается в регистр 6, а содержимое счетчика 4 увеличивается на единицу, т.е. становится равным порядковому номеру информационного слова. Блок 18 обработки сравнивает число на первом информационном входе, соответствующее значению первого ин- формационного слова и значению кода на входе порога селекции. Если выпол

няется соотношение P, то на выходе разрешения записи блока 18 появляется сигнал, который поступает на одноименный вход блока 17 синхронизации записи и разрешает формирование второго импульса на выходе синхронизации записи блока и единичного

0

5

не выполняется, то отсутствие сигнала разрешения записи на выходе блока 18 обработки информации запрещает формирование сигналов выбора режима и управления адресом и второго импульса синхронизации записи на выходах блока 17 синхронизации записи информации в накопитель, и перевода счетчика 2 адреса не происходит.

Аналогичным образом устройство работает в последующих тактах поступления информации. При поступлении на устройство последнего тактового импульса последней строки и поступлении на вход установки блока 16 контроля записи импульса с выхода синхронизации регистров блока 17 синхронизации записи на выходе установки конечного адреса блока 16 контроля записи появится импульс, поступающий на вход параллельной записи вычитающего счетчика 3, и его содержимое станет равным содержимому счетчика 2 адреса, т.е. в него перепишется код последнего адреса накопителя, по которому была записана информация при приеме информации первой посыпки. По заднему фронту этого же импульса на выходе конца записи блока 16 контроля запи

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное оперативное запоминающее устройство | 1988 |

|

SU1559379A1 |

| Устройство для сопряжения телеграфных линий связи с ЦВМ | 1988 |

|

SU1603392A1 |

| Буферное запоминающее устройство | 1990 |

|

SU1833918A1 |

| Устройство для обмена данными между источником и приемником информации | 1988 |

|

SU1557566A1 |

| Устройство для ввода-вывода информации | 1984 |

|

SU1246103A2 |

| Устройство для сопряжения абонентов с цифровой вычислительной машиной | 1985 |

|

SU1277123A1 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Буферное запоминающее устройство | 1988 |

|

SU1583938A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при приеме и обработке информации от оптоэлектронных датчиков в автоматнческах системах управления фокусиропанием изображения в оптических устройствах. Цепью изобретения является упрощение устройства за счет уменьшения объема хранимой информации. Устройство содержит накопитель, первый, второй и третий счетчики, регистры с первого по четвертый, триггеры с первого по третий, дешифратор адреса управления, дешифратор адреса выдачи информации, генератор тактовых сигналов, мультиплексор, блок контроля записи, блоки синхронизации записи и считывания, блок обработки информации, блок сравнения, элементы И с первого по пятый, элементы ИЛИ с первого по пятый и элемент НЕ. Цель изобретения достигается тем, что при приеме первой посылки информации каждое слово J сравнивается со значением порога селекции и при его превышении записывается п накопитель вместе со своим порядковым номером. При приеме второй посылки информации из нее извлекаются только те слова J 2 номера которых совпадают с номерами хранимых в накопителе слов первой посыпки информации. Затем результат вычитания J: S (Л - sJ - J записывается в накопиli - 2i тель по тому ке адресу. 6 ил.

35

40

сигнала на выходе выбора режима этого 30 си появится сигнал, который поступает на одноименный вход блока 17 синхронизации записи и блокирует его работу при дальнейшем поступлении тактовых импульсов на вход 34 устройства. На этом завершается запись информации первой посылки. Этот же сигнал конца записи поступает на вход одного из разрядов первого канала мультиплексора 15. Б процессе выполнения записи информации после получения командного слова по шине 37 управления устройством на устройство с произвольным интервалом времени поступают на вход 40 адреса выдачи информации кодовые комбинации, вызывающие появление единицы на первом выходе дешифратора 13, котораяразрешает прохождение сигнала с входа 39 синхронизации выдачи информации через элементы И 22 и ИЛИ 29 на вход разрешения мультиплексора 15, в результате чего, поскольку сигнал на его адресном входе отсутствует, открывается первый канал мультиплексора и на выходе устройства появляется информация о состоянии устройства. При работе устройства в режиме записи первой посыпки информации контролю подлежат только те разряды выходной информации, котоже блока. Сигнал выбора режима поступает на соответствующий вход накопителя и переводит его в режим записи информации. По сигналу синхронизации записи информационное слово с выхода блока 18 обработки информации переписывается в накопитель одновременно с его порядковым номером этого слова, поступающим с выхода счетчика 4, по адресу, определяемому состоянием счетчика 2 адреса. Затем импульсом с выхода управления, адреса блока 17 синхронизации записи, который поступает через элемент ИЛИ 27 на С-вход счетчика 2 адреса, содержимое этого счетчика увеличивается на единицу.

Вычитающий счетчик 3 по этому же импульсу также изменяет свое состояние, однако, так как он не устанавливался в исходное состояние, состояние сигнала на его выходе заема остается неопределенным, что не влияет на работу устройства, поскольку указанный сигнал поступает на вход сигнала концы обработки блока 17 синхронизации записи, который при записи первой посылки информации блокируется нулевым сигналом на входе режиме обработки этого блока. Если соотношение Л „ Р

45

50

55

рые отражают наличие или отсутствие

сигналов конца записи, сбоя и переполнения счетчика адреса.

Появление в разряде, соответствующем сигналу крица записи, единицы соответствует окончанию записи.

Если в процессе записи произошло нарушение количества либо последовательности поступления строчных и тактовых импульсов на входах 33 и 34 устройства, то на выходе сбоя блока

16контроля записи появится сигнал, по которому блокируется работа блока

17синхронизации записи и прекращается прием информации, и на выходе 41 в соответствующем разряде появится единичный сигнал, сообщающий о сбое в приеме информации.

Если в процессе записи информации первой посыпки в ней окажется такое количество информационных слов, значение которых P, что емкости накопителя не хватит для их размещения, то при переполнении счетчика 2 адреса на его выходе переноса появится единичный сигнал, который разрешит , установку триггера 11 по следующему импульсу управления адресом на выходе блока 17 синхронизации записи в единицу, и в соответствующем разряде выходной информации появится единица - сообщение об аварийном переполнении памяти.

Перед приемом информации второй посыпки на входы 37 шины управления поступает управляющее слово в сопровождении адресных сигналов на входе 36 и сигнала синхронизации управления на входе 35 устройства и записывается регистр 5 аналогично описанному. Значение разрядов управляющего слова соответствует значению разрядов управляющего слова при приеме информации первой посыпки за исключением того, что в третьем разряде, определяющем режим обработки информации (прием первой или второй информационной посыпки) , устанавливается единица, а значение разрядов кода порога селекции может быть любым, так как этот код при приеме информации второй посыпки в ее обработке не участвует. Сигнал с выхода элемента И 21, по которому записывается управляющее слово в регистр 5, как и в первом режиме записи устанавливает все функциональные узлы устройства, кроме счетчика 3 и регистров 6 - 8, в исходное состоя

5

0

5

0

5

0

5

0

5

ние. В счетчике 3 остается записанным код адреса последней ячейки накопителя, в которую была занесена информация при записи первой информационной посылки, а состояние регистров 6 - 8 на работу устройства не влияет. Работа устройства при приеме информации второй посыпки аналогична его работе при приеме информации первой посыпки.

Информация второй посылки поступает на вход 38 устройства так же, как и информация первой посылки. Работа устройства при приеме информации первой посылки,за исключением того, что единичный сигнал с выхода третьего разряда регистра 5 поступает на входы рекима обработки информации блоков синхронизации записи 17 и обработки информации 18 и переводит их во второй режим обработки информации.

После поступления первого информационного слова на вход 38 устройства на выходе синхронизации записи блока 17 синхронизации записи появляется сигнал, по которому происходит считывание информации из нулевого адреса накопителя 1, так как накопитель находится в режиме считывания информации из-за наличия на его входе выбора режима нулевого сигнала с одноименного выхода блока 17 синхронизации записи. Затем на выходе синхронизации регистров этого же блока появляется импульс, по которому в регистр 6 записывается первое слово второй посылки, а в регистры 7 и 8 - содержимое ячейки накопителя с нулевым адресом - первое слово из первой посылки, значение которого превысило значение порога селекции, и его порядковый номер. Этим импульсом содержимое счетчика 4 увеличивается на единицу. Если значение содержимого счетчика 4 и регистра 8 совпадают, то на выходе блока 20 сравнения появляется единичный сигнал, который поступает на вход совпадения блока 17 синхронизации записи. Содержимое регистров 6 и 7 поступает на первый и второй информационные входы блока 18 обработки информации, на выходе которого появля- ется разность значений соответствую-, щих слов из первой и второй посылки. Поступление сигнала на вход совпадения блока 17 синхронизации записи ,

разрешает формирование на его выхода единичных сигналов выбора режима, который переводит накопитель 1 в режим записи, и синхронизации записи, по которому в накопитель по нулевому адресу записывается в разряды информации разигость информационных слов с выхода блока 18 обработки информации а с выходов счетчика 4 в разряды порядкового номера повторно записывается (подтверждается) порядковый номер слова.

Этот же сигнал на входе совпадения блока 17 синхронизации записи

разрешает формирование сигнала управ ления адресом, который увеличивает содержимое счетчика 2 адреса на единицу, а содержимое счетчика 3 уменьшает на единицу.

Если порядковый номер поступившег слова второй посылки и порядковый номер слова первой посылки, переписанный в регистр 8 из накопителя 1, не совпадают, то на выходе блока 20 сравнения остается нулевой сигнал, который, пбступая на вход совпадения блока 17 синхронизации записи, блокирует формирование сигналов синхронизации записи, выбора режима и управления адресом и записи полученной разности с выхода блока 18 обработки информации в накопитель 1 не происходит, а счетчик 2 адреса и счетчик 3 не изменяют своего содержимого и при поступлении второго информационного слова второй посыпки из накопителя 1 в регистры 7 и 8 вновь будет записан содержимое ячейки памяти накопителя с нулевым адресом. Если в текущем такте работы устройства в накопитель записывалась разность информационных слов (т.е. порядковые номера совпали) , то в следующем такте работы при поступлении очередного слова будет считано для сравнения порядковых номеров содержимое следующей в порядке возрастания адреса ячейки накопителя

Аналогичным образом устройство работает в последующих тактах поступления информации второй посылки до тех пор, пока содержимое счетчика 3 не станет равным нулю, а содержимое счетчика 2 адреса не примет значение последнего адреса ячейки памяти, в

которой была записана информация пер- 55 ства устанавливаются в исходное соевой посылки. В этом случае на выходе заема счетчика 3 появится сигнал, который, поступая на вход конца обработки блока 17 синхронизации записи,

тояние, за исключением счетчика 3, в котором сохраняется код адреса последней ячейки накопителя, в которую была занесена информация, и регистро

счетчике

блокирует его работу, и, как следствие, запись информации в накопитель 1 и перевод счетчика 2 адреса прекращаются, несмотря на поступление информации на вход 38 устройства.

Работа блока 16 контроля записи при приеме информации второй посыпки абсолютно аналогична его работе при приеме информации первой посыпки. После поступления на устройство последнего тактового импульса последней строки из блока 16 контроля записи он формирует на выходе установки конечного адреса сигнал, по которому в

5

0

счетчике

0

5

0

5

0

3 переписывается содержимое счетчика 2 адреса, а на выходе конца записи зтого же блока появляется единичный сигнал конца записи, который поступает на вход разряда первого канала мультиплексора 15. На этом запись второй посылки информации завершается .

Если в процессе приема информации второй посылки произошло нарушение количества либо последовательности поступления строчных или тактовых импульсов, то блок 16 контроля записи также, как и при приеме информации первой посылки, может формировать сигнал сбоя, по которому прекращается работа устройства, и в соответствующем разряде выходной информации на выходе 41 устройства формируется сигнал единицы. Контроль за работой устройства в этом режиме осуществляется так хе, как и при приеме информации первой посыпки, путем спроса информации на выходе 41 устройства по первому адресу выдачи информации, подачей соответствующих сигналов на входы синхронизации выдачи 39 информации и адреса выдачи 40 информации. В режиме приема информации второй посылки контролю подлежат только те разряды выходной информации, которые соответствуют сигналам сбоя и конца записи.

После появления сигнала конца записи на входы 37 шины управления поступает новое управляющее слово в сопровождении сигналов на входах адреса управления 36 и синхронизации управления 35, которое записывается в регистр 5 аналогично описанному. При этом все функциональные узлы устройства устанавливаются в исходное соетояние, за исключением счетчика 3, в котором сохраняется код адреса последней ячейки накопителя, в которую была занесена информация, и регистров

1316

6-8, состояние которых не влияет на работу устройства. Значение всех разрядов управляю1чего слова, записанного в регистр 5, безразлично, за исключением первого разряда, значение кото- рого равно нулю, и второго, определяющего перевод устройства в режим чтения (выдачи) из него информации, значение которого равно единице.

После записи управляющего слова устройство готово к выдаче информации. Наличие нулевого сигнала в первом разряде регистра 5 блокирует работу блока 16 контроля записи, устанавливает в исходное состояние триг- геры 9 и 10 и единичным сигналом с инверсного выхода триггера 10 блокирует работу блока 17 синхронизации записи, в результате чего на входе выбора режима накопителя 1 устанавли- вается нулевой сигнал, разрешающий выполнять только считывание из него информации.

Поступление единичного сигнала с выхода второго разряда регистра 5 на вход режима чтения блока 19 синхронизации чтения разрешает его работу и на его выходе синхронизации чтения появляется сигнал, по которому из накопителя 1 происходит считывание ин- формации из ячейки памяти с нулевым адресом, так как счетчик 2 адреса пока находится в исходном состоянии, и по сигналу на выходе синхронизации регистров этого же блока считанная из накопителя 1 информация записывается в регистры 7 и 8, после чего блок синхронизации чтения переходит в режим ожидания. Задним фронтом сигнала с выхода синхронизации чтения (после записи информации в регистры

7и 8) содержимое счетчика 2 адреса увеличивается, а счетчика 3 уменьшается на единицу, и H.I адресные входы накопителя 1 поступает адрес следую- щей ячейки памяти, подготавливая его

к следуютемv чтению информации с задержкой L. VUT относительно управляющего слова, выданного по шине управления на устройство. На вход 40 адреса выдачи информации поступает первая адресная комбинация, разрешающая прохождение сигнала с входа 39 синхронизации выдачи через элементы И 22 и ИЛИ 29 на вход разрешения мультиплексора 15, на адресном входе которого присутствует нулевой сигнал.

8результате этого открывается первый канал мультиплексора и на выход 41

0 5 0

5

,-

0

7514

устройства проходит информация ит рг- гистра 7, представляющая собой разность 1-х слов двух информационных посылок J J,,; - J2j .

Затем на вход 40 устройства поступает вторая адресная комбинация, которая вызывает появление единичного сигнала на втором выходе дешифратора 13, в результате чего на адресном входе мультиплексора 15 устанавливается единичный сигнал, а сигнал с входа 39 синхронизации выдачи информации через элемент И 23 поступает на вход управления чтением блока синхронизации чтения и через элемент ИЛИ 29 на вход разрешения мультиплексора 5. В результате этого открывается второй канал мультиплексора 15 и на выход 41 устройства проходит информация из регистра 8, представляющая собой порядковый номер информационных слов первой и второй посыпок, результат обработки которых был выдан ранее.

Сигнал на вход е управления чтением блока 19 синхронизации чтения устанавливает его в исходное состояние и после снятия этого сигнала блок синхронизации чтения повторяет цикл формирования на своих выходах синхронизации чтения и синхронизации регистров сигналов, по которым информация из следующей ячейки памяти накопителя 1 переписывается в регистры 7 и 8.

Аналогичным образом продолжается работа устройства при выдаче информации до тех пор, пока содержимое счетчика 2 адреса не станет равным значению кода адреса последней ячейки накопителя 1, в которую была занесена информация при записи, а содержимое счетчика 3 равным нулю.

Сигнал с выхода заема счетчика 3 через элемент И 25, открытый сигналом с выхода второго разряда регистра 5, поступит на вход соответствующего разряда первого канала мультиплексора 1 5 и будет выдан на выход 41 устройства при выдаче результата обработки информации, находящейся в последней занятой ячейке памяти накопителя 1. Появление указанного сигнала свидетельствует об окончании выдачи информации из устройства. После появления сигнала об окончании выдачи информации из устройства считывается порядковьй номер последнего результата обработки информации, на этом работа устройства по приему, обработке и выдаче информации завершается.

ормула изобретения

Буферное запоминающее устройство, одержащее дешифратор адреса управления , входы которого являются входами адреса управления устройства, а выод подключен к первому входу первого элемента И, второй вход которого явяется входом синхронизации управления устройства, а выход соединен с входом сброса первого счетчика, входами установки в исходное состояние блока контроля записи, блока синхронизации записи и блока синхронизации тения и с синхровходом первого регистра, информационные входы которого являются входами управления устройства, а первый выход подключен к информационному входу первого триггера и к входу режима записи блока контроля записи, второй выход первого регистра соединен с входом режима чтения блока синхронизации чтения, синхровход первого триггера является входом начала кадра устройства и подключен к одноименному входу блока контроля записи, выход первого триггера соединен с информационным входом второго триггера, синхровход которого подключен к входу строчных импульсов блока контроля записи и является одноименным входом устройства, выходы сигналов сбоя и конца записи блока контроля записи соединены с одноименными входами блока синхронизации записи и с информационными входами соответствующих разрядов первой группы мультиплексора, входы синхронизации блока синхронизации записи и блока инхронизации чтения подключены к выходу генератора тактовых импульсов, дешифратор адреса выдачи информации, входы которого являются входами адреса выдачи информации устройства, а первый и второй выходы соединены соответственно с первыми входами второго и третьего элементов Hs вторые , входы которых являются входом синхронизации выдачи информации устройства, второй регистр, информационные входы которого являются входами информации устройства, накопитель, выходы первой группы которого .соединены с информационными входами третьего регистра, синхровход которого соединен с синх- овходом четвертого регистра, выходы оторого подключены к информационным входам второй группы мультиплексора, выходы которого являются информацион

0

5

0

5

0

5

0

5

ными выходами устройства, выходы третьего регистра соединены с информационными входами соответствующих разрядов первой группы мультиплексора, инверсный выход второго триггера подключен к входу включения блока записи, выход синхронизации записи которого соединен с первым входом первого элемента ИЛИ, второй вход которого подключен к выходу синхронизации чтения блока синхронизации чтения, выход управления адресом блока синхронизации записи подключен к первому входу второго элемента ИЛИ, выходы первого счетчика соединены с адресными входами накопителя, один из информационных входов первой группы мультиплексора подключен к выходу третьего триггера, четвертый и пятый элементы И, третий, четвертый и пятый элементы ИЛИ и элемент НЕ, отличающееся тем, что, с целью упрощения устройства за счет уменьшения объема хранимой информации j в устройство введены второй и третий счетчики, блок обработки информации и блок сравнения, причем третий выход первого регистра подключен к входам режима блока синхронизации записи и блока обработки информации, выходы группы первого регистра соединены с входами кода порога селекции блока обработки информации, информационные входы первой и второй групп которого подключены к выходам соответственно второго и третьего регистров, а информационные выходы и выход разрешения записи соединены соответственно с информационными входами первой группы накопителя и входом разрешения блока синхронизации записи, выход установки конечного адреса блока контроля записи подключен к управляющему входу второго счетчика, информационные входы которого соединены с адресными входами накопителя, а выход заема подключен к входу конца обработки блока синхронизации, выход синхронизации регистров которого соединен с синхровходами второго регистра и третьего счетчика, с входом установки блока контроля записи и с первым входом третьего элемента ИЛИ, выход которого соединен с синхровхо- дом четвертого регистра, информационные входы которого подключены к выходам второй группы накопителя, информационные входы второй группы которого соединены с выходами третьего

счетчика и с входами перпой группы блока сравнения, входы второй группы которого подключены к выходам четвертого регистра, а выход соединен с входом совпадения блока синхронизации записи, выход выбора режима которого подключен к одноименному входу накопителя, синхровход которого соединен с выходом первого элемента ИЛИ, второй вход третьего элемента ИЛИ подключен к выходу синхронизации регистров, вход управления которого соединен с выходом третьего элемента И и с первым входом четвертого элемента ИЛИ, второй вход которого подключен к выходу второго элемента И, а выход соединен с входом выборки мультиплексора, адресный вход которого подключен к первому входу третьего элемента И, второй вход первого элемента ИЛИ соединен с вторым входом второго элемента ИЛИ, выход которого соединен с синхровходами третьего триггера, первого и второго счетчиков, выход переноса первого счетчика подключен

зг

5

0

5

к информационному входу третьего триггера, вход сброса которого соединен с выходом первого элемента И, с входом сброса третьего счетчика и с первым входом пятого элемента ИЛИ, выход которого подключен к входам сброса первого и второго триггеров, а второй вход соединен с выходом элемента НЕ, вход которого подключен к первому выходу первого регистра, прямой выход второго триггера соединен с первым входом четвертого элемента И, второй вход которого является входом тактовых импульсов устройства, а выход подключен к входам тактовых импульсов блока контроля записи и блока синхронизации записи, второй выход первого регистра соединен с первым входом пятого элемента И, второй вход которого подключен к выходу заема второго счетчика, а выход соединен с. соответствующим информационным входом первой группы мультиплексора.

Фиг. 5

| Буферное запоминающее устройство | 1983 |

|

SU1119077A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Буферное оперативное запоминающее устройство | 1988 |

|

SU1559379A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1991-06-07—Публикация

1989-06-14—Подача