геров и с вторым входом четвертого элемента И, третий вход которого соединен с вторым выходом управляемого генератора тактов, выход четвертого элемента И является выходом Общая норма устройства.

2. Устройство по пЛ, отличаю щ ее с я тем, что хправляе мый генератор тактов содержит RS-триггер, генератор импульсов,два элемента И, делитель частоты, два элемента ИЛИ, счетчик, дешифратор, группу элементов И, причем вход пуска управляемого генератора тактов соединен с s-входом RS-триггера и первым входом первого элемента ИШ, второй вход которого соединен с управляющим входом генератора, RS-триггера соединен с шиной начальной установки устройства, выход RS-триггера соединен с первым

входом первого элемента И, второй вход которого соединен с выходом генератора импульсов, выход первого элемента И соединен с вхадом делителя частоты, выходы которого соединены поразрядно с первыми входами соответствующих элементов И группы, вторые входы которых поразрядно соединены с выходами дешифратора, выход первого элемента ИЛИ соединен с первым входом второго элемента И и счетным входом счетчика, выходы которого поразрядно соединены с входами дешифратора, выходы элементов И группы соединены с входами второго элемента ИЛИ, выход которого соединен с первым выходом управляемого генератора тактов, последний выход дешифратора соединен с вторым входом второго элемента И, выход которого соединен с вторым выходом управляемого генератора тактов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых блоков | 1980 |

|

SU960826A1 |

| Устройство для контроля логических узлов | 1981 |

|

SU968816A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для контроля мажоритарных схем | 1983 |

|

SU1117643A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА КОМАНД ТЕЛЕУПРАВЛЕНИЯ | 1991 |

|

RU2023309C1 |

| Многоканальное устройство для измерения температуры | 1984 |

|

SU1229599A1 |

| Устройство для контроля микропроцессорных программных блоков | 1983 |

|

SU1267424A1 |

| Устройство для контроля логических блоков | 1988 |

|

SU1608672A1 |

| Устройство для контроля цифровых объектов | 1988 |

|

SU1691841A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

1; УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОШЛХ ОБЪЕКТОВ, содержащее генератор тактов, первый элемент И, первый счетчик, первый дешифратор, первый НЗ-трйггер, блоки памяти эталонной и контрольной информации, трехвxoдoвыecxe вi сравнения, регистр и элемент ИЛИ, причем вход генератора тактов является входом устройства, выход генератора тактов соединен с первым входом первого элемента И, выход которого соединен со счетным входом первого счетчика, вход сброса которого соединен с выходом первого дешифратора и S-входом первого RS-триггера, инверсный .выход которого соединён с вторьм входом пер-вого элемента И, группа выходов первого счетчика поразрядно соединена с соответствукмдими входами первого дешифратора и входами- эталонного объекта, группа выходов которого по-раэрядно соединена с соответствующими информационными входами блока памяти эталонной информации, группа выходов контролируемого объекта поразрядно соединена с информационными входами блока памяти контрольной информации, одноюяенные разряды выходов блока памяти эталонной информации и блока памяти контрольной информации соединены соответственно с первыми и вторыми входакш соответствующих схем сравнения, выходы , которых поразрядно соединены с входами регистра, выходы которого соединены с соотвётствьтощими входами элемента или, выход которого является выходом Сбой устройства, о т л и чающееся тем, что, с целью расширения функциональных возможностей за счет обеспечения прогнозирования постепенных отказов цифровых объектов, в устройство введены управлякядий генератор тактор, второй элемент И, второй счетчик, второй дешифратор, второй RS-триггер, узел выделения первого импульса, первый и второй элементы задержки и третий и четвертый элементы И, причем вход пуска управляемого генератора тактов соединен с входом устройства, первый выход управляемого генератора тактов соединен с первым входом уе второго элемента И, выход которого соединен с управляющим входом блокапамяти контрольной информации и счетным входом второго счетчика, вход сброса которого соединен с выходоу второго дешифратора и S-входом ВТОРОГО RS-триггера инверсный выход которого соединен с вторым входом второго элемента И,группа, выходов второго счетчика поразрядно соединена с соответствующими входами второго дешифратора и входами контролируемого объекта, выход первого элемента И соединен с управляющим входом блока памяти эталонной информации и входом узла выделения первого импульса1, выход которого соединен с входом первого эли«1ента задержки выход которого соединен с управляющим входом управляемого I генератора тактов, с третьими входа ми схем сравнения и с входом второго элемента задержки, выход которого сое. динен с первым входом третьего элемента И, второй вход которого соединен с первым входом четвертого элемента И и выходом элемента ИЛИ, BL.ход третьего элементу И соеди-нен с R-входами первого и второго RS-триг

Изобретение относится к вычислительной технике и может быть использовано при контроле цифровых объектов .

Известно устройство для контр1апя комбинационных схем, содержавшее генератор импульсов, счетчик, дешифратор, блок элементов совпадения и табло индикации l} .

Недостаток этого устрсй1с вй от сутствие возможности прогнозировать отказы контролируемых схем.

Наиболее близким по технической сущности к предлагаемому является устройство для испытания логических блоков, содержащее генератор тактов элемент И, счетчик, дешй аторг RS-триггер, блок памяти эталойной и контрольной информации, трехвходовые схемы сравнения, регистр нэдшмент ИЛИ, причем вход генератора тактов является входом устройства, выход генератора тактов соединен с первым входом элемента И, выход которого соединен со счетным ВХОДОМ счетчика, вход сброса которого соединен с выходам дешифратора и S-входом RS-триггера инверсный выход которого соединен с вторым входом элемента И, пруппа выходов счетчика поразрядно соединена с соответствую щими входами дешифратора и входами эталонного объекта, группа выходов которого поразрядно соединена с соответствуюйдами информационными входами блока памяти эталонной информации,, группа выходов проверяем

мого объекта поразрядно соединена с информационными входами блока памяти, контроль ной информации, одноименные разряды выходов блока памяти эталонной информации и блока памяти контрольной информации соединены соответственно с первым и вторым входом соответствующих схем сравнения, выходр которых поразрядно соединены с входами регистра, выходы которого соединены с соответствующими входами элемента ИЛИ, Выход которого является выходом Сбой устройства i. 2j.

Недостаток известного устройства состоит в том, что оно не позволяет прогнозировать 1 остепенные отказы, развивающиеся в цифровых Объектах от старения или из-за технологических дефектов.

Цель изобретения - расширение 4 нкциональных возможностей устройства за счет обеспечения прогнозирования постепенных отказов цифровых объектов.

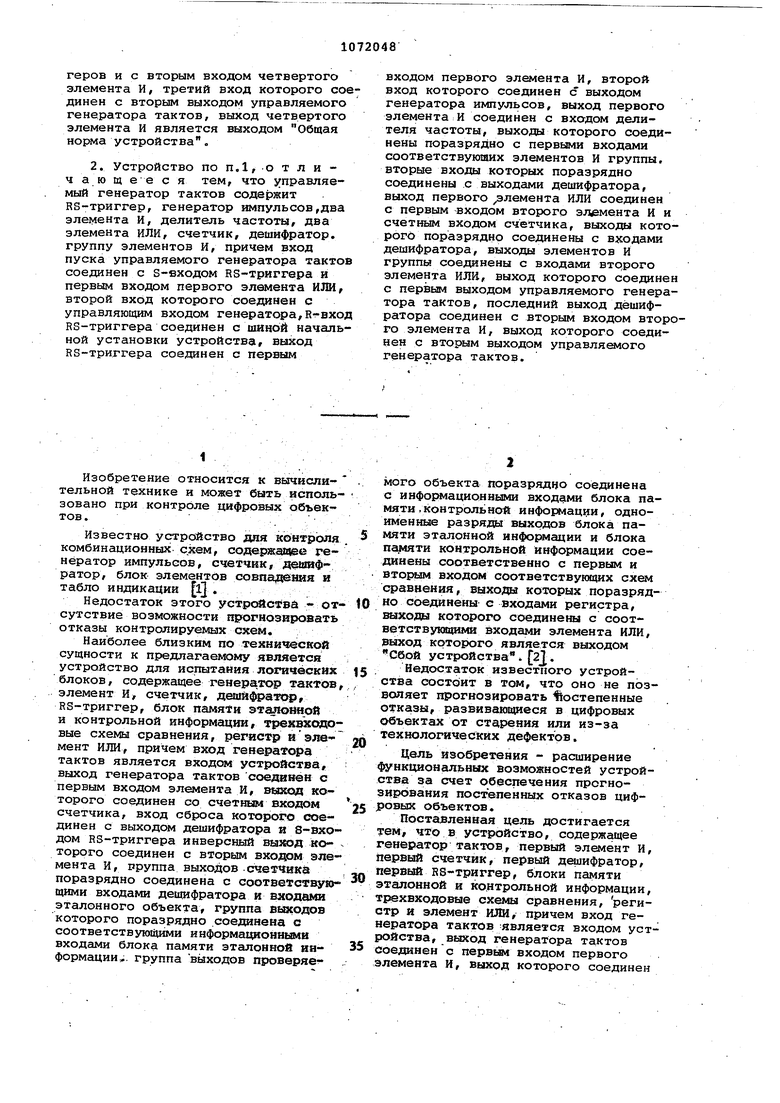

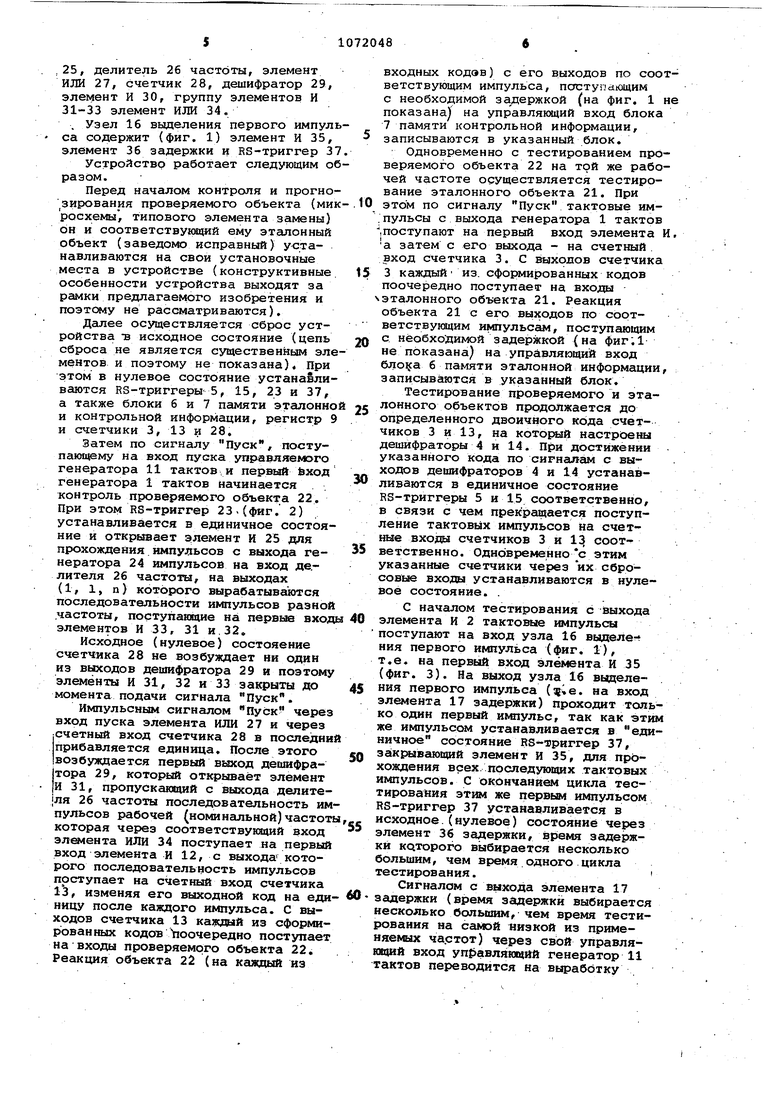

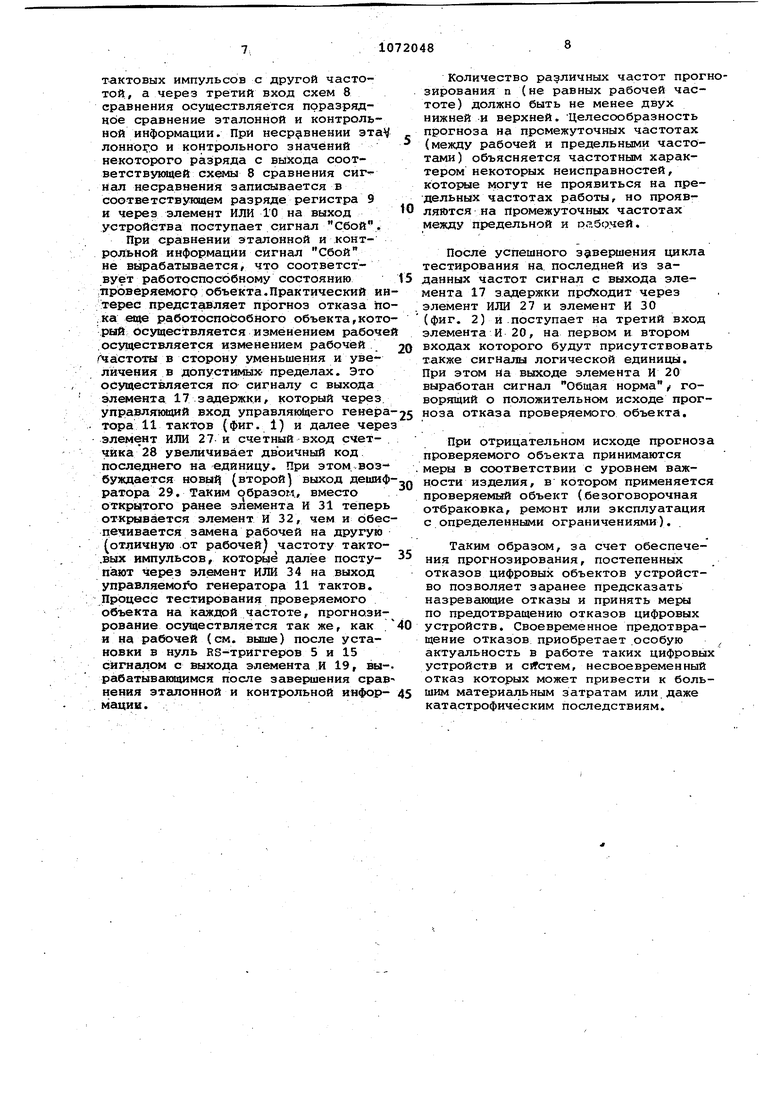

Поставленная цель достигается тем, что в устройство, содержащее генератор тактов, первый элемент и, первый счетчик, первый даиифратор, перВЕ RS-триггер, блоки памяти эталонной и контрольной информации, трехвходовые схемы сравнения, регистр и элемент ИЛИ, причем вход генератора тактов -является входом устройства, выход генератора тактов соединен с первьвч входом первого элемента И, выход которого соединен счетным входом первого счетчика, вход сброса которого соединен с выходом первого дешифратора и-З-входом первого RS-триггера, инверсный выход которого соединен с вторым входом первого элемента И, группа выходов первйго счетчика поразрядно соединена с соответстйующими входам первого дешифратора и входами эталонного объекта, группа выходов которого поразрядно соединена с соот ветствующими информационными входами бло|са памяти талонной информации, группа выходов проверяемого объекта поразрядно соединена с информационными входами блока памяти контрольной информации, одноименные разряды выходов блока:, памяти эталонной информации и блока памяти контрольной информации соединены соответственно с первым и вторым входом соответствующих схем сравнения,выходы которых поразрядно соединены с входами регистра, выходы которого соединены с „соответствующими входами элемента КПК, выход которого является выхо.дом Сбой устройства, введены управ лйемый генератор тактов., второй элемент И, второй счетчик, второй дешифратор, второй RS-триггер, узел выделения первого импульса, первый и второй элементы задержки и третий и четвертый элементы И, вход пуска управляемого генератора тактов соединен с входом устройства первый выход управляемого генёратора тактов соединен с первым входом второго элемента И, выход которого соединен с управляющим входом блока памяти контрольной информации и счет ным входом второго счетчика, вход сброса которого соединен с выходом второго дешифратора и S-входом второ го RS-триггёра, инверсный выход которого соединен с вторым входом второго элемента И, группа выходов в-торого счетчика поразрядно соединена с соответствукяцими входами второг дешифратора и входами проверяемого объекта, выход первого элемента И соединен с управляницим входом блока (Памяти эталонной информации и входом узла выделения первого импульса, выход которого соединен с входом первого элемента задержки, выход которо го соединен с управляющим входом управляемого генератора тактов, с третьими входами схем сравнения и с входом второго элемента задержки, выход которого соединен с первым входом третьего элемента И, второй вход которого соединен с первьш входом четвертого элемента И и выходом элемента ИЛИ, выход третьего элемента И соединен с R-входами первого и второго RS-триггеров и с вторым входом четвертого элемента И, третий вход которого соединен с вторым выхрдом управляемого генератора тактов,выход четвертого элемента И является выходом Общая норма устройства. Кроме того, управляемый генератор тактов - содержит RS-триггер, генератор импульсов, два элемента.И, делитель частоты, два элемента ИЛИ, счетчик, дешифратор, группу элементов И, причем вход пуска управляемого генератора тактов соединен с S-входом RS-триггера и первьш входом первого элемента ИЛИ, второй вход которого соединён с управляющим входом генератора, R-вход RS-триггера соединен с шиной начальной установки устройства, выход RSrтpиггepa соединен с первым входом первого элемента И, второй вход которого соединен с выходом генератора импульсов, выход первого элементу И соединен с входом делителя частоты, выходы которого соединены поразрядно с первыми входами соответствующих элементов И группы, вторые входы которых поразрядно соединены с выходами дешифратора, выход первого элемента ИЛИ соединен с первым входом второго элемента И и счетным входом счетчика, выходы которого поразрядно соединены с входами дешифратора, вых9Ды элементов И группы соединены с входами второго элемента ИЛИ, выход которого соединен с первым выходом управляемого генератора тактов, последний выход Дешифратора соединен с вторым входом второго элемента И, выход которого соединен с вторым выходом управляемого генератора тактов. На фиг. 1 представлена блок-схема устройства контроля и цифровых объектов; на фиг. 2 - блок-схема управляемого генератора тактовj на фиг.З блок-схема выделения первого импульса. Устройство содержит (фиг. 1) генератор 1 тактов, первый элемент И 2,, первый счетчик 3, первый дешифратор 4, первый RS-триггер 5, блоки 6 и 7 эталонной и контрольной информации, трехвходовые схемы 8 сравнения, регистр 9, элемент ИЛИ 10, управляеглый генератор 11 тактов, второй элемент И 12, второй счетчик 13, второй дешифратор 14, второй RB-триггер 15, узел 16 выделений первого импульса, первый 17 и второй 18 элементы задержки, третий 19 и четвертый 20 элементы И. Эталонный объект 21 и проверяемый объект 22 не входит в состав устройства, на фиг. 1 они приведены для пояснения. Управляемый генератор 11 тактор (фиг. 2) содержит RS-триггер. 23, генератор 24 импульсов, элемент и

25, делитель 26 частоты, элемент ИЛИ 27, счетчик 28, дешифратор 29, элемент И 30, группу элементов И 31-33 элемент ИЛИ 34.

Узел 16 вьаделения первого импульса содержит (фиг. 1) элемент И 35, элемент 36 задержки и RS-триггер 37

Устройство работает следующим образом.

Перед началом контроля и прогно зирования проверяемого объекта (микросхемы, типового элемента замены) он и соответствукнций ему эталонный объект (заведокю исправный) устанавливаются на свои установочные места в устройстве (конструктивные. особенности устройства выходят за рамки предлагаемого изобретения и поэтому не рассматриваются).

Далее осуществляется сброс устройства -в исходное состояние (цепь сброса не является существенным элементов и поэтому не показана). При этом в нулевое состояние устанаёливаются RS-триггеры 5, 15, 23 и 37, а также блоки 6 и 7 памяти эталонно и контрольной информации, регистр 9 и счетчики 3, 13 и 28.

Затем по сигналу Пуск, поступающему на вход пуска управляемого генератора 11 тактов,и первый Ьход генератора 1 тактов начинается контроль проверяемого объекта 22. При этом RS-триггер 23 -(фиг. 2) устанавливается в единичное состояние и открывает элемент И 25 для прохождения импульсов с выхода генератора 24 импульсой на вход делителя 26 частоты, на выходах (1, 1, п) которого вырабатываются последовательности импульсов разной частоты, поступающие на первые вход элементов И 33, 31 и,32.

Исходное (нулевое) состояение счетчика 28 не возбуждает ни один из выходов дешифратора 29 и поэтому элемёнш И 31, 32 и 33 закрыты до момента подачи сигнала Пуск.

Импульсным сигналом Пуск через вход пуска элемента ИЛИ 27 и через счетный вход счетчика 28 в последни прибавляется единица. После этого возбуждается первый выход дешифратора 29, который открывает элемент И 31, пропускающий с выхода депите|ля 26 частоты последовательность импульсов рабочей (номинальной)частот которая через соответствуняций вход элемента ИЛИ 34 поступает на первый вход элемента И 12, с выхода которого последовательность импульсов поступает на счетный вход счетчика 13, изменяя его выходной код на единицу после каждого импульса. С выходов счетчика 13 каждый из сформированных кодов поочередно поступает на входы проверяемого объекта 22. Реакция объекта 22 (на каждый из

входных кодэв) с его выходов по соответствующим импульса, поступакддим с необходимой за держкой (на фиг. 1 не показана) на управлякадий вход блока 7 памяти контрольной информации, записываются в указанный блок.

Одновременно с тестированием проверяемого объекта 22 на той же рабочей частоте осуществляется тестирование эталонного объекта 21. При этом по сигналу Пуск тактовые импульсы с выхода генератора 1 тактов .поступают на первый вход элемента И. а затем с его выхода - на счетный вход счетчика 3. С выходов счетчика 3 каждый из. сформированных кодов поочередно поступает на входы эталонного объекта 21. Реакция объекта 21 с его выходов по сортветствукяцим и ульсам, поступающим с необходимой задержкой (на фиг;1 не показана) на управляющий вход б памяти эталонной информации, записываются в указанный блок.

Тестирование проверяемого и эталонного объектов продолжается до определенного двоичного кода счетчиков 3 и 13, на который настроены дешифраторы 4 и 14. При достижении указанного кода по сигналшл с выходов дешифраторов 4 и 14 устанавливаются в единичное состояние RS-триггеры 5 и 15 соответственно, в связи с чем прекраи{ается поступление тактовых импульсов на счетные входы счетчиков 3 и 1: соответственно. Одновременно с этим указанные счетчики через их сбросовые входы устанавливаются в нулевое состояние. .

С началом тестирования с выхода элемента И 2 тактовые импульсы

поступают на вход узла 16 вьщелег ния первого импульса (фиг. 1), т.е. на первый вход элемента И 35 (фиг. 3). На выход узла 16 выделения первого импульса (i4e. на вход элемента 17 задержки) проходит только один первый импульс, так как этим же импульссш устанавливается в единичное состояние RS-spHrrep 37, закрывающий элемент И 35, для прохождения всех, последуюаих тактовых импульсов. С окончанием цикла тестирования эт1т же первым импульсом RS-триггер 37 устанааливается в исходное.(нулевое) состояние через элемент 36 задержки, время задержки которого выбирается несколько большим, чем время одного цикла тестирования.

Сигналом с выхода элемента 17

задержки (время задержки выбирается несколько большим, чем время тестирования на самой низкой из применяемых ча.стот) через свой управляккций вход уп| авляк 1чйй генератор 11 тактов переводится на выработку тактовых импульсов с другой частотой, а через третий вход схем 8 сравнения осуществляется поразрядное сравнение эталонной и контрольной информации. При неср внении эта лонно о и контрольного значений некоторого разряда с выхода соответствующей схемы 8 сравнения сигНал несравнения записывается в соответствующем разряде регистра 9 и через элемент ИЛИ ID на выход устройства поступает сигнал Сбой, При сравнении эталонной и контрольной информации сигнал Сбой не вырабатывается, что соответствует работоспособному состоянию .проверяемого объекта .Практический и терес представляет прогноз отказа по ка еще работоспособного объекта,кото рый; Осуществляется изменением рабоче .осуществляется изменением рабочей гчастоты в сторону уменьшения и увеличения в допустимых- пределах. Это осуществляется по сигналу с выхода эл&лен1а 17 задержки, который через управляниций вход управляю1цего генера тора 11 тактов (фиг. 1) и далее чере элемент ИЛИ 27 и счетный вход счетчика 28 увеличивает двоичный код последнего на единицу. При этом,,возбуждается новы{| (второй) выход дешиф ратора 29, Таким образом., вместо открытого ранее элемента И 31 теперь открывается элемент и 32, чем и Обес печивается замена рабочей на другую (отличную от рабочей) частоту такто.вых импульсов, которые далее поступают через элемент ИЛИ 34 на выход управляемоiro генератора 11 тактов. Процесс тестирования проверяемого объекта на каждой частоте, прогнозирование осуществляется так же, как и на рабочей (см. выше) после установки в нуль RS-триггеров 5 и 15 сигналом с выхода элемента И 19, вырабатывающимся после завершения срав нения эталонной и контрольной информации. Количество различных частот прогнозирования п (не равных рабочей частоте) должно быть не менее двух нижней и верхней. Целесообразность прогноза на промежуточных частотах (между рабочей и предельными частотами) объясняется частотным характером некоторых неисправностей, которые могут не проявиться на предельных частотах работы, но прояви ляются на Промежуточных частотах между предельной и р..5(чей. После успешного завершения цикла тестирования на последней из заданных частот сигнал с выхода элемента 17 задержки прсЛсодит через элемент ИЛИ 27 и элемент И 30 (фиг. 2) и .поступает на третий вход элемента И 20, на первом и втором входах которого будут присутствовать также сигналы логической единицы. При этом на выходе элемента И 20 выработан сигнал Общая норма f говорящий о положительнс 1 исходе прогноза отказа проверяемого объекта. При отрицательном исходе прогноза проверяемого объекта принимаются меры в соответствии с уровнем важности изделия. В котором применяется проверяемый объект (безоговорочная отбраковка, ремонт или эксплуатация с определенными ограничениями). Таким образом, за счет обеспечения прогнозирования, постепенных отказов цифровых объектов устройство позволяет заранее предсказать назревающие отказы и принять меры по предотвращению отказов цифровых устройств. Своевременное предотвращение отказов приобретает .особую , актуальность в работе таких цифровых устройств и сЛстем, несвоевременный отказ которых может привести к большим материальным затратам или даже катастрофическим последствиям.

4

f7T

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для испытания логических блоков | 1975 |

|

SU551573A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1984-02-07—Публикация

1982-01-28—Подача