Изоб)етение относится к вычислительной технике и предназначено для использования в аналоговых и аналого-цифровых вычислительных устройствах.

Известно множительное устройство, в котором требуемое значение дробнорациональной функции формируется в сумматоре с помощью интегрирующего преобразователя напряжения в длительность импульса как алгебраическая сумма приближенного результата первого такта и поправки, формируемой в двух последующих тактах 1). Недостатком данного устройства является необходимость выполнения условия / Е К / 2 , где Е - третья переменная;

К - коэффициент преобразования интегрирующего преобразователя напряжения в длительность импульса, налагающий ограничение на рабочий диапазон устройства относительно третьей переменной.

Наиболее близким к предлагаемому является множительно-делительное уст; ройство, содержащее распределитель

тактовых импульсов,преобразователь первой переменной во временной ин- тервал, вход которого является первым входе устройства, последовательно соединенные первый ключ, интегратор, блок запоминания, второй ключ, преобразователь напряжения в длительность импульса, первый выход которого подключен к управляюще10му входу третьего ключа, информационный вход которого является вторым входом устройства и через последовательно соединенные четвертый ключ и дополнительный, масштабный преоб15разователь подключен к второму информационному входу преобразователя напряжения в длительность импульса, а выход третьего ключа подключен ко входу интегратора, последовательно

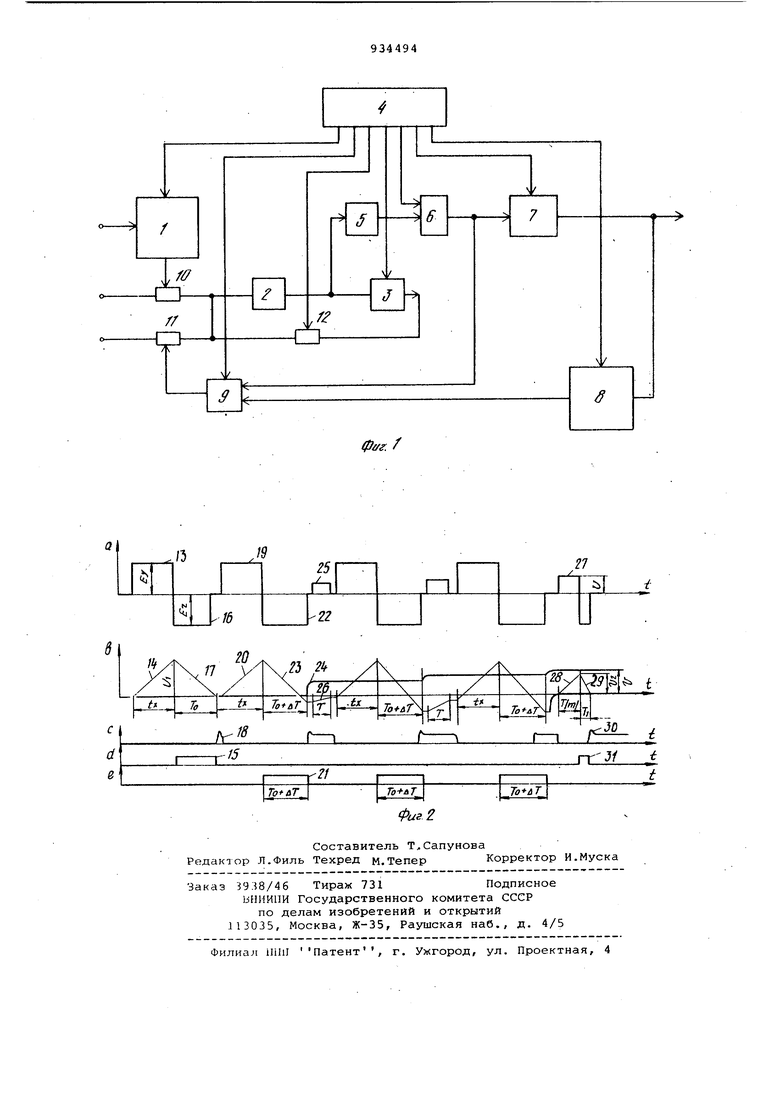

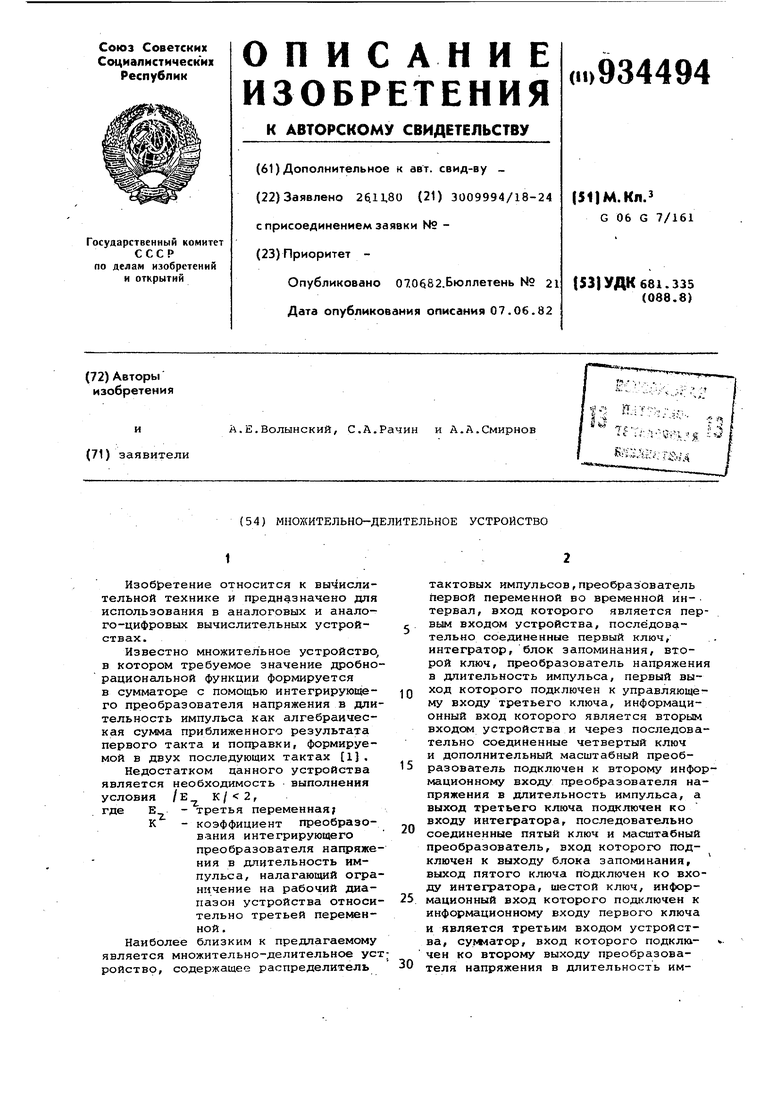

20 соединенные пятый ключ и масштабный преобразователь, вход которого подключен к выходу блока запоминания, выход пятого ключа подключен ко входу интегратора, шестой ключ, инфор25мационный вход которого подключен к информационному входу первого ключа и является третьим входом устройства, суг-матор, вход которого подключен ко второму выходу преобразова30теля напряжения в длительность импульса, а выход является выходом устройства, управляющие ВХОДЕЛ первого U шестого ключа подключены к соответстнующим выходам преобразователя первой переменной во временной интервал, выходы распределителя тактовых импульсов подключены соответственно к управляющим входам преобразователя первой переменной во временной интервал, пятого ключа, второго ключа, преобразователя напряжения в длительность импульса, сумматора и четвертого ключа J. В этом устройстве расширение диа пазона возможных изменений третьей переменной обеспечивается за счет такта автоподстройки коэффициента преобразования интегрирующего пре образователя напряжения в длительность импульса; однако введение дополнительного такта приводит к увел чению длительности рабочего цикла устройства, т.е. к уменьшению его быстродействия, а также связано с затратами на оборудование-, множител но-делительного устройства дополнительным каналом автоподстройки. Цель изобретения - увеличение бы тродействия устройства. Поставленная цель достигается тем, что в множительно-делительное устройство, содержащее преобразователь первой переменной во временно интервал, последовательно соединенн первый ключ, интегратор и блок запо минания, второй и третий ключи, сум матер и распределитель тактовых импульсов, вход преобразователя перво переменной во временной интервал яв ляется первым входом устройства, ин формационный вход первого ключа я-вляется вторым входом устройства, а управляющий вход подключен к выходу преобразователя первой переменной во временной интервал, информационный вход второго ключа является третьим входом устройства, а выход второго ключа подключен к входу интегратора и к выходу третьего ключа, выход бло ка запоминания подключен к информационному входу третьего ключа, выход сумматора является выходом устройства,первый, второй, третий и чет вертый выходы распределителя тактовых импульсов людключены соответст:венно к управляющим входам преобразователя первой переменной во време ной интервал, третьего ключа, блока запоминания и сумматора, введены пос ледовательно включенные нуль-орган и формирователь -временных интервалов, преобразователь выходной переменной во временной интервал и мультиплексо вход нуль-органа подключен к выходу интегратора, а выход подключен к информационному входу формирователя временных интервалов, выход ко торого подключен к информационному входу сумматора и к первому информационному входу мультиплексора, информационный вход преобразователя выходной переменной во временной интервал подключен к выходу сумматора, а выход - ко второму информационному входу мультиплексора, выход которого подключен к управляющему входу второго ключа, управляющие входы муль типлексора, формирователя временных интервалов и преобразователя выходной переменной во временной интервал подключены соответственно к пятому, шестому и седьмому выходам распределителя тактовых импульсов. На фиг. Д представлена функциональная схема множительно-делительного устройства; на фиг. 2 - временные диаграммы, поясняющие работу устройства. Множительно-делительное устройство содержит преобразователь 1 первой переменной во временной интервал, интегратор 2, блок 3 запоминания, распределитель 4 тактовых импульсов, нуль-орган 5, формирователь 6 временных интервалов, сумматор 7, преобразователь 8 выходной переменной во временной интервал, мультиплексор 9, первый, второй и третий ключи 10, 11 и 12 соответственно. На,фиг. 2 обозначено q - изменение выходного сигнала интегратора 2; Ъ выходных напряжений интегратора 2 и блока 3 запоминания; С.- выходные сигналы формирователя .6 временных интервалов и преобразователя .8 выходной переменной во временной интервал соответственно. Устройство работает следующим образом. В начале вычислительного цикла, состоящего из трех тактов, распределитель 4 выдает команду преобразователю 1 первой переменной во временной интервал на считывание, запоминание и преобразование во временной интервал t текущего значения первой переменной, представленной, например, параметром частотновременной группы или кодом. Далее преобразователь 1 замыкает ключ 10 на время t, в течение которого вторая переменная Еу подается на вход интегратора, 2 (на диаграмме поз. 13),, а на выходе интегратора 2 формируется линейно-и-зменяюшееся напряжение (на диаграмме поз. 14); к концу указанного интервала напряжение на выходе интегратора 2 достигает уровня и - -bLSr. - тг где Ъ- постоянная времени интегри-рования. По окончании данной части такта распределитель 4 с помощью мультиплексора 9, роль которого заключается в подключениях входа управления ключа 12 к выходу блока 6 или 8, подключает выход формирователя 6 к входу управления ключа 11 и далее выдает импульс запуска данному формирователю б. При поступлении данного сигнала формирователь б (в простейшем случае - триггерная ячейка) начинает вырабатывать интервал зalvIЫкaния ключа 11 (на диаграмме поз. 15), в течение которого третья переменная чья полярность противоположна полярности второй перёменной, подается на вход интегратора 2 (на диаграмме поз. 16 Выходное напряжение интегратора начинает убывать по линейному закон Up (t) и.+-5: (на диаграмме поз, 17), а в момент достиже ния им нулевого уровня срабатывает компаратор 5 и своим выходным сигналом, условно показанным на эпюре. импульсов поз, 18, возвращает фор мирователь б в исходное состояние, В результате последней операции завершается формирование интервала за мыкания ключа 11, длительность кото рого заносится также в сумматор 7 в качестве приближенного результата вычисления дробно-рациональной функ ции If в первом такте. Второй такт работы устройства со держит несколько итерационных цикло (на эпюрах три цикла). В начале каж дого из. указанных циклов преобразо ватель 1 замыкает ключ 10 на время, на вход интегратора поступает вт рая переменная (изменения входного и выходного сигналов интегратора в этой части цикла показано на диагра ме поз. 19 и 20 соответственно). П окончании данной части цикла распределитель 4 подключает с Помощью мультиплексора 9 выход преЬбразоваля 8 выходной переменной во временной интервал ко входу управления ключа 11 и далее выдает импульс за пуска указанному преобразователю. По данному сигналу преобразователь вырабатывает временной интервал, длительность которохо где ЛТ - ошибка дискретности формирования результата пер вого TciKTa (ДТ 70), соответственно записанному в сумматор 7 первому приближенному результ ту вычисления (процесс формирования интервала показан на диаграмме поз, 21). При зтом третья переменная пос тупает на вход интегратора (на диаграмме поз, 22), выдавая соответствующий отклик на выходе данного (поз. 23) . В последующей части итерационного цикла распределитель 4 выдает импульс записи блоку 3, по которому данный блок запоминает выходное напряжение интегратора2 (изменение выходного напряжения блока 3 показано поз, 24, где для наглядности принято, что коэффициент передачи блока Зга -1, фактически же/m/77l. В оставшейся части каждого цикла второго такта распределителем 4 выдается на вход управления ключа 12 импульс, длительность которого Т равна частному от деления номинальной постоянной времени интегратора 2 на величину/ж/ ; в течение данного интервала ключ 11 замкнут, и выходное напряжение блока 3 интегрируется интегратором 2 (изменения входного и выходного сигналов интегратора условно показаны на эпюрах поз. 25 и 26), Аналогично прототипу можно показать, что к концу второго такта на выходе блока 3 формируется напряжение поправки - hxS +(То+йТ) Ej.. В начале третьего такта распрет делитель 4 замыкает на время Т/и)/ ключ 12, и выходное напряжение блока 3 подается на вход интегратора 2 (поз. .27), вызывая соответствующий отклик на его выходе (поз. 28). По окончании данного интервала выход-ное напряжение интегратора 2 достигает уровня 2 4 Далее аналогично первому такту распределитель 4 подключает выход формирователя б через мультиплексор 9 ко входу управления ключа 11 и выдает импульс запуска формирователю 6. Подобно первому такту на выходе формирователя б вырабатывается интегратор управления, в течение которого замы- кается ключ 11 и третья переменная, чья полярность должна быть противоположна полярности величины поправки, подается на вход интегратора 2 и интегрируется в данном блоке, вызывая убывание его выходного напря, жения по линейному закону Upi(t)(на диаграмме поз. 29). Нулевое значение величины Up в момент регистрируется, как и в первом такте, компаратором 5, выходным сигнсшом которого (на диаграмме поз. 30) формирователь б возвращается в исходное состояние; этим обеспечивается окончание выработанного им интервала замыкания ключа 11 (на диаграмме поз. 31), значение длительности которого с ошибкой дискретиости йТ /т/ дТ заносятся в сумматор 7 с. весом Р О в качестве поправки к полученному ранее приближенному ре зультату вычисления. К концу третьего такта в сумматоре 7 содержится окончательный ре зультат / А /№/-1г н 12 /дт+1 - ч /-|-/- т m m В.у ДТ Е, m на точность которого ошибка дискрет ности формирования промежуточного р зультата влияет,как и в прототипе, с весом Р, / P/rti. Таким- образом, в данном устройст ве, благодаря использованию одного того же интегратора во всех тактах рабочего цикла, автоматически выпол няется условие его работоспособнос ти (условие сходимости). Это выгод но отличает предлагаемое устройств от известного, так как позволяет исключить дополнительные такты авто подстройки параметра и, следователь но, повысить быстродействие множительно-делительного устройства. Экoнo ФIчecкий эффект от использования изобретения обусловлен указанными техническими особенностями устройства. Формула изобретения Множительно-делительное устройст во, содержащее преобразователь первой переменной во временной интерва последовательно соединенные первый ключ, интегратор и блок запоминания второй и третий ключи, сумматор и распределитель тактовых импульсов, вход преобразователя первой перемен ной во временной интервал является nepBoLM входом устройства, информационный вход первого ключа является входом устройства, а управляющий вх подключен к выходу преобразователя первой переменной во временной интервал, информационный вход второго ключа является третьим входом устройства, а выход второго ключа подключен к .входу интегратора и к выходу третьего ключа, выход блока запоминания подключен к информационному входу третьего ключа, выход сумматора является выходом устройства, первый, второй, третий и четвертый выходы распределителя тактовых импульсов подключены соответственно к управляющим входам преобразователя первой переменной во временной интервал, третьего ключа/ блока запоминания и сумматора, о т личающееся тем, что, с целью повышения его быстродействия, в. него введены последовательно включенные нуль-орган и формирователь временных интервалов, преобразователь выходной переменной во временной интервал и мультиплексор, вход нульоргана подключен к выходу интегратора, а выход подключен к информационному входу формирователя временных интервалов, выход которого подключен к информационному входу cyvwaTOpa и к первому информационному входу мультиплексора, информационный вход преобразователя выходной переменной во временной интервал подключен к выходу сумг 1атора, а выход - ко второму информационному входу мультиплексора, выход которого подключен к управлякйцему входу второго ключа, управляющие входы мультиплексора, формирователя временных интервалов и преобразователя выходной переменной во временной интервал подключены соответственно к пятому, шестому и седьмому выходам распределителя тактовых импульсов. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 772411, кл. G 06 G 7/161, 1978. 2.Авторское свидетельство СССР по заявке № 2807660,кл.С 06 G 7/161 1979,

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительно-делительное устройство | 1982 |

|

SU1088016A1 |

| Время-импульсное устройство дляуМНОжЕНия | 1979 |

|

SU847329A1 |

| Время-импульсное множительное устройство | 1982 |

|

SU1048489A1 |

| Масштабный преобразователь напряжения и его варианты | 1980 |

|

SU922780A1 |

| Время-импульсное устройство для умножения | 1977 |

|

SU744625A1 |

| Устройство управления | 1984 |

|

SU1229721A1 |

| Измерительный преобразователь напряжения | 1981 |

|

SU1075083A1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Генератор случайного напряжения | 1984 |

|

SU1241238A1 |

Авторы

Даты

1982-06-07—Публикация

1980-11-26—Подача